- •Введение

- •Тема 1. Базовая структура микроконтроллерной (мк) системы управления

- •Тема 2. Модель мк

- •Режимы обмена информацией

- •Тема 3. Структура базового мк

- •Тема 4. Организация и функционирование базового цпу

- •Устройство управления и синхронизации

- •Тема 5. Языки программирования контроллера

- •Основные группы команд контроллера

- •Тема 6. Реализация логических функций микроконтроллера

- •Этапы реализации логических функций

- •Реализация логических функций ( вариант 2)

- •Тема 7. Управление параметром в заданных пределах

- •Алгоритм управления температурой

- •Тема 8. Формирование временных интервалов таймером

- •Тема 9. Обработка прерываний в контроллере

- •Настройка контроллеров прерывания

- •Тема 10. Последовательный интерфейс в мк

- •Упрощенная структура модуля типа uart

- •Тема 11. Организация параллельного интерфейса

- •Основные характеристики адаптера

- •Структурная схема параллельного периферийного адаптера

- •Программирование адаптера

- •Тема 12 Аналого-цифровые и цифро-аналоговые преобразователи

- •Тема 12 .Этапы разработки программного обеспечения в симуляторе adsim812

- •4. Описание симулятора adSim812

Этапы реализации логических функций

Пример: У= Х1 ^ Х2 V/ Х3.

-

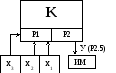

Разработка структурной схемы подключения вх. и вых. сигналов к контроллеру для заданной функции :

ИМ – исполнительный механизм, входные сигналы х1,х2,х3 подключены к порту Р1 (0,1,2 выводы соответственно).

-

Построение таблицы истинности для логических функций;

-

Разработка алгоритма реализации;

-

Разработка программы;

-

Трансляция программы для формирования исполняемого объектного кода.

Пусть Log.asm - имя файла логической функции( создан в редакторе блокнот);

ASM51.exe Log.asm - трансляция, (программа–транслятор АSM51.exe)

В результате трансляции получаем два файла:

|

Log.HEX (16-ричный код программы) .

|

Log.LST Файл листинга (указаны синтаксические ошибки) |

Загрузка .HEX файла в симулятор и отладка программы;

-

Оценка результатов:

-

быстродействие;

-

объем программы в байтах;

-

распределение адресного пространства памяти данных и команд.

Реализация логической функции с использованием команд условных переходов для функции: У= Х1 ^ Х2 V/ Х3

1.Создание структурной схемы ( см. выше);

2. Построение таблицы истинности; Внимание: входные сигналы Х необходимо размещать в таблице истинности в соответствии с подключением к входному порту контроллера (таблицу истинности заполнить самостоятельно).

|

Х3 |

Х2 |

Х1 |

У |

|

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

3. Разработка алгоритма реализации функции.

Программа функции У= Х1 ^ Х2 V/ Х3

$Mod812

M4: CLR P2.5 ;у=0

JNB P1.0, M1 ;проверка х1

JNB P1.1, M1

M2: SETB P2.5 ; y =1

JMP M4

M1: JNB P1.2, M2

JMP M4

END

Реализация логических функций ( вариант 2)

Второй вариант предусматривает вначале формирование значений всевозможных наборов входных сигналов хранящихся в виде массива данных в резидентной памяти данных контроллера. Значения функций также формируются в отдельном массиве этой же памяти данных. Таким образом, во внутренней памяти данных контроллера необходимо выделить буфер наборов входных сигналов х1,х2,….хn и буфер выходных сигналов y. Автоматическое построение таблицы истинности выполняется самим контроллером. Пусть в некоторой области памяти данных , например с ячейки 20H , формируется таблица истинности, а с ячкйки 30 формируются значения вычисляемой функции У.

Память данных:

Память данных в симуляторе

|

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

0 |

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

2 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

3 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

Комбинации входных сигналов (Х3,Х2,Х1) хранятся, начиная с 20 ячейки РПД;

Выходные сигналы У формируются в РПД, начиная с 30 ячейки.

Пример: у = х1 х2 V /х3

R0 – регистр адреса памяти данных (входные Х), R0 = 20H

R1 - регистр адреса памяти данных (выходных Y), R1 = 30H

R2 – Cч. количества комбинаций переменных Х, R2 = 08H

;Программа

$Mod812

; начальная установка регистров

START: MOV R0, #20H

MOV R2, #08H

; формирование массива таблицы истинности

CLR A

M1: MOV @R0, A

INC A

INC R0

DJNZ R2, M1

; установка регистров

MOV R0, #20H

MOV R1, #30H

MOV R2, #08H

M5: MOV A, @R0 ; Ввод {X}

; вычисление функции У=Х1Х2 V /Х3

JNB acc.0, M3

JNB acc.1, M3

M2: MOV A, #01H ; y =1

JMP M4

M3: JNB acc.2, M2

MOV A, #00H ; y=0

M4: MOV @R1, A ; вывод y в память данных

; формирование адресов R0, R1

INC R0

INC R1

DJNZ R2, M5

JMP $ ; останов программы

END