- •1. Диоды.

- •Таким образом современная система обозначений позволяет по наименованию типа получить значительный объём информации о свойствах транзистора.

- •Лабораторная работа №3

- •Лабораторная работа №4.

- •Таким образом современная система обозначений позволяет по наименованию типа получить значительный объём информации о свойствах транзистора.

- •Лабораторная работа.

- •Лабораторная работа

- •Генератор

- •Свойства не инвертирующего усилителя.

- •Лабораторная работа

- •Лабораторная работа

- •В микросхемах ттл основным технологическим элементом является элемент и –не.

- •Лабораторная работа

- •Лабораторная работа

- •Лабораторная работа

- •Лабораторная работа

- •Лабораторная работа

Лабораторная работа

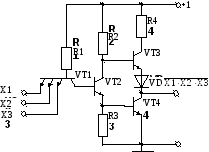

ИССЛЕДОВАНИЕ ТРАНЗИСТОРНО – ТРАНЗИСТОРНОЙ ЛОГИКИ (ТТЛ).

-

ЦЕЛЬ РАБОТЫ. Изучить работу ТТЛ, снять характеристики и рассчитать статические параметры.

-

СПРАВОЧНЫЕ ДАННЫЕ исследуемого элемента 8И – НЕ в микросхеие 158 ЛА2

-напряжение источника питания, UИ.П., В ____

-потребляемая мощность, РПОТР., мВт,____

-напряжение выходного сигнала «0», U0ВЫХ, В _____

-напряжение выходного сигнала “1”, U1ВЫХ, В ____

-входной ток при входном напряжении сигнала «0», I0ВХ., мкА ______

-входной ток при входном напряжении сигнала «1», I1ВХ., мкА ______

- время распространения среднее, tЗД.СР., нс ______

3 .

СХЕМА ИССЛЕДОВАНИЯ .

.

СХЕМА ИССЛЕДОВАНИЯ .

4. ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ.

4.1.Ознакомиться с установкой для проведения лабораторной работы и собрать схему исследования.

ОБОРУДОВАНИЕ. Для проведения лабораторной работы в установке используются: часть стенда СТ4 для исследования логических устройств, приборы измерительного блока (два вольтметра и два амперметра) и внутренний нерегулируемый источник питания +5В. В верхней части на панели стенда имеется рисунок функциональной схемы исследования ТТЛ. На панели закреплены гнёзда для подключения измерительных приборов. В цепи питания и во входной цепи одного входа Х1 закреплены гнёзда для установки вилок амперметров. В точке подключения источника питания, во входной цепи Х1 и на выходе закреплены гнёзда для подключения вольтметров. Напряжение на входе Х1 регулируется потенциометром R в пределах от нуля до + 3,5 В. Нуль соответствует логическому нулю, а напряжение +3,5 В соответствует логической единице. На входах Х2 и Х3 напряжение устанавливается переключателями S1 и S2 в положение логического нуля «0» или в положение логической единицы «1».

Перед сборкой схемы проверить напряжение питания и пределы регулировки входного напряжения. Напряжение питания должно быть в пределах от 4,7 В до 5,3 В. вставить вилки амперметров А1 в гнёзда входной цепи, а А2 в гнёзда цепи питания, штырь вольтметра V1 гнездо входной цепи, а V2 в гнездо выхода. Переключатели S1 и S2 установить в положение логической единицы.

4.2. Провести измерения для определения переключательной характеристики, и заполнить таблицу 1.

При снятии данных необходимо учитывать особенности переключательной характеристики. Особенностью является то, что характеристика изменения от напряжения логической единицы до напряжения логического нуля по выходу занимает по входу незначительный участок напряжения – не более 0,5 В. Поэтому нецелесообразно снимать характеристику классическим методом, когда разбивают входное напряжение равномерно в заданных пределах и по данным проводят измерения параметров.

В данной работе равномерное измерения проводим только на участке изменения характеристики от «1» до «0» по выходу. Для этого определяется этот участок входных напряжений. От начала резкого изменения к нулю (при изменении входного напряжения от минимального значения ) до начала резкого изменения к единице ( при изменении входного напряжения от максимального значения ). Следовательно необходимо вначале провести два измерения от нуля, и установить минимальное входное напряжение начала изменения выходного напряжения, затем два измерения от максимального значения, установив максимальное напряжение по входу конца изменения. На участке изменения выходного напряжения можно провести два – три измерения.

Особенностью схемы ТТЛ является возможность установки линейного режима, при котором ток потребления значительно превышает токи в статическом состоянии логического нуля и логической единицы. Участок входного напряжения по входу в режиме максимального тока составляет единицы милливольт.

Необходимо соблюдать очерёдность измерений:

первое измерение проводить при минимальном входном напряжении;

второе измерение проводить на участке начала изменения выходного напряжения от максимального;

третье измерение – при максимальном входном напряжении, записать результаты в последнюю графу таблицы;

четвёртое – на участке начала изменения выходного напряжения от нуля;

пятое – при максимальном токе потребления;

шестое и седьмое измерения проводить при входных напряжениях распределённых пропорционально между входными напряжениями второго и пятого измерений.

4.3. Зарисовать и зависимости выходного напряжения и тока потребления от входного напряжения.

4.4. Рассчитать параметры логического элемента. Для определения статических параметров на переключательную характеристику зарисовать обратимую характеристику.

-

ДАННЫЕ ИССЛЕДОВАНИЯ.

Таблица

-

№ изм.

1

2

6

7

5

4

3

UВХ., В

UВЫХ., В

IВХ., мА

IПОТР.,мА

7. РАСЧЁТНЫЕ ДАННЫЕ.

На переключательной характеристике построить обращённую характеристику и определить статические параметры:

напряжение логического нуля по входу U0 , В _________

напряжение логической единицы по входу U1 , В _________

напряжение логического нуля по выходу U0 , В _________ напряжение логической единицы по выходу U1 , В _________

напряжение помехи от нуля U0 ПОМ , В ______

напряжение помехи от единицы U1 ПОМ , В ______

таблица истинности:

Х1

0 1 0 1 0 1 0 1

Х1

0 1 0 1 0 1 0 1

Х2 0 0 1 1 0 0 1 1

Х3 0 0 0 0 1 1 1 1

F

Функция в коньюктивной форме F=___________________________________

8. КОНТРОЛЬНЫЕ ВОПРОСЫ.

-Почему необходимо устанавливать“1” на входах Х2 и Х3 при снятии характеристики?

-Преимущества схемы сложного инвертора.

-Почему при переключении появляется точка максимального тока потребления?

-Описание принципиальной схемы логического элемента И – НЕ со сложным инвертором.

-Принцип работы логического элемента на МЭТ.

- Какими параметрами характеризуется помехоустойчивость?

+1

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ МОП-СТРУКТУР (КМОП)

С хемы

И и ИЛИ на полевых транзисторах с

изолированным затвором (

металл-окисел-полупроводник МОП)

образуются путём последовательного

или параллельного соединения транзисторов.

В качестве нагрузки вместо сопротивления

применяют МОП-транзисторы. Благодаря

этому упрощается технология изготовления

интегральных схем (ИС) и, кроме того,

увеличивается плотность размещения,

так как МОП-транзистор занимает на

подложке меньшую площадь, чем биполярный

транзистор.

хемы

И и ИЛИ на полевых транзисторах с

изолированным затвором (

металл-окисел-полупроводник МОП)

образуются путём последовательного

или параллельного соединения транзисторов.

В качестве нагрузки вместо сопротивления

применяют МОП-транзисторы. Благодаря

этому упрощается технология изготовления

интегральных схем (ИС) и, кроме того,

увеличивается плотность размещения,

так как МОП-транзистор занимает на

подложке меньшую площадь, чем биполярный

транзистор.

На рис.1 представлены схемы инверторов на МОП транзисторах. На рис1.а в схеме используются транзисторы одной проводимости. Транзистор VT2 работает в ключевом режиме, а в качестве сопротивления нагрузки применён МОП транзистор VT1 с прямым смещением. На рис 1.б в инверторе используются транзисторы разной проводимости, включённые встречно-последовательно. Пару транзисторов разной проводимости, выполненных по единой технологии, называют комплементарными транзисторами, а логические элементы, выполненные по этой технологии, относят к элементам КМОП. Оба транзистора работают в ключевом режиме и управляются одним сигналом. Открывание одного транзистора всегда сопровождается закрыванием другого независимо от того, какая логика используется – положительная или отрицательная. Следует отметить, что запирание транзистора одного происходит раньше, чем открывание другого. Это свойство объясняет то, что элементы КМОП практически не потребляют энергии от источника питания в статическом и динамическом режимах. Расход энергии источника питания происходит во время переключения транзистора из состояния отсечки в состояние насыщения на перераспределение зарядов ёмкости затвора. Ёмкость образована между металлом, к которому подводится потенциал управления, и полупроводником, в котором образуется канал. В МОП- транзисторах эта ёмкость достаточно велика, чем объясняются в основном низкая частота переключения МОП-логики.

При применении положительной логики общая точка подключается к истоку транзистора n-проводимости, а напряжение питания положительной полярности подключается к истоку транзистора p-проводимости. А при применении отрицательной логики общая точка подключается к истоку транзистора p-проводимости, а напряжение питания отрицательной полярности подключается к истоку транзистора n-проводимости.

Д ля

выполнения операции ИЛИ транзисторы

соединяются параллельно, а их

комплементарные пары, выполняющие

функцию нагрузки, соединяются

последовательно. Для выполнения операции

И транзисторы соединяются последовательно,

а их комплементарные пары, выполняющие

функцию нагрузки, соединяются параллельно.

ля

выполнения операции ИЛИ транзисторы

соединяются параллельно, а их

комплементарные пары, выполняющие

функцию нагрузки, соединяются

последовательно. Для выполнения операции

И транзисторы соединяются последовательно,

а их комплементарные пары, выполняющие

функцию нагрузки, соединяются параллельно.

На рис. 2 представлена схема ИЛИ – НЕ для положительной логики. Количество входов может быть неограниченным, так как отсутствуют токи затворов. Количество входов ограничивается только конструктивными требованиями.

Схема элемента И представлена на рис. 3. Напряжение логического нуля можно получить только тогда, когда все транзисторы, включённые последовательно, будут в режиме насыщения. В режиме насыщения МОП транзистор имеет большое сопротивление, и при большом количестве входов маловероятно получить напряжение логического нуля. В реальных устройствах количество входов по И не превышает четырёх.

Основными элементами КМОП логики считаются элементы ИЛИ – НЕ.

Статические параметры логических элементов указывают на номинальные значения напряжений логического нуля, напряжений логической единицы по входу и выходу и помехоустойчивость логического элемента при заданных режимах эксплуатации. Статические параметры определяют по переключательным характеристикам. Координаты точек наибольшей скорости изменения характеристики принято считать предельными значениями напряжений логического нуля и логической единицы по входу и выходу. Точка наибольшей скорости устанавливается по точке касания линии, проведённой под углом 45 градусов к осям координат. Номинальные значения определяются по техническим условиям завода изготовителя по применению элемента.

На рис. 4 приводится

методика определения статических

параметров инвертирующего элемента

НЕ. На основную переключательную

характеристику накладывается обратимая

характеристика. Для того, чтобы начертить

обратимую характеристику, используют

те же значения, что и для основной

![]() ,

изменяя при этом координатные оси

,

изменяя при этом координатные оси

![]() .

На рисунке обратимая характеристика

изображена пунктиром.

.

На рисунке обратимая характеристика

изображена пунктиром.

Координаты точек пересечения характеристик А и В указывают статические значения номинальных напряжений логического нуля и логической единицы по входу U0 , U1 и выходу U0 , U1. Точка D определяет предельное максимальное напряжение логического нуля по входу и предельное минимальное напряжение логической единицы по выходу, а точка Е определяет предельное минимальное напряжение логической единицы по входу и предельное максимальное напряжение логического нуля по выходу. Точка С определяет неопределённое состояние логического элемента по выходу.

Помехоустойчивость – это максимальное напряжение помехи на входе, которое может изменить состояние на выходе. Помехоустойчивость определяется как разность предельного и номинального напряжений по входной координате основной характеристики. Напряжение помехоустойчивости от нуля по входу – статическая помехоустойчивость по низкому уровню Uп01, определяется, как разность напряжения координаты точки D и напряжения координаты точки А. Это напряжение положительное. Напряжение помехоустойчивости от единицы по входу – статическая помехоустойчивость по высокому уровню Uп10, определяется, как разность напряжения координаты точки Е и напряжения координаты точки В. Это напряжение отрицательное.

В некоторых технических условиях на логические элементы помехоустойчивость элемента с инверсией «НЕ»112,113 определяется, как разность напряжений неопределённости в точке С и номинальных напряжений в точках А и В.