Микроконтроллер at89c2051

Основные характеристики

- Совместимость с MCS-51 - 2 Килобайта Перепрограммируемой Флеш-Памяти - Допускается: 1000 циклов записи/чтения - Диапазон напряжения питания от 2.7В до 6В - Полностатическая система: тактовая частота от 0 Гц от 24 MHz - Двух-уровневая блокировка памяти программ - 128 x 8-разрядная внутреннее ОЗУ - 15 программируемых линий ввода/вывода - Два 16-разрядных Таймера/счетчика - Шесть источников прерывания - Программируемый последовательный UART Канал - Прямое подключение светодиодного дисплея - Встроенный аналоговый компаратор - Малая мощность пассивного режима и режим пониженной мощности

ОписаниеAT89C2051 - низковольтная, быстродействующая CMOS 8-разрядная микроЭВМ с 2 Кб электрически стираемой флеш ПЗУ (PEROM). Устройство изготовлено, с использованием технологии энергонезависимой памяти высокой плотности фирмы Atmel и совместимо с промышленным стандартом MCS-51 по системе команд и назначению контактов. Соединение универсального 8-разрядного процессора с флеш-памятью на одном кристалле, делает Atmel AT89C2051 мощной микроЭВМ, которая обеспечивает гибкое и недорогое решение многих прикладных задач управления. AT89C2051 обеспечивает следующие стандартные возможности: 2 Кб флеш памяти, 128 байтов ОЗУ, 15 линий ввода/вывода, два 16-разрядных таймера/делителя, пяти векторная, двух уровневая система прерываний, полно/дуплексный последовательный порт, прецизионный аналоговый компаратор, встроенный осцилятор и тактовый генератор. Кроме того в микросхеме AT89C2051 применяется технология со статической логикой корректно работающая при снижении частоты тактового генератора вплоть до нулевого значения и поддерживает два программновыбираемых режима экономии мощности. Неактивный Режим приостанавливает работу ЦП. При этом выход из режима малого потребления может происходить при запросах то ОЗУ, таймера/делителя, последовательного порта или системы прерывания. При принудительном переходе в режим пониженного потребления мощности сохраняется содержимое ОЗУ, но внутренний генератор микросхемы, останавливается, отключая все другие функции чипа до последующего аппаратного сброса.

Описание

выводовPDIP/SONIC

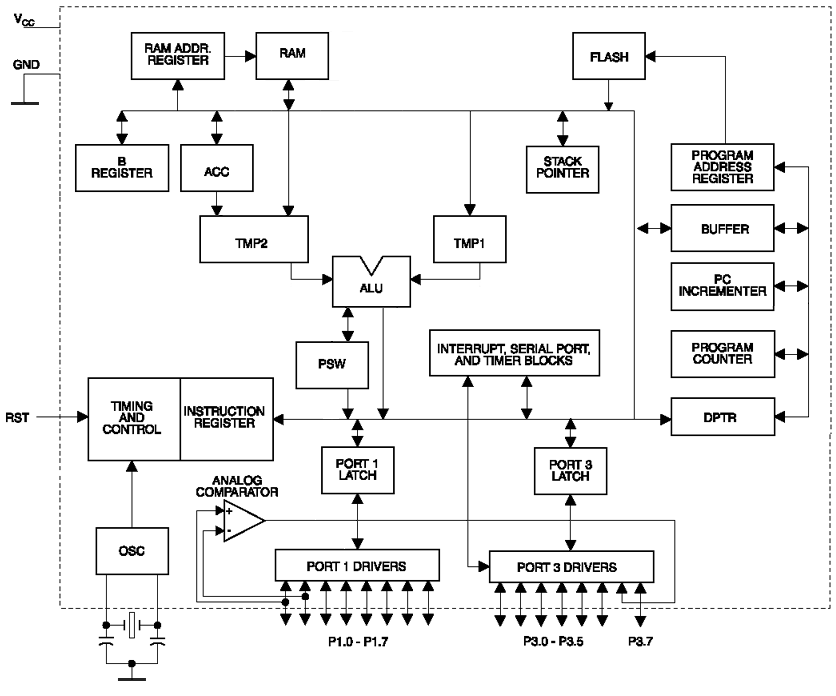

Блок - схема внутреннего устройства контроллера

Назначение выводов------------------VCC Напряжение Питания.GND Общий провод.Порт P1 8-разрядный двунаправленный порт ввода/вывода. Порт со держит линии P1.2 к P1.7, имеющие внутренние нагрузочные резисторы. P1.0 и P1.1 требуют внешней нагрузки. P1.0 и P1.1 также являются положительным (AIN0) и отрицательным (AIN1) входами встроенного аналогового компаратора. Все выводы ПортаP1содержат буферы вывода, которые могут выдерживать нагрузку до 20 mA и могут непосредственно управлять светодиодными дисплеями. Когда на какой-либо выход Порта P1 подана логическая 1,они могут использоваться как входы. Когда выводы P1.2 к P1.7 используются как входы и извне на них подан сигнал низкого уровня, из них будет вытекать ток от источника (IIL) благодаря внутренним нагрузочным резисторам. Порт P1 также получает данные кода в процессе программирования и проверки ПЗУ программ.

Порт P3Порт P3 имеет семь двунаправленных линий ввода/вывода со внутренней нагрузкой (P3.0 - P3.5, P3.7). Линия P3.6 постоянно подсоединена к выходу встроенного компаратора и не выходит на внешние выводы, как остальные линии ввода/вывода. Буферы Порта 3 могут нагружаться сигналом до 20 mA. Когда на любую из линий Порта 3 подан сигнал логической единицы, напряжение на этих выводах будет высоким (благодаря внутренним нагрузочным резисторам) при этом они могут использоваться как вводы. Если внешним сигналом вывод Порта 3 будут переведены в низкий уровень, из линии порта будет вытекать ток источника (IIL) благодаря внутреннему сопротивлению нагрузки. Порт P3 также обслуживает функции дополнительных устройств AT89C2051 как перечислено ниже:Альтернативные функции выводов порта P3P3.0- RXD (вход последовательного порта)P3.1- TXD (выход последовательного порта)P3.2- INT0 (внешнее прерывание)P3.3- INT1 (внешнее прерывание)P3.4- T0 (таймер 0 внешний ввод)P3.5- T1 (таймер 1 внешний ввод) Порт P3 также получает некоторые сигналы управления при программировании и проверке ПЗУ программ.

RST Вход сброса. На всех вывода ввода/вывода устанавливается сигнал логической 1, как только RST перейдет в состояние логической 1. Высокий логический уровень на входе RST должен удерживаться в течении двух машинных циклов для надежного сброса устройства. Каждый машинный цикл берет 12 тактов генератора или циклов часов.

XTAL1 Вход инвертирующего усилителя тактового генератора и вход внешнего тактового сигнала.

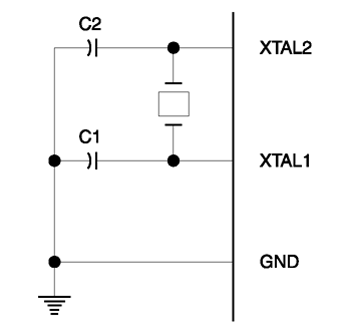

XTAL2 Выход инвертирующего усилителя генератора.Характеристики ГенератораXTAL1иXTAL2- вход и выход, соответственно, инвертирующего усилителя, который может быть настроен для использования как внутренний генератор, как показано в Рисунке 1. Может использоваться кварцевый или керамический резонатор. Чтобы управлять устройством от внешнего источника колебаний, выводXTAL2должен быть оставлен свободным, а наXTAL1подается управляющий сигнал, как показано в Рисунке 2. Нет никаких жестких ограничений к частоте внешнего тактового сигнала, так как к внутренней схеме синхронизации осуществляется через встроенный делитель на два, но требования к уровням напряжения высокого и низкого уровней должны соблюдаться.

Рисунок 1. Подключение кварцевого кристалла.

Примечания: C1, C2 = 30 pF +/- 10 pF для Кварцевых Резонаторов = 40 pF +/- 10 pF для Керамических Резонаторов

Рисунок 2.Подключение внешнего тактового сигнала.

Регистры Специальных Функций

Вся область внутренней памяти на микросхемы называется Регистры Специальных Функций (Special Function Register - SFR) назначение которых показано в таблице 1 см. ниже.

Таблица 1. Карта SFR микросхемы 89C2051 и их значения после сброса.

Обратите внимание, что не все адреса заняты, при этом не занятые ячейки отсутствуют на кристалле. При чтении по этим адресам будут в общем возвращаться, случайные данные, и запись будет иметь неопределенный эффект. Пользовательская программа не должна записывать 1 в эти ячейки, так как они могут использоваться в будущих модификациях микросхемы, для реализации новых возможностей. В этом случае, сброс или неактивные значения новых битов будет всегда 0.

Ограничения на некоторые Команды

AT89C2051это экономичный и недорогой представитель большого семейства микроконтроллеров фирмы Атмел. Он содержит 2 Килобайта памяти программ. Микроконтроллер полностью совместим с архитектурой MCS- 51, и может быть запрограммирован, используя систему команд MCS-51. Однако, имеются несколько соображений, которые нужно иметь в виду при использовании некоторых команд в программе для этого устройства. Все команды, связанные с переходом к подпрограмме или безусловным переходом должны быть ограничены так, чтобы они адресовали ячейку в пределах физического пространства памяти программ устройства, которое ограничено 2КБ для AT89C2051. За это несет ответственность разработчик программного обеспечения. Например, команда LJMP 7E0H была бы допустима для AT89C2051 (с 2КБ памяти), но LJMP 900H будет не допустимо.

1. Команды Перехода:

LCALL, LJMP, ACALL, AJMP, SJMP, JMP @A+DPTRЭти команды безусловного перехода выполняются правильно, пока программист имеет в виду, что адрес ячейки, к которой происходит переход, должен оставаться в пределах физических границ размера памяти программы (00H - 7FFH для процессора 89C2051). Нарушение физических пределов адресов может вызвать непредсказуемое поведение программы.

CJNE [...], DJNZ [...], JB, JNB, JC, JNC, JBC, JZ, JNZС этими командами условного перехода то же самое правило, что и для команд безусловного перехода. Здесь также, нарушение границы памяти может привести к ошибочному выполнению программы. Для прикладных программ, включающих прерывания нормальное прерывание обслуживается стандартные адреса используемые в архитектуре семейства 80C51, сохранились.