Лабораторная работа №2

Тема: исследование транзистора, включенного по схеме с общим эмиттером.

Цель: научить измерять характеристики биполярного транзистора и делать выводы из полученных результатов.

Оборудование: : ПЭВМ, программный пакет «Electronics Workbench»

1 Краткие теоретические сведения

В числе электропреобразовательных полупроводниковых приборов, т. е. приборов, служащих для преобразования электрических величин, важное место занимают транзисторы. Они представляют собой полупроводниковые приборы, пригодные для усиления мощности и имеющие три вывода или больше. В транзисторах может быть разное число переходов между областями с различной электропроводностью. Наиболее распространены транзисторы с двумя n–р- переходами, называемые биполярными, так как их работа основана на использовании носителей заряда обоих знаков. В настоящее время изготовляются и применяются исключительно плоскостные транзисторы. Устройство плоскостного биполярного транзистора показано схематически на рисунке 1.

Рисунок 1 – Принцип устройства плоскостного транзистора

Применяют три основные схемы включения транзисторов в усилительные или иные каскады. В этих схемах один из электродов транзистора является общей точкой входа и выхода каскада. Основные схемы включения транзисторов называются соответственно схемами с общим эмиттером (ОЭ), общей базой (ОБ) и общим коллектором (ОК).

Схема с общим эмиттером показана на рисунке 2. Входное напряжение Uвх, которое необходимо усилить, подается от источника колебаний на участок база – эмиттер.

Зависимости между токами и напряжениями в транзисторах выражаются статическими характеристиками транзисторов, снятыми при постоянном токе и отсутствии нагрузки в выходной цепи. В транзисторах взаимно связаны всегда четыре величины: I1, I2, U1, U2 – входные (индекс 1) и выходные (индекс 2) токи и напряжения.

Рисунок 2 – Схема включения транзистора в усилительный каскад

(схема с общим эмиттером)

Одним семейством характеристик эту зависимость показать нельзя. Необходимо два семейства. Наиболее удобно рассматривать семейство входных характеристик I1 = f(U1) вместе с семейством выходных характеристик I2 = f(U2). Входные и выходные характеристики транзистора аналогичны характеристикам полупроводникового диода.

На рисунке 3 показаны входные характеристики транзистора, включенного по схеме ОЭ т.е. Iб = f(Uбэ) при постоянных выходных напряжениях (Uкэ = const). Характеристика при Uкэ = 0 идет из начала координат, так как, все напряжения равны нулю и нет никакого тока.

Рисунок 3 – Входные характеристики транзистора при включении его по

схеме ОЭ

Семейство выходных характеристик т.е. Iк = f(Uкэ) показано на рисунке 4. Как правило, эти характеристики снимаются при различных постоянных токах базы. Первая характеристика при Iб = 0 выходит из начала координат и весьма напоминает обычную характеристику для обратного тока полупроводникового диода. Условие Iб = 0 соответствует разомкнутой цепи базы. При этом через весь транзистор от эмиттера к коллектору проходит сквозной ток Iкэ0 (рисунок 4).

Если Iб > 0, то выходная характеристика расположена выше, чем при Iб = 0, и тем выше, чем больше ток Iб. Выходные характеристики показывают, что при увеличении Uкэ от нуля до небольших значений (десятые доли вольта) ток коллектора резко возрастает, а при дальнейшем увеличении Uкэ характеристики идут

Рисунок 4 – Выходные характеристики транзистора при включении его

по схеме ОЭ

с небольшим подъемом, что означает сравнительно малое влияние напряжения Uкэ на ток коллектора. При увеличении напряжения Uкэ увеличивается и та его часть, которая приложена в виде прямого напряжения к эмиттерному переходу. В результате этого также возрастают токи Iэ и Iк.

Хотя для расчета схем с транзисторами достаточно иметь входные и выходные характеристики, иногда пользуются еще характеристиками управления т.е. зависимостью Iк = f(Iб) при Uкэ = const (рисунок 5, а) и Iк = f(Uбэ) при Uкэ = const (рисунок 5, б). Эти характеристики наглядно показывают, что между токами Iк и Iб существует зависимость, близкая к линейной, а зависимость Iк от входного напряжения нелинейна.

Рисунок 5 - Характеристики управления (сквозные) при включении

транзистора по схеме с ОЭ

Понятно, что схема включения транзистора типа p – n – p будет отличаться от показанной на рисунке 2 обратной полярностью источников питания Е1 и Е2.

Характеристики такого транзистора являются зеркальным отображением относительно оси ординат характеристик, изображенных на рисунках 3,4,5.

Статический коэффициент передачи постоянного тока базы βстат определяется как отношение тока коллектора Iк к току базы Iб:

![]() .

(1)

.

(1)

Коэффициент передачи переменного тока базы βдиф определяется отношением приращения ΔIк коллекторного тока к вызывающему его приращению ΔIб базового тока при постоянном напряжении между коллекторам и эмиттером Uкэ (Uкэ= coust).

![]() .

(2)

.

(2)

Входное сопротивление транзистора по постоянному току (статическое) Rвх стат определяется отношением

Rвх.

стат

=

![]() ,

(3)

,

(3)

при Uкэ= coust.

Дифференциальное входное сопротивление rвх транзистора в схеме с общим эмиттером (ОЭ) определяется при фиксированном значении напряжения коллектор – эмиттер. Оно может быть найдено как отношение приращения напряжения база – эмиттер к вызванному им приращению ΔIб тока базы по методу двух точек

![]()

![]() (4)

(4)

Дифференцированное входное сопротивление rвх транзистора в схеме с ОЭ через параметры транзистора определяется следующим выражением:

rвх = rб + βдин·rэ (5)

где rб – распределенное сопротивление базовой области полупроводника,

rэ – дифференциальное сопротивление перехода база – эмиттер, опре-

деляемое из выражения: rэ= 25/ Iэ – где Iэ – постоянный ток эмиттера

в миллиамперах.

Первое слагаемое rб в выражении много меньше второго, поэтому им можно пренебречь:

rвх = βдин·rэ (6)

Выходное сопротивление транзистора по постоянному току (статическое) Rвых стат определяется из выражения

Rвых.

стат

=

![]() ,

(7)

,

(7)

при Iб = coust.

Дифференциальное выходное сопротивление транзистора (сопротивление транзистора переменному току) определяется из выражения:

Rвых.

диф

=

![]() , (8)

, (8)

при Iб = coust.

Здесь ΔUкэ, ΔIк – приращения коллекторного напряжения и коллекторного тока, соответствующие пологому участку выходной характеристики.

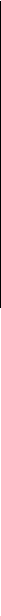

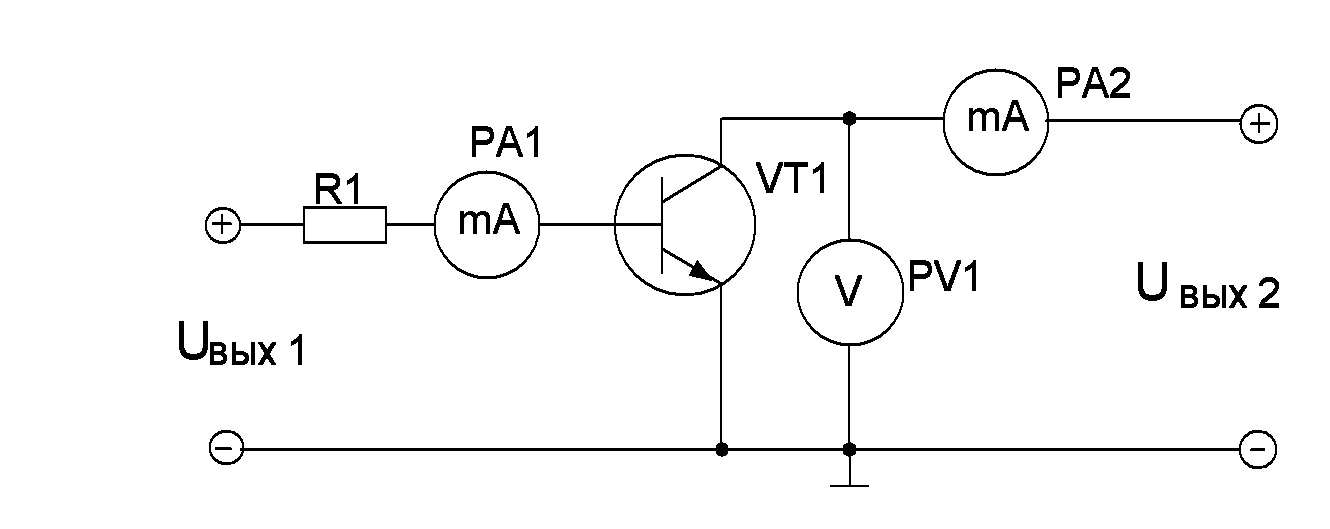

Схемы включения биполярного транзистора n – p – n типа с ОЭ (┴) для снятия статических входных и выходных характеристик показаны соответственно на рисунках 6 и 7.

Рисунок 6 - Схема включения биполярного транзистора n - p - n типа с СОЭ для снятия статических входных характеристик

Рисунок 7 - Схема включения биполярного транзистора n - p - n типа с ОЭ для снятия статических выходных характеристик транзистора