8 Автоматизированный синтез микропрограммного автомата мура

8.1 Цель работы

Ознакомление с автоматизированным синтезом управляющих автоматов на примере автомата Мура и сравнение его с каноническим структурным синтезом микропрограммных автоматов.

8.2 Методические указания по организации самостоятельной работы студентов

В курсе ПТЦА мы работаем с платой Spartan-3E Starter Kit для программирования FPGA XC3S500E-5fg320. Плата используется как макет, иллюстрирующий процессы, происходящие в схеме. Для подачи входных воздействий используются кнопки и переключатели, для наблюдения выходных сигналов – светодиоды.

Для генерации синхросигнала используется встроенный генератор с частотой 50 МГц (периодом 20 нс) (рис. 8.1). Также плата дает возможность подключать внешние генераторы частоты, на плате имеются два разъема для этих целей (рис. 8.1).

Если при реализации автомата осведомительные сигналы подавать с переключателей, а синхросигнал получать со встроенного генератора, наблюдать пошаговую работу автомата будет невозможно из-за высокого быстродействия схемы, определяемого частотой синхросигнала.

Рисунок 8.1 – Встроенный генератор синхроимпульсов и разъемы для подключения внешних генераторов

Если синхросигнал подавать с переключателя или кнопки, мы тоже не сможем наблюдать пошаговую работу автомата, поскольку кнопки и переключатель дает на вход схемы не чистый сигнал, а сигнал с дребезгом (точнее сигнал, вызываемый дребезгом механических контактов), т.е. с многократным изменением сигнала в течение короткого времени (рис. 8.2). Это многократное изменение сигнала образует множество фронтов, по которым автомат сможет переключиться не один раз.

Рисунок 8.2 – Дребезг механических переключателей

Для выхода из положения необходимо использовать стробирующий сигнал, разрешающий синхронизацию. Его нужно подавать с переключателя или кнопки, а синхросигнал подключать с генератора. Поскольку период синхросигнала значительно меньше времени нажатия кнопки или переключателя, то за одно нажатие (подачу сигнала разрешения синхронизации) или переключение автомат может перейти в t+1 состояние много раз, и мы не сможем наблюдать его пошаговую работу. Поэтому нужна схема, формирующая на выходе единичный импульс в течение одного синхротакта для разрешения синхронизации (внутренний строб). Эта схема должна также учитывать, что внешний строб сигнал, подаваемый с переключателя или кнопки, тоже имеет дребезг. Таким образом, необходима антидребезговая схема для формирования единичного импульса (внутреннего строба), подаваемого на автомат по нажатию кнопки или переключателя (внешнего строба). Ниже на рис. 8.3 представлена временная диаграмма, иллюстрирующая данную идею. Здесь AD –антидребезговая схема, En – внешний строб, EnFSM – внутренний строб.

Рисунок 8.3– Формирование внутреннего строба

Структура антидребезговой схемы и поясняющие ее работу временные диаграммы представлены на рис. 8.4. Временные диаграммы приведены с учетом задержек срабатывания элементов.

Рисунок 8.4 – Антидребезговая схема и ее временные диаграммы с учетом задержек

Период синхроимпульса должен быть больше времени дребезга. Если передний фронт синхроимпульса Clk поступит в момент дребезга, значение 0 или 1 будет сохранено в триггере в момент t1. При наличии 0 единица будет получена при следующем активном фронте синхроимпульса (t2). Поэтому сигнал S1 является беспомеховой и синхронизированной версией сигнала AD_in. Тем не менее, возможность ошибки существует, если изменение сигнала AD_in будет близко к активному фронту синхроимпульса, что приведет к нарушению времени установки и хранения. В таком случае выход триггера может начать генерировать или выдать неправильный результат. Хотя такая ситуация встречается редко, лучше исключить ее, добавив еще один триггер S2, который хранит задержанное на один такт значение входного сигнала и позволяет обнаружить его изменение. Сигнал AD_out в течение одного синхротакта равен 1, если на входе AD_in произошло изменение значения с 0 на 1. VHDL-модель антидребезговой схемы представлена в листинге 8.1.

Листинг8.1 – VHDL-модель антидребезговой схемы

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity AD is

Port (AD_in, clk: in STD_LOGIC;

AD_out: out STD_LOGIC);

end AD;

architecture AD of AD is

signal S0, S1, S2: STD_LOGIC;

begin

PR1: process (clk)

begin

if clk = '1' and clk'event then

S0 <= AD_in;

S1 <= S0;

S2 <= S1;

end if;

end process;

AD_out <=S0 and S1 and not S2; --формирование управляющего импульса;

end AD;

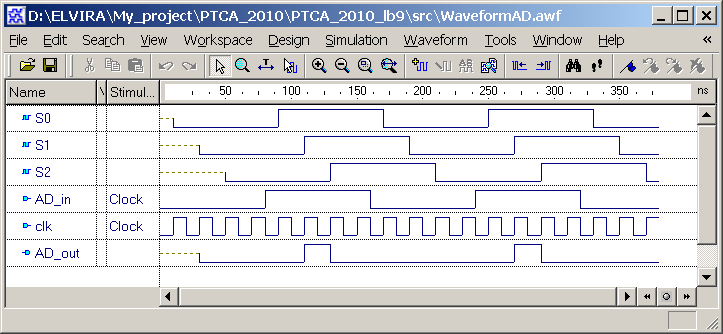

На рис. 8.5 представлен результат моделирования антидребезговой схемы

Рисунок 8.5 – Результат моделирования антидребезговой схемы

Наличия антидребезговой схемы не будет достаточно для моделирования работы автомата на макете. Это связано с тем, что период синхроимпульса гораздо короче дребезга переключателя. Поэтому необходимо увеличить период синхроимпульса (уменьшить частоту синхроимпульса) до величины, соизмеримой с длительностью дребезга.

Переключатели на плате Spartan-3E Starter Kit имеют длительность дребезга td=2 мс=2∙10-3 с. А частота синхроимпульса, генерируемая встроенным в плату генератором, составляет hclk=50 Мгц=50∙106 Гц. Период синхроимпульса определяется как 1/ hclk =1/(50∙106) = 0,02∙10-6 с=20∙10-9 с= 20 нс.

Чтобы определить во сколько раз необходимо увеличить период clk, необходимо разделить td / tclk=(2∙10-3)/( 20∙10-9)=105. Т.е. в 100000 раз или более. Для реализации увеличения периода (уменьшении частоты) clk необходимо воспользоваться делителем частоты, выполненном на счетчике (рис. 8.6).

Рисунок 8.6 – Делитель частоты на счетчике

Определим разрядность счетчика N, если коэффициент пересчета счетчика должен быть более 100000. 217=131072, 216=65536, следовательно, N=17. В таком случае, период будет равен tclk2, 62 мс, что больше td=2 мс.

VHDL-модель делителя частоты представлена в листинге 8.2.

Листинг8.2 – VHDL-модель делителя частоты

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

entity CT is

Port (R, clk: in STD_LOGIC;

CT_out: out STD_LOGIC);

end CT;

architecture CT of CT is

constant N: INTEGER := 17;

signal COUNT_INT: STD_LOGIC_VECTOR(N-1 downto 0);

begin

process (CLK, R)

begin

if R = '1' then

COUNT_INT <= (others => '0');

elsif CLK'event and CLK='1' then

COUNT_INT <= COUNT_INT + 1;

end if;

end process;

CT_out<='1' when COUNT_INT(N-1)= '1' else

'0';

end CT;

Вместо CT_out<='1' when COUNT_INT(N-1)= '1' else '0'; можно было написать CT_out<= COUNT_INT(N-1).

На рис. 8.7 представлены результаты моделирования делителя частоты для N=4 вместо N=17 для наглядности.

Рисунок 8.7 – Временные диаграммы для делителя частоты с пересчетным коэффициентом 16

Для того чтобы воспользоваться антидребезговой схемой и делителем частоты при создании проекта автомата, необходимо предусмотреть в блоке, описывающем собственно автомат еще один управляющий вход En. Рассмотрим в качестве примера автомат Мура (рис. 8.8).

Рисунок

8.8 – Граф переходов автомата Мура

Рисунок

8.8 – Граф переходов автомата Мура

VHDL-модель автомата Мура представлена в листинге 8.3. управляющий вход En описывается в блоке формирования последовательностной части. Синхронизируется автомат задним фронтом.

Листинг8.3 – VHDL-модель автомата Мура

library IEEE;

use IEEE.std_logic_1164.all;

-- Описание интерфейса устройства

entity FSM is

port ( Clk: in STD_LOGIC;

Reset, En: in STD_LOGIC;

x1, x2: in STD_LOGIC;

y1, y2, y3, y4: out STD_LOGIC);

end;

-- Описание архитектуры устройства

architecture FSM of FSM is

type State_type is (a1, a2, a3, a4, a5, a6, a7, a8, a9);

signal State, NextState: State_type;

begin

-- Блок для формирования последовательностной части

Sreg0_CurrentState: process (Clk, reset)

begin

if Reset='1' then

State <= a1;

elsif Clk'event and Clk = '0' then

if En='1' then

State <= NextState;

end if;

end if;

end process;

-- Блок для формирования комбинационной части

-- Описание переходов состояний по условиям

Sreg0_NextState: process (State, x1, x2)

begin

case State is

when a1=> if x1='1' then NextState <= a2;

else NextState <= a1;

end if;

when a2=> if x2='1' then NextState <= a3;

else NextState <= a4;

end if;

when a3=> NextState <= a4;

when a4=> NextState <= a5;

when a5=> if x1='1' then NextState <= a4;

elsif x2='1' then NextState <= a7;

else NextState <= a6;

end if;

when a6=> NextState <= a9;

when a7=> NextState <= a8;

when a8=> NextState <= a1;

when a9=> NextState <= a8;

when others => NextState <= a1;

end case;

end process;

-- Описание выходных сигналов

y1<='1' when State=a2 or State=a6 else

'0';

y2<='1' when State=a3 or State=a7 else

'0';

y3<='1' when State=a4 or State=a9 else

'0';

y4<='1' when State=a5 or State=a8 else

'0';

end;

На рис. 8.9 представлены временные диаграммы работы автомата Мура

Рисунок 8.9 – Временные диаграммы работы автомата Мура

Полностью проект автомата Мура будет выглядеть, как показано на рис. 8.10.

Рисунок 8.10 – Структурная схема для автомата Мура

Укрупненная схема для автомата Мура представлена на рис. 8.11

Рисунок 8.11 – Укрупненная схема для автомата Мура

VHDL-модель укрупненной схемы автомата Мура представлена в листинге 8.4.

Листинг8.4 – VHDL-модель укрупненной схемы автомата Мура

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity top is

port(

R : in STD_LOGIC;

CLK : in STD_LOGIC;

En : in STD_LOGIC;

x1 : in STD_LOGIC;

x2 : in STD_LOGIC;

y1 : out STD_LOGIC;

y2 : out STD_LOGIC;

y3 : out STD_LOGIC;

y4 : out STD_LOGIC

);

end top;

architecture top of top is

component CT

Port (R, clk: in STD_LOGIC;

CT_out: out STD_LOGIC);

end component;

component AD

Port (AD_in, clk: in STD_LOGIC;

AD_out: out STD_LOGIC);

end component;

component FSM

port ( Clk: in STD_LOGIC;

Reset, En: in STD_LOGIC;

x1, x2: in STD_LOGIC;

y1, y2, y3, y4: out STD_LOGIC);

end component;

signal EnFSM: STD_LOGIC;

signal ClkAD: STD_LOGIC;

begin

U1:CT

port map (R=>R, clk=>CLK, CT_out=>ClkAD );

U2:AD

port map (AD_in=>En, clk=>ClkAD, AD_out=>EnFSM );

U3:FSM

port map (Clk=>ClkAD, Reset=>R, En=>EnFSM, x1=>x1,

x2=>x2, y1=>y1, y2=>y2, y3=>y3, y4=>y4);

end top;

Состояния автомата были закодированы системой следующим образом:

Analyzing FSM <FSM_0> for best encoding.

Optimizing FSM <U3/State/FSM> on signal <State[1:4]> with gray encoding.

-------------------

State | Encoding

-------------------

a1 | 0000

a2 | 0001

a3 | 0011

a4 | 0010

a5 | 0110

a6 | 0101

a7 | 0111

a8 | 1100

a9 | 0100

-------------------