- •Глава 6

- •6.1. Принципы организации процессоров обработки

- •6.1.1. Принципы обработки сигналов в цифровых

- •6.1.2. Обобщенная архитектура dsp

- •6.2. Процессоры семейства dsp56000

- •6.2.1. Обзор архитектуры и шинной организации dsp56000 Общая характеристика

- •Структура шин

- •Арифметико-логическое устройство

- •Программный контроллер

- •Состояния процессора

- •6.2.2. Порта

- •Интерфейс порта а

- •6.2.3. Порт в Стандартный ввод/вывод

- •6.2.4. Порт с Стандартный ввод/вывод

- •6.2.5. Внутрикристальный эмулятор ОnСе

- •6.2.6. Широтно-импульсный модулятор (pwm)

- •6.2.7. Последовательный аудиоинтерфейс (sai)

6.2.6. Широтно-импульсный модулятор (pwm)

Состав PWM.

Широтно-импульсный модулятор (Pulse Width Modulator - PWM) использует два типа блоков:

блок PWMA, который является 16-битным знаковым широтно-импульсным модуля тором данных;

блок PWMB, который является 16-битным положительным дробным широтно-импульсным модулятором данных;

PWM состоит из трех блоков PWMA, двух блоков PWMB, а также связанных с ними выводов и блоков предварительного масштабирования тактового сигнала.

Характеристики PWMA:

программируемая ширина - от 9-битных до 16-битных знаковых дополненных до

двух дробных данных;

внутренний или внешний тактовые сигналы;

внутренняя или внешняя несущие частоты;

максимальный уровень тактовой частоты равен 1/2 тактового сигнала ядра DSP;

четыре вектора прерываний.

Характеристики PWMB:

программируемая ширина - от 9-битных до 16-битных знаковых дополненных до

двух дробных данных;

внутренний или внешний тактовые сигналы;

внутренняя или внешняя несущие частоты;

максимальный уровень тактовой частоты равен 1/2 тактового сигнала ядра DSP;

три вектора прерываний.

Внутренняя архитектура PWM.

PWM состоит из трех блоков PWMA и двух блоков PWMB. В семействе 560ХХ каждый блок рассматривается как периферийное устройство, занимающее одно 16-битное слово в пространстве памяти данных X и четыре дополнительных 16-битных слова (два из которых - совместно всеми блоками PWMA, а два других используются совместно всеми блоками PWMB). В семействе 560ХХ широтно-импульсный модулятор используется как обычное периферийное устройство со стандартной технологией опроса или программирования прерываний.

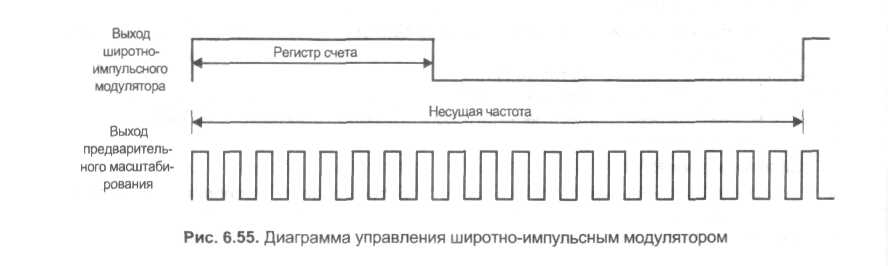

Импульсы от блоков PWMn генерируются следующим образом (рис. 6.55):

внутренний или внешний источник управляет периодом выхода PWMn, т. е. от фронта до фронта сигнала;

в регистр счета (PWACRn и PWBCRn) загружается номер, который определит ширину импульса, т. е. расстояние от фронта сигнала до его спада;

выбор источника тактового сигнала и числа, загружаемого в блок предварительного масштабирования, для определения ширины импульса.

Структура PWMA.

На рис. 6.56 показана внутренняя структура PWMA.

Регистры счета PWMA (PWMAO, PWMA1, PWMA2).

Каждый из блоков - PWMA0, PWMA1, PWMA2 состоит из следующих элементов:

16-битного регистра счета (PWACRn);

16-битного буферного регистра (PWABUFn);

15-битного счетчика (PWACNn);

компаратора;

логики управления, которая отвечает за генерацию выходных импульсов на выводах

PWM, прерываний и битов статуса.

Если в регистр счета PWMAn (PWMACRn) загружается данное из ядра процессора, поступающее через общую шину данных, то при появлении фронта сигнала несущей частоты:

данные будут передаваться в буферный регистр PWABUFn;

15-битный счетчик PWACNn начнет счет на увеличение;

будет активизирован сигнал PWAPn или сигнал PWANn (в зависимости от знака дан ных - PWABUFn(23)).

Когда компаратор определяет равенство значений PWABUFn и PWBCN, выходной сигнал (PWAPn или PWANn) переводится в неактивное состояние. На рис. 6.57 показан двигатель, управляемый выводами PWAP1 и PWBN1.

Тактовый сигнал и логика управления PWMA. Тактовый сигнал используется для инкремента счетчиков PWMAO, PWMA1, PWMA2.

Тактовый сигнал может быть:

внешним, получаемым через вывод PWACLK; в этом случае внешний тактовый сигнал является внешне синхронизируемым по внешнему тактовому сигналу и входу блока предварительного масштабирования; эта частота должна быть ниже, чем внутренний тактовый сигнал ядра 56К, деленный на 2 (CLK/2);

внутренним, получаемым от тактового сигнала ядра 560ХХ после предварительного масштабирования; максимальный уровень тактовой частоты для счетчиков равен половине тактовой частоты ядра 56К (CLK/2).

Если сигнал несущей частоты программируется как внутренний, то внутренний сигнал, который эквивалентен «фронту сигнала несущей частоты», возникает в следующих случаях:

• счетчик осуществляет циклический переход (т. е. PWACNn выполняет инкрементирование от $7FFF до 0);

• разрешается работа модуля PWMAn (WAEn = 1) после того, как бит был предварительно сброшен (WAEn = 0).

Если используется меньше чем 16 бит в дробных данных, то счетчик выполняет циклический переход в соответствии с шириной данных (т. е. если ширина данных равна 15 (т.е. 14 бит плюс знаковый бит), то счетчик выполняет циклический переход после того, как достигает значения 3FFF). «Ширина» счетчика может быть запрограммирована в диапазоне от 9 до 16 бит (т. е. счетчик может выполнить циклический переход, когда достигнет значения от $FF до $7FFF в соответствии со значением в битах WAW(2:0) в PWACSR0).

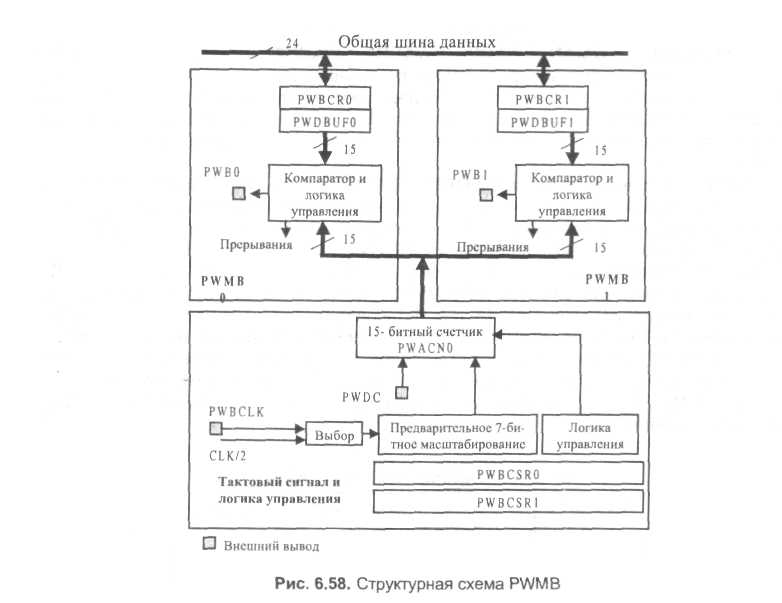

Структура PWMB.

На рис. 6.58 показана внутренняя архитектура PWMB.

Регистры счета PWMB (PWMBO, PWMB1).

Каждый из блоков - PWMBO, PWMB1 состоит из следующих элементов:

16-битного регистра счета (PWBCRn);

16-битного буферного регистра (PWBBUFn);

компаратора;

логики управления, которая отвечает за генерацию выходных импульсов на выводах

PWM, прерываний и битов статуса.

Если в регистр счета PWMBn (PWMBCRn) из процессора через общую шину данных загружается положительное дробное число, то при появлении фронта сигнала:

данные будут передаваться в буферный регистр PWBBUFn;

15-битный счетчик PWBCNn начнет счет на увеличение;

будет активизирован сигнал PWBn.

Когда компаратор определяет равенство значений PWBBUFn и PWBCN, выходной сигнал (PWBn) переводится в неактивное состояние (рис. 6.58).

Тактовый сигнал и логика управления PWMB. Тактовый сигнал, используемый для инкремента счетчиков PWMBO, PWMB1 (рис. 6.58) может быть:

• внешним, получаемым через вывод PWBCLK; в этом случае внешний тактовый сигнал является внешне синхронизируемым по внешнему тактовому сигналу и входу блока предварительного масштабирования; эта частота должна быть ниже, чем внутренний тактовый сигнал ядра 56К, деленный на 2 (CLK/2);

• внутренним, получаемым от тактового сигнала ядра 56К после предварительного масштабирования; максимальный уровень тактовой частоты для счетчиков равен поло вине тактовой частоты ядра 56К (CLK/2).

Если сигнал несущей частоты программируется как внутренний, то сигнал, который эквивалентен «фронту сигнала несущей частоты», возникает в следующих случаях:

когда счетчик осуществляет циклический переход (т. е. PWBCNn выполняет инкрементирование от $7FFF до 0);

когда разрешается работа модуля PWMBn (WBEn = 1) после того, как бит был предварительно сброшен (WBEn = 0), пока работа второго модуля PWMBk запрещена; если работа второго модуля PWMBk разрешена, то следующий сигнал «фронт сигнала не сущей частоты» произойдет когда счетчик выполнит циклический переход (т. е. когда PEBCN осуществляет инкремент от $7FFF до 0 - см. рис. 6.69).

Если используется меньше чем 16 бит в дробных данных, то счетчик выполняет циклический переход в соответствии с шириной данных. Таким образом, если ширина данных равна 15 (т. е. 14 бит плюс знаковый бит), то счетчик выполняет циклический переход после того, как достигает значения 3FFF. Разрядность счетчика может быть запрограммирована в диапазоне от 9 до 16 бит (т. е. счетчик может выполнить циклический переход, когда достигнет значения от $FF до $7FFF в соответствии со значением в битах WBW(2:0) регистра PWBCSR0). Знаковый бит 16-битных слов дробных данных в регистрах счета PWMB игнорируется, a PWMB осуществляет операции с этими данными как с положительными.

Программная модель PWM

Регистры счета PWMAN (PWACRO, PWACR1, PWACR2).

Регистры счета PWACRn (n = 0...2) являются 16-битными регистрами, доступными для чтения и записи. Данные, записанные в такой регистр, автоматически передаются в связанный с регистром буфер PWABUFn после первого перехода сигнала несущей частоты PWACn или (когда используется внутренняя несущая частота) после выполнения циклического перехода счетчика PWACNn.

Регистр управления/статуса PWMAN (PWACSRO).

PWACSR0 является 16-битным регистром, доступным для чтения и записи, и управляющим уровнями предварительного масштабирования тактового сигнала PWM, их источниками и шириной данных PWM. Биты статуса PWACSRO позволяют программисту DSP осуществлять опрос статуса PWMA.

Биты предварительного масштабирования PWMAn (WAP0-WAP2 - биты 0-2). Доступные для чтения и записи биты WAP0-WAP2 определяют значение делителя предварительного масштабирования PWMA. Эти биты определяют значение любого коэффициента в диапазоне от 2° до 27. Тактовый сигнал формируется с помощью тактового сигнала ядра 56К (CLK/2) или с помощью вывода PWACLK и делится на значение, соответствующее коэффициенту масштабирования. В табл. 6.36 показано программирование битов WAP0-WAP2. Эти биты сбрасываются (масштаб 1:1) после аппаратного ¬RESET или программного сброса.

Бит источника тактового сигнала PWMAn (WACK- бит 3). Доступный для чтения и записи бит WACK определяет источник тактового сигнала для 7-битного предварительного масштабирования тактового сигнала. Когда бит устанавливается, масштабируемый тактовый сигнал берется от внешнего тактового сигнала через вывод PWACLK. Бит сбрасывается после аппаратного или программного сброса.

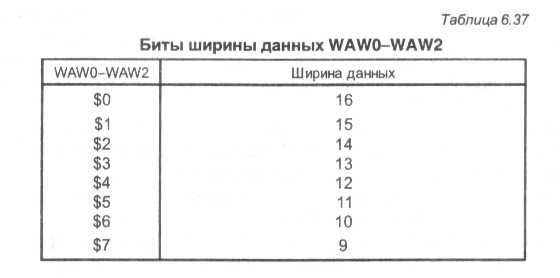

Биты ширины данных PWMAn (WAW0-WAW2- биты 4-6). Доступные для чтения и записи биты WAW0-WAW2 определяют ширину данных PWMA. Эти биты позволяют определить ширину данных от 9 до 16 бит. Представление данных остается выровненным слева,невзирая на дробное представление значение в битах WAW0-WAW2. В табл. 6.37 показано использование битов WAW0-WAW2. Эти биты сбрасываются (16-битная ширина данных) после аппаратного сброса ¬RESET или после программного сброса (команда RESET).

Резервные биты PWMAn (PWACSRO - биты 7-9). Биты PWACSRO зарезервированы и не используются. Они могут считываться и их следует записывать как нули для дальнейшей совместимости.

Биты статуса PWMAn (WAS0-WAS2 - биты 10-12). Доступный только для чтения бит WASn (n = 0+2) устанавливается, когда данные из регистра счета PWMAn (PWACRn) передаются в буферный регистр PWMAn (PWABUFn). Бит WASn очищается, когда в регистр счета PWMAn (PWACRn) заносятся новые данные. Биты устанавливаются после аппаратного сброса ¬RESET или после программного сброса (команда RESET). Пользовательская программа может протестировать биты для того, чтобы проверить загрузку регистра счета новыми данными.

Биты ошибки PWMAn (WAR0-WAR2 - биты 13-15). Доступный только для чтения бит WASn (n = 0...2) устанавливается, когда выполняется условие ошибки PWMAn, т. е. когда фронт сигнала несущей частоты появляется перед тем, как компаратор PWMAn определит равенство регистров PWACRn и PWACNn. Бит статуса WARn сбрасывается, когда работа PWMAn запрещается (WAEn сбрасывается). Бит статуса WARn сбрасывается после аппаратного или программного сброса.

Регистр управления/статуса PWMA (PWACSR1).

PWACSR1 является 16-битным регистром, доступным для чтения и записи и используемым для задания направления работы PWMA. Биты управления PWACSR1 разрешают/запрещают в блоках PWMA0, PWMA1, PWMA2:

регистры;

прерывания;

источник сигнала несущей частоты;

полярность вывода PWMA (выхода).

Биты разрешения работы PWMAn (WAEn - биты 0-2). Доступный для чтения и записи бит WAEn (n = 0+2) разрешает/запрещает работу PWMAn. Когда WAEn устанавливается, работа PWMAn разрешается. Когда WAEn сбрасывается, работа PWMAn запрещается и PWMAn переводится в собственное состояние сброса. Бит сбрасывается после аппаратного сброса -.RESET или после программного сброса (команда RESET).

Биты разрешения прерываний (WAIn - биты 3-5). Доступный для чтения v\ записи бит WAIn (n = 0-2) разрешает/запрещает прерывания PWMAn. Когда WAIn устанавливается, прерывание PWMAn генерируется после того, как данные передаются из регистра счета PWMAn (PWACRn) в буферный регистр PWMAn (PWABUFn), т.е. появления нового перехода сигнала несущей частоты. Когда WAIn сбрасывается, прерывание PWMAn запрещается. Бит сбрасывается после аппаратного или программного сбросов.

Биты выбора несущей частоты PWMAn (WACn-биты 6-8). Доступный для чтения и записи бит WACn (n = 0+2) осуществляет выбор между внутренней и внешней несущей частотой для PWMAn. Когда бит установлен, несущая частота является внутренней. Сигнал внутренней несущей частоты активизируется на каждом циклическом переходе счетчика PWACNn. Циклический переход может быть выполнен при различных значениях счета в соответствии с шириной данных, запрограммированной в битах WAW0-WAW2 PWACSR0. Отметим, что поскольку управление внутренней несущей частотой может осуществляться программно, то период сигнала PWM может контролироваться или меняться независимо от ширины импульса, управляемой через регистр счета (от фронта до спада). Когда WACn сбрасывается, несущая частота PWMAn формируется через вывод PWACn. Бит сбрасывается после аппаратного сброса ¬RESET или после программного сброса (команда RESET).

Биты полярности выходов PWACSR1 (WALn - биты 9-11). Доступный для чтения и записи бит WALn (n = 0...2) осуществляет выбор полярности выводов PWAPn PWANn. Когда бит сбрасывается, эти выводы являются активными по низкому сигналу выходами. Если бит устанавливается, выводы являются активными выходами по высокому сигналу. Бит сбрасывается после аппаратного или программного сбросов.

Резервные биты PWACSR1 (биты 12-14). Биты 12-14 PWACSR1 зарезервированы и не используются. Они читаются и их следует записывать как нули для дальнейшей совместимости.

Бит разрешения прерываний ошибки PWACSR1 (WAEIn - бит 15). Доступный для чтения и записи бит WAEIn (n = 0...2) разрешает/запрещает прерывания ошибки PWMAn. Когда WAEIn устанавливается, и возникает условие ошибки, генерируется прерывание ошибки PWMA. Когда WAEIn сбрасывается, прерывание ошибки PWMAn запрещается. Когда происходит прерывание ошибки, пользовательская программа должна протестировать все биты ошибок PWMAn (WARO, WAR1, WAR2) и биты ошибок PWMBn (WBR0, WBR1) для того, чтобы выявить, какой именно блок (PWMAn или PWMBn) сгенерировал ошибку. Бит сбрасывается после аппаратного сброса ¬RESET или после программного сброса (команда RESET).000000000000000000000000000000000000

Регистры счета PWMB (PWBCRO, RWBCR1).

Регистры счета PWBCRn (n = 0,1) являются 16-битными регистрами, доступными для чтения и записи. Данные, записанные в такой регистр, автоматически передаются в связанный с регистром буфер PWABUFn после первого перехода сигнала несущей частоты PWACn или (когда используется внутренняя несущая частота) после выполнения циклического перехода счетчика PWBCN.

Регистр управления/статуса PWMB (PWBCSRO).

PWBCSR0 является 16-битным регистром, доступным для чтения и записи, и управляющим уровнями предварительного масштабирования тактового сигнала PWMB, их источниками и шириной данных PWMB. Биты статуса PWBCSRO позволяют программисту DSP осуществлять опрос статуса PWMB.

Биты предварительного масштабирования PWMB (WBP0-WBP2 - биты 0-2). Доступные для чтения и записи биты WBP0-WBP2 определяют значение делителя предварительного масштабирования PWMB. Эти биты определяют значение коэффициента в диапазоне от 2° до 27. Тактовый сигнал формируется с помощью тактового сигнала ядра 56К (CLK/2) или с помощью вывода PWACLK и делится на значение, соответствующее коэффициенту. Выбор коэффициента масштабирования с помощью битов WBP0-WBP2 осуществляется аналогично табл. 6.36. Эти биты сбрасываются (масштаб 1:1) после аппаратного сброса ¬RESET или после программного сброса (команда RESET).

Бит источника тактового сигнала PWBCSRO (WBCK- бит 3). Доступный для чтения и записи бит WBCK определяет источник тактового сигнала для 7-битного предварительного масштабирования тактового сигнала. Когда этот бит устанавливается, масштабируемый тактовый сигнал берется от внешнего тактового сигнала через вывод PWBCLK. Этот бит (внешний тактовый сигнал) сбрасывается после аппаратного сброса ¬RESET или после программного сброса (команда RESET).

Биты ширины данных PWBCSRO (WBW0-WBW2 - биты 4-6). Доступные для чтения и записи биты WBW0-WBW2 определяют ширину данных PWMA. Эти биты позволяют определить ширину данных от 9 до 16 бит. Данные представлены выровненными слева, поскольку нежелательно дробное представление значение в битах WBW0-WBW2.

Использование битов WBW0-WBW2 аналогично использованию битов WAW0-WAW2 (см. табл. 6.37). Эти биты сбрасываются (16-битная ширина данных) после аппаратного сброса ¬RESET или после программного сброса (команда RESET).

Резервные биты PWBCSRO (биты 7-11). Биты 7-11 PWBCSR0 зарезервированы и не используются. Они читаются и их следует записывать как нули для дальнейшей совместимости.

Биты статуса PWBCSRO (WBSO- WBS2 - биты 12-13). Доступный только для чтения бит WBSn (п = 0,1) устанавливается, когда данные из регистра счета PWMBn (PWBCRn) передаются в буферный регистр PWMBn (PWBBUFn). Бит WBSn очищается, когда в регистр счета PWMBn (PWBCRn) заносятся новые данные. Эти биты устанавливаются после аппаратного сброса ¬RESET или после программного сброса (команда RESET).

Пользовательская программа может протестировать этот бит для того, чтобы проверить загрузку регистра счета PWBCRn новыми данными.

Биты ошибок PWBCSRO (WBRn - биты 14-15). Доступный только для чтения бит WBSn (n = 0,1) устанавливается, когда выполняется условие ошибки PWMBn, т. е. когда фронт сигнала несущей частоты появляется перед тем, как компаратор PWMBn определит равенство регистров PWBCRn и PWBCNn. Бит статуса WBRn сбрасывается, когда работа PWMBn запрещается (WBEn сбрасывается).

Бит статуса WBRn сбрасывается после аппаратного сброса ¬RESET или после программного сброса (команда RESET).

Регистр управления/статуса PWMB (PWBCSR1).

Это 16-битный регистр, доступный для чтения и записи и используемый для задания направления работы PWMB.

Биты управления PWBCSR1 разрешают/запрещают в PWMB:

регистры;

прерывания;

источник сигнала несущей частоты.

Биты разрешения работы PWBCSR1 (WBEn - биты 0-1). Доступный для чтения и записи бит WBEn (n = 0,1) разрешает/запрещает работу PWMBn. Когда WBEn устанавливается, работа PWMBn разрешается. Когда WBEn сбрасывается, работа PWMBn запрещается и PWMBn переводится в собственное состояние сброса. Бит сбрасывается после аппаратного сброса ¬RESET или после программного сброса (команда RESET).

Биты разрешения прерываний PWBCSR1 (WBIn - биты 2-3). Доступный для чтения и записи бит WBIn (n = 0,1) разрешает/запрещает прерывания PWMBn. Когда WBIn устанавливается, прерывание PWMBn генерируется после того, как данные передаются из регистра счета PWMBn (PWBCRn) в буферный регистр PWMBn (PWBBUFn), т. е. появления нового перехода сигнала несущей частоты. Когда WBIn сбрасывается, прерывание PWMBn запрещается. Бит сбрасывается после аппаратного сброса -.RESET или после программного сброса (команда RESET).

Резервные биты PWBCSR1 (биты 4-12). Биты 4-12 PWBCSR1 зарезервированы и не используются. Они читаются и их следует записывать как нули для дальнейшей совместимости.

Бит выбора несущей частоты PWBCSR 1 (WBC- бит 13). Доступный для чтения и записи бит WBC осуществляет выбор между внутренней и внешней несущей частотой для PWMB. Когда бит установлен, несущая частота является внутренней. Сигнал внутренней несущей частоты активизируется на каждом циклическом переходе счетчика PWBCN. Циклический переход может быть выполнен при различных значениях счета в соответствии с шириной данных, запрограммированной в битах WBW0-WBW2 PWBCSRO. Отметим, что, поскольку управление внутренней несущей частотой может осуществляться программно, то период сигнала PWM может контролироваться или меняться независимо от ширины импульса, управляемой через регистр счета (от фронта до спада). Когда WBC сбрасывается, несущая частота PWMB формируется через вывод PWBC. Бит сбрасывается после аппаратного или программного сброса.

Бит выхода с открытым коллектором PWBCSR1 (WBO - бит 14). Доступный для чтения и записи бит управления WBO конфигурирует выводы выходов PWMB (¬PWB0, ¬PWB1) как выходы с открытым коллектором или как выходы TTL-уровня. Когда бит сбрасывается, выходы конфигурируются в режим с открытым коллектором. Когда бит устанавливается, выходы конфигурируются в режим TTL-уровня. Бит сбрасывается после аппаратного или программного сброса.

Бит разрешения прерывания ошибки PWBCSR1 (WBEI- бит 15). Доступный для чтения и записи бит WBEI разрешает/запрещает прерывания ошибки PWMB. Когда WBEI устанавливается и возникает условие ошибки, генерируется прерывание ошибки PWMB. Когда WAEIn сбрасывается, прерывание ошибки PWMAn запрещается. Когда происходит прерывание ошибки, пользовательская программа должна протестировать все биты ошибки PWMAn (WARO, WAR1, WAR2) и биты ошибки PWMBn (WBRO, WBR1) для того, чтобы выявить, какой именно блок (PWMAn или PWMBn) сгенерировал ошибку. Бит сбрасывается после аппаратного сброса¬RESET или после программного сброса (команда RESET).