- •Элементы устройств вычислительный систем. Вентили, триггеры, регистры, счетчики, мультиплексоры, шифраторы, дешифраторы, сумматоры.

- •Асинхронные счетчики.

- •Синхронные счётчики.

- •Мультиплексор

- •Демультиплексор

- •Сумматор

- •4. По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на:

Асинхронные счетчики.

Простейший вид счётчика - двоичный может быть построен на основе T-триггера. T-триггер изменяет своё состояние на прямо противоположное при поступлении на его вход синхронизации импульсов. Для реализации T-триггера воспользуемся универсальным D-триггером с обратной связью, как это показано на рисунке 13.1.

Рисунок 13.1 Реализация счетного T-триггера на универсальном D-триггере.

Так как эта схема, как мы уже рассматривали ранее, при поступлении на вход импульсов меняет свое состояние на противоположное, то её можно рассматривать как счётчик, считающий до двух. Временные диаграммы сигналов на входе и выходах T-триггера приведены на рисунке 13.2.

Рисунок 13.2 Временные диаграммы сигналов на входе и выходах T-триггера.

Обычно требуется посчитать большее количество импульсов. В этом случае можно использовать выходной сигнал первого счетного триггера как входной сигнал для следующего триггера, то есть соединить триггеры последовательно. Так можно построить любой счётчик, считающий до максимального числа, кратного степени два.

Схема счётчика, позволяющего посчитать любое количество импульсов, меньшее шестнадцати, приведена на рисунке 13.3. Количество поступивших на вход импульсов можно узнать, подключившись к выходам счётчика Q0 … Q3. Это число будет представлено в двоичном коде.

Рисунок 13.3 Схема четырёхразрядного счётчика, построенного на универсальных D-триггерах.

Синхронные счётчики.

В рассмотренных схемах делителей частоты быстродействие всей схемы определяется временем распространения сигнала от входа до выхода самого старшего разряда. При этом получается, что чем больше требуемый коэффициент деления, тем больше двоичных разрядов счётчика требуется для реализации этого делителя. Тем большее время требуется для распространения сигнала от входа синхронизации счётчика, до его выхода, и тем меньше будет предельная частота, которую можно подавать на вход этого делителя.

Первая схема, которую мы рассмотрим - это схема кольцевого счётчика. Такой счётчик можно построить на основе сдвигового регистра. Схема кольцевого счётчика приведена на рисунке 13.4.

Рисунок 13.4 Схема кольцевого счетчика.

Рассмотрим работу этой схемы. Пусть первоначально в счетчике записано число 002. После первого же тактового импульса состояние счётчика станет равным 102, после второго - 112. Временные диаграммы этой схемы приведены на рисунке 13.5.

13.5 - Временные диаграммы к кольцевому счетчику.

В результате анализа временных диаграмм можно определить, что коэффициент деления схемы кольцевого счётчика будет равен: Кд = 2*n.

Для того чтобы избежать неправильной работы счётчика в этот счётчик можно ввести схему контроля правильной работы. В простейшем случае это может быть обычный логический элемент “И-НЕ”. Этот элемент будет контролировать состояние счётчика, соответствующее единицам во всех его разрядах. Схема 2-разрядного счётчика со схемой проверки правильности его работы приведена на рисунке 13.6.

Рисунок 13.6 - Схема 2-разрядного счетчика с проверкой правильности его работы.

В этой схеме триггеры счётчика при поступлении импульсов на тактовый вход последовательно заполняются единицами. Как только все триггеры будут заполнены единицами, на выходе логического элемента “2И-НЕ” появится уровень логического нуля. При поступлении следующего тактового импульса этот ноль будет записан в первый триггер счётчика. В дальнейшем работа счётчика повторяется. Временные диаграммы сигналов на выходах этого счётчика приведены на рисунке 13.7.

Рисунок 13.7 – Временные диаграммы.

Дешифратор - преобразователь кодов, выполняющий преобразование входных двоичных кодов в выходной унитарный код. Унитарный код двоичного n – разрядного числа представляется 2n разрядами, только один из разрядов которого равен 1 (или 0). Условное описание дешифратора задаётся формулой nxm (n на m), для полного дешифратора это формула nx2n. Примерами полных являются дешифраторы: 1x2, 2x4, 3x8, 4x16.

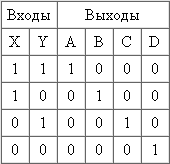

Рассмотрим пример. Составим таблицу, в которой каждому выходному сигналу сопоставляется последовательность из двух входных сигналов.

Рисунок 9.1 – Таблица истинности

На основании данной таблицы истинности составим формулу для функций A, B, C и D:

На основании полученных функций построим логическую схему. Схема должна иметь два входа и четыре выхода.

Рисунок 9.2 – Логическая схема дешифратора