- •1. Цель проектирования, задание на проектирование, состав проекта, требования к проекту

- •2. Рекомендации по проектированию узлов и блоков принципиальных электрических схем эвм

- •2.1. Разработка структурно-функциональной схемы

- •2.2. Выбор элементной базы

- •2.3. Построение принципиальной электрической схемы

- •2.3.1. Соединение логических элементов

- •2.3.2. Регистровые узлы

- •2.3.3. Счетные узлы

- •2.3.4. Узлы с дешифраторами и мультиплексорами

- •2.3.5. Суммирующие узлы

- •2.3.6. Формирование и хранение констант

- •2.4. Построение запоминающих устройств эвм

- •2.5. Некоторые распространенные схемотехнические решения

- •3. Построение временной диаграммы

- •4. Расчётная часть

- •5. Приложение

- •Литература

2.3.2. Регистровые узлы

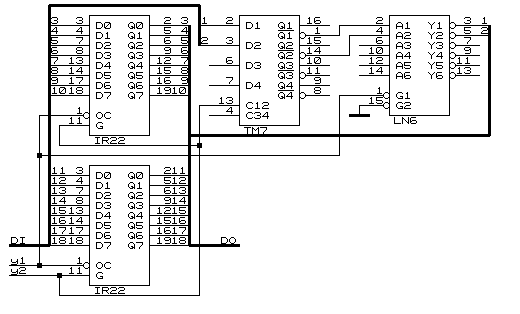

При разработке принципиальной электрической схемы специального вычислителя требуется построение нескольких регистровых узлов. Основное назначение этих регистров это - хранение и передача слова информации. Поэтому они в основном являются параллельными регистрами и, следовательно, для их реализации нужно выбирать микросхемы параллельных, в крайнем случае, универсальных регистров. Количество микросхем определяется делением количества разрядов слова информации на количество разрядов, выбранной микросхемы, полученный результат нужно округлить до ближайшего большего целого. Такой расчет приводит к тому, что количество разрядов в полученном наборе микросхем превышает разрядность слова информации, т.е. имеем недоиспользование элементной базы. Чтобы исключить это, необходимо результат деления округлять до ближайшего меньшего целого. При этом для реализации слова информации будет не хватать одного ─ двух разрядов регистра, для этого в регистр нужно добавить один ─ два триггера. Триггеры нужно выбирать таким образом, чтобы они имели такое же управление ,как и дополняемый ими регистр. На рис.4 приведен пример построения восемнадцатиразрядного параллельного регистра с третьим стабильным состоянием выхода. В качестве основы для построения выбрана микросхема регистра 555ИР22 ─ восьмиразрядный параллельный регистр с трехстабильным выходом ( в количестве 2 шт). Для хранения восемнадцатиразрядного слова информации не хватает двух разрядов.

Чтобы получить восемнадцать разрядов, выбираем микросхему 555ТМ7 (в корпусе четыре D-триггера с объединением по два для управления). Управление записью и хранением у микросхем 555ИР22 и 555ТМ7 одинаково. Однако микросхема 555ТМ7 имеет стандартный двухстабильный выход. С целью получения трехстабильного выхода у добавляемых двух разрядов регистра приходится устанавливать в схему устройство, имеющее третье стабильное состояние ─ микросхему 155ЛН6. Добавляемая микросхема имеет в своем составе шесть инверторов с третьим стабильным состоянием выхода. Принятое решение об использовании микросхемы 555ТМ7 целесообразно, т. к. неиспользуемые в данной схеме два триггера имеют независимое управление и могут быть применены при построении других регистров. Установка микросхемы 155ЛН6 является примером неудачного применения, т. к. из имеющихся в микросхеме шести инверторов используются только два. Оставшиеся четыре использовать очень трудно, так как все шесть имеют общее управление.

На представленной схеме имеются: шина входных данных DI, шина выходных данных DO и два управляющих сигнала y1 и y2. Сигнал y2 управляет занесением информации в регистр: при низком уровне этого сигнала регистр находится в режиме хранения и не воспринимает информацию на шине DI, при высоком уровне на выходной шине DO повторяется вся изменяющаяся информация шины DI (регистр построен на D триггерах-защелках). Запоминание информации происходит в момент перехода 1- 0 сигнала y2. Сигнал y1 управляет состоянием выхода регистра: при y1= 0 выходы регистра находятся в третьем стабильном состоянии, при y1=1 на выходах воспроизводится информация, записанная в регистре.

Рис.4. Параллельный регистр

Данная схема позволяет несколько подобных регистров подключать к одному входу (например сумматору), т. к. в момент передачи информации на сумматор выходы только одного регистра нужно сделать активными, а выходы остальных регистров нужно перевести в третье стабильное состояние соответствующими значениями управляющих сигналов.

При выполнении операций умножения и деления приходится осуществлять сдвиг одного из операндов. С этой целью широко используются сдвиговые регистры. В номенклатуре микросхем ТТЛ серий имеется большое разнообразие типов микросхем регистров. Имеются чисто сдвиговые регистры , у которых и запись и считывание осуществляются в последовательном коде. Однако, применение таких регистров ограничено. Наиболее широко применяются регистры с расширенными функциональными возможностями: параллельная запись - последовательное чтение, последовательная запись - параллельное чтение, параллельная запись - сдвиг - параллельное чтение. Если же регистр позволяет осуществлять запись и чтение как в параллельном, так и в последовательном коде, и сдвиг как влево, так и вправо, то такой регистр называется универсальным.

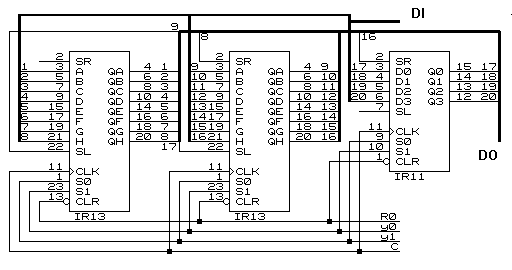

Обычно управление универсальным регистром синхронное и динамическое. На рис. 5 приведен пример построения сдвигового регистра.

Основой для построения представленного регистра выбраны микросхемы универсальных регистров 155ИР13 (2шт.) и 555ИР11, которые имеют одинаковое управление.

Рис.5. Сдвиговый регистр

Входы микросхем образуют двадцатиразрядную входную шину DI, а выходы ─ выходную шину DO. Соответствующие управляющие входы микросхем запаралеллены и образуют шину управления с сигналами: R0, y0, y1, C. Сигнал R0 предназначен для предварительной установки всех разрядов регистра в нулевое состояние. Установка в ноль происходит асинхронно, т.е. независимо от значений других управляющих сигналов. Статические сигналы y0,y1 определяют режим работы регистра. При сигналах у0=у1=0 регистр находится в режиме хранения и не воспринимает информации имеющейся на шине DI, при у0 = 1 и у1 = 0 регистр работает в режиме сдвига информации влево, при у0 = 0 и у 1=1 ─ режим сдвига информации вправо, при у0 =1 и у1=1 ─ режим параллельной записи информации в регистр. Выполнение функций в указанных режимах осуществляется только если сигнал С имеет переход 0-1. Представленный регистр может работать и только как параллельный регистр, в этом случае сигналы у0 = у1 = 1 , т.е. проводники, на которые подаются эти сигналы, должны быть соединены и через резистор 1кОм подключены к шине питания +5В. Нужно четко представлять, что данный регистр имеет стандартный двухстабильный выход, и нельзя его объединять с другими устройствами. Приведенные примеры не могут охватить всего многообразия регистровых устройств, однако они дают представление об основных схемотехнических решениях при построении регистровых узлов.