- •1. Цель проектирования, задание на проектирование, состав проекта, требования к проекту

- •2. Рекомендации по проектированию узлов и блоков принципиальных электрических схем эвм

- •2.1. Разработка структурно-функциональной схемы

- •2.2. Выбор элементной базы

- •2.3. Построение принципиальной электрической схемы

- •2.3.1. Соединение логических элементов

- •2.3.2. Регистровые узлы

- •2.3.3. Счетные узлы

- •2.3.4. Узлы с дешифраторами и мультиплексорами

- •2.3.5. Суммирующие узлы

- •2.3.6. Формирование и хранение констант

- •2.4. Построение запоминающих устройств эвм

- •2.5. Некоторые распространенные схемотехнические решения

- •3. Построение временной диаграммы

- •4. Расчётная часть

- •5. Приложение

- •Литература

2.3.5. Суммирующие узлы

Суммирующие узлы (сумматоры) являются основным арифметическим устройством , используемым при выполнении курсового проекта.

В любой серии интегральных микросхем имеются микросхемы сумматоров и арифметико-логических устройств (АЛУ), которые могут быть использованы при построении суммирующих узлов. Разнообразие микросхем сумматоров невелико и для схемотехнической реализации наилучшим образом подходят четырехразрядные микросхемы (ИМ3, ИМ6). У каждой микросхемы имеются по четыре разрядных входа операндов, вход переноса из младшего разряда, четыре разрядных выхода суммы и выход переноса в старший разряд. Выходы генерации переноса и распространения переноса у этих микросхем отсутствуют. В микросхеме между четырьмя разрядами реализован ускоренный перенос. Однако при построении многоразрядных сумматоров (8,16,32 разряда) между группами по четыре разряда возможна организация только последовательного переноса.

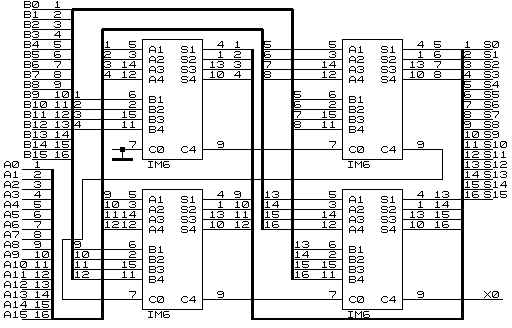

На рис. 10 показан пример построения двоичного сумматора на 14 разрядов.

Представленная схема может быть использована в качестве параллельного сумматора для выполнения операций над 14-разрядными двоичными числами с фиксированной запятой, причем 15-й разряд - знаковый, а 16-й разряд выполняет функцию анализа переполнения разрядной сетки. Перенос между интегральными микросхемами осуществляется последовательно.

Для получения высокого быстродействия необходима организация сквозного переноса. Это возможно при использовании в качестве сумматоров микросхем АЛУ (155ИП3) и ускоренного переноса (155ИП4).

Микросхема 155ИП3 имеет пять управляющих входов, сигналы которых настраивают ее на выполнение одной из 32 арифметических и логических операций над двумя четырехразрядными операндами. Следовательно, имеются восемь входов для операндов и один вход для переноса из младшего разряда. Выходы: четыре функциональных (результат обработки операндов), переноса в старший разряд, функциональный - равенства операндов (открытый коллектор) и два выхода ускоренного переноса ( G - функция генерации переноса, P - функция распространения переноса). Таким образом, микросхема 155ИП3 позволяет строить схемы сумматоров, у которых перенос осуществляется либо последовательно между микросхемами, либо ускоренно. Во втором случае обязательно использование микросхемы 155ИП4, которая организует ускоренный перенос между микросхемами АЛУ. Один корпус 155ИП4 позволяет организовать ускоренный перенос между четырьмя микросхемами 155ИП3.

Рис.10. Комбинационный сумматор

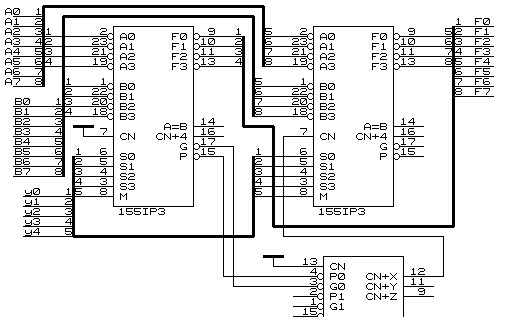

Представленная на рис. 11 схема сумматора является иллюстрацией применения микросхем АЛУ и ускоренного переноса.

Использование микросхемы 155ИП4 - ускоренного переноса позволяет построить сумматор, у которого переносы между микросхемами АЛУ будут осуществляться ускоренно. На рис. 11 у микросхемы 155ИП4 задействована только одна группа ускоренного переноса (микросхема имеет четыре таких группы) , выходы Р и G предназначены для каскадирования 155ИП4, если в сумматоре используется более четырех микросхем 155ИП3. Арифметические операции выполняются над словами, а логические операции выполняются поразрядно. Для выбора операции необходимо задавать соответствующие значения управляющим переменным y0-y4.

Рис. 11. Сумматор на микросхемах АЛУ и ускоренного переноса