Розділ 4. Схемотехніка накопичувальних схем

Тема 4.1. Тригери Елементарні поняття теорії автоматів

Цифровий автомат можна трактувати як пристрій, котрий здійснює прийом, зберігання і перетворення дискретної інформації по деякому алгоритму.

До класу автоматів з пам’яттю (АП) відносять послідовністні схеми, вузли та пристрої в яких містяться елементи пам’яті (ЕП), крім логічних елементів (ЛЕ). Наявність ЕП придає АП властивість мати деякі внутрішні стани Q, які визначаються сукупністю станів всіх елементів пам’яті. В залежності від внутрішнього стану, АП по різному реагує на один і той же вектор вхідних сигналів Х Сприймаючи вхідні сигнали Х при певному стані АП переходять в новий стан Qн і виробляє вектор вихідних сигналів Y.

Переходи АП із одного стану в інший починаються з деякого вихідного стану Q0, котрий являється частиною автомата. Наступний стан залежить від Q0 і поступивших вхідних сигналів Х. Таким чином, вся послідовність вхідних сигналів визначається послідовністю станів і вихідних сигналів. Це пояснює назву «послідовністні схеми», яка також застосовується для позначення АП.

Тригери (елементарні автомати)

Тригери – елементарні автомати, мають власні елементи пам’яті і схему управління. Усі різновиди тригерів являють собою елементарний автомат, який вміщує власний елемент пам’яті АП та схему керування (СхК), яка утворює вхідну логіку рис. 1. |

|

Рис. 1. Елементарний автомат |

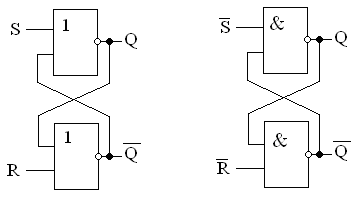

В найпростіших схемах тригерів окрема СхК може бути відсутньою, то зовнішні сигнали переносяться на всю схему тригерів. Зовнішні сигнали позначаються латинськими буквами R, S, T, C, D, J, K, як і входи тригерів. ЕП будується на двох логічних елементах, які зв’язані друг з другом так, що вихід одного з’єднаний з входом іншого. Таке з’єднання дає ланцюг з двома стійкими станами, рис 2. Для управління елементами пам’яті використовуються зовнішні установочні сигнали, на рис. 1 вони позначені через S (set) та R (reset). S – сигнал установки тригера в стан логічної одиниці (сигнал установки); R – сигнал установки тригера в стан логічного нуля (сигнал скидання). |

Рис. 2. Схема ЕП з входами управління на елементах АБО-НЕ та І-НЕ |

|

Стан тригера рахують по значенню прямого виходу, позначеного як Q.

Тригер – це запам’ятовуючий елемент з двома стійкими станами, зміна яких відбувається під дією вхідних сигналів. Як елемент комп’ютера тригер призначений для зберігання одного біта інформації, тобто 0 або 1.

Схема тригера забезпечує записування, зчитування, стирання та індикацію двійкової інформації, яка зберігається.

Практично всі серії цифрових ІС мають готові тригери, і тому задача користувача – правильне використання цих тригерів. Звідси велике значення має класифікація тригерів, вивчення їх параметрів і особливостей їх функціонування.

Класифікація тригерів

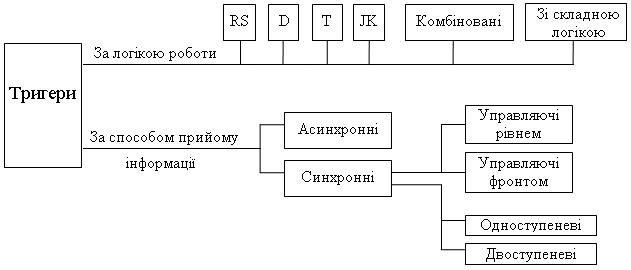

Класифікація тригерів, які використовуються в практичній схемотехніці, приведена на рис. 3.

Рис. 3. Класифікація тригерів

Класифікація тригерів відбувається за ознаками логічного функціонування та способу запису інформації.

За логічним функціонуванням розрізняють тригери типів:

RS – з роздільною установкою станів «0» і «1»;

D (Delay - затримка) – з одним інформаційним входом D;

T – тригер з лічильним входом;

JK – універсальний з роздільною установкою станів «0» і «1» та інших.

За способом запису (прийому) інформації розрізняють асинхронні та синхронні (тактові) тригери.

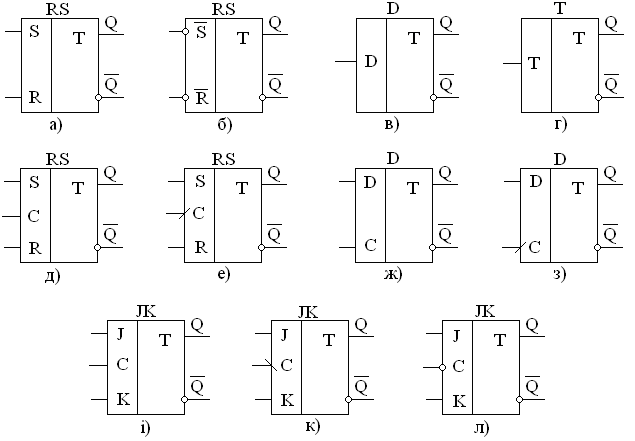

Умовно графічне позначення асинхронних та синхронних тригерів показано на рис. 4. Синхровхід позначається – С, якщо тригери не мають цього входу, то їх називають асинхронними. У таких тригерах записування інформації відбувається в будь-який момент часу при надходженні сигналів до інформаційних входів.

У синхронному тригері є С – вхід і записування інформації можливе при збігу сигналів на інформаційному і синхронному входах. Цим пояснюється вища стійкість до перешкод синхронних тригерів порівняно з асинхронними.

Рис. 4. УГП тригерів: RS, D, JK, T; а, б, в, г – асинхронні; д, е, ж, з, і, к, л – синхронні,

де д, ж, і – мають прямий статичний вхід; л – інверсний статичний вхід;

е, з – прямий динамічний; к – інверсний динамічний.

У синхронних тригерах (д, ж, і, л) з керуванням за рівнем запис інформації можливий тільки впродовж тривалості тактового сигналу (0 або 1). При керуванні фронтами у тригерах (е, з, к) дозвіл на запис інформації дається тільки в момент перепаду тактового сигналу від нуля до одиниці (динамічний прямий - вхід по фронту) або від одиниці до нуля (динамічний інверсний - вхід по спаду). В інші моменти часу тригер не реагує на вхідні інформаційні сигнали незалежно від рівня тактового імпульсу.

Розглянемо таблиці переходів тригерів, які описують логіку їх роботи. Позначимо Q – стан тригера в теперішній час, Qн – стан тригера в наступний час.

RS – тригери (тригери з окремим запуском)

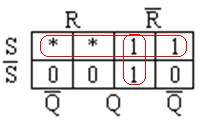

Таблиця 1

|

|

|||||||||||||||||||||||||

Таблиця

1 відповідає карті Карно. Логічне

рівняння асинхронного RS – тригера

|

Схеми асинхронних RS – тригерів з прямими та інверсними входами приведені на рис. 4а), б).

Відсутність стану при комбінації вхідних сигналів RS=11 означає, що ця комбінація заборонена.

D – тригери (тригери затримки)

Рис. 5. |

Таблиця 2

|

|

||||||

Закон

функціонування асинхронного D –

тригера здійснюється логічним виразом

Таблиця 2 дійсна і для синхронного D – тригера, тільки необхідно врахувати значення С – входу. Схема асинхронного D – тригера на елементах І-НЕ приведена на рис. 5. |

||||||||

Т – тригери (лічильний тригер)

Стан

Т – тригера змінюється на протилежний

після кожного надходження лічильного

сигналу на Т – вхід. Логіка функціонування

асинхронного лічильного тригера

подана таблицею переходів (табл.3) і

описується логічним рівнянням

|

Таблиця 3 |

||

Т |

Q |

Qн |

|

0 0 1 1 |

0 1 0 1 |

0 1 1 0 |

|

Тригери типу – JK (універсальні)

Зміна станів JK тригера наведена в табл. 4. Таблиця 4

|

Рис. 9. |

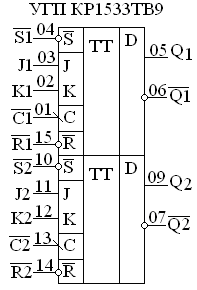

На рис. 6 показані УГП тригерів серії КР1533.

.

.

.

. .

.