- •1. Формулировка задания

- •2. Схема 4-х разрядного мультиплексора 4→1 с тристабильными выходами

- •2.1. Общие сведения по работе 4-х разрядного мультиплексора 4→1 с тристабильными выходами

- •2.2. Описание работы мультиплексора 4→1

- •2.3. Описание работы 4-х разрядного мультиплексора 4→1 с тристабильными выходами

- •2.4. Проверка работы 4-х разрядного мультиплексора 4→1 с тристабильными выходами в сапр xilinx ise 8.2i

- •3. Схема 32-разрядного синхронного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок intel) и обратно, с сигналом загрузки данных

- •3.1. Описание схемы 32-разрядного синхронного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок Intel) и обратно, с сигналом загрузки данных

- •3.2. Проверка работы схемы 32-рязрядного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок Intel) и обратно, с сигналом загрузки данных в сапр xilinx ise 8.2i

Оглавление

1. ФОРМУЛИРОВКА ЗАДАНИЯ 2

2. Схема 4-х разрядного мультиплексора 4→1 с тристабильными выходами 2

2.1. Общие сведения по работе 4-х разрядного мультиплексора 4→1 с тристабильными выходами 2

2.2. Описание работы мультиплексора 4→1 3

2.3. Описание работы 4-х разрядного мультиплексора 4→1 с тристабильными выходами 4

2.4. Проверка работы 4-х разрядного мультиплексора 4→1 с тристабильными выходами в САПР XILINX ISE 8.2i 5

3. Схема 32-разрядного синхронного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок intel) и обратно, с сигналом загрузки данных 9

3.1. Описание схемы 32-разрядного синхронного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок Intel) и обратно, с сигналом загрузки данных 9

3.2. Проверка работы схемы 32-рязрядного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок Intel) и обратно, с сигналом загрузки данных в САПР XILINX ISE 8.2i 12

ВыводЫ 18

1. Формулировка задания

Домашнее задание, Вариант № 11б:

1. Составить схемы:

- 4-х разрядного мультиплексора 4→1 с тристабильными выходами;

- 32-разрядного синхронного преобразователя порядка следования байтов в слове из сетевого в узловой (порядок Intel) и обратно, с сигналом загрузки данных.

2. Построить временные диаграммы работы устройств, перечисленных в п.1. Для построения временных диаграмм выбрать необходимое количество контрольных точек.

3. Реализовать с использованием библиотечных элементов САПР Xilinx ISE 8.2i перечисленные в п.1 схемы, представить их в виде интегрированных элементов.

4. Произвести моделирование работы элементов, полученных в п.3 и получить временные диаграммы, совпадающие с построенными в п.2.

5. Составить письменный отчет о проделанной работе по требуемой форме.

2. Схема 4-х разрядного мультиплексора 4→1 с тристабильными выходами

2.1. Общие сведения по работе 4-х разрядного мультиплексора 4→1 с тристабильными выходами

Мультиплексор – это комбинационная схема ЭВМ, имеющая один выход и несколько входов (информационных и управляющих), причём выходной сигнал формируется из сигнала на одном из входов в зависимости от комбинации сигналов на управляющих входах. Если управляющих входов n, то информационных входов 2ⁿ. Мультиплексор выполняет роль коммутатора информационных сигналов DI на один единственный выход DO.

Четырехразрядный мультиплексор 4→1 с тристабильными выходами имеет 5 входных шин, по которым поступают информационные и управляющие сигналы, и одну выходную шину; входные шины DI0,DI1,DI2,DI3 на которые поступают информационные сигналы; входная шина Adr на которые поступают управляющие сигналы; вход OE, на который поступает сигнал установки в Z-состояние; одна выходная шина DO.

Устройство работает при подаче на вход OE «0» и устанавливается в Z-состояние при подаче «1».

Для построения четырехразрядного мультиплексора 4→1 сначала был построен мультиплексор 4→1 и на его основе был построен четырехразрядный мультиплексор 4→1 с добавлением тристабильных выходов.

2.2. Описание работы мультиплексора 4→1

Для построения мультиплексора 4→1 были использованы четыре элемента «И» с тремя входами и один элемент «ИЛИ» с четырьмя входами.

В таблице 2.1. приведена таблица истинности для мультиплексора 4→1.

Таблица 2.1

Таблица истинности мультиплексора 4→1

|

A0 |

A1 |

DI0 |

DI1 |

DI2 |

DI3 |

DO |

|

0 |

0 |

DI0 |

x |

x |

x |

DI0 |

|

0 |

1 |

x |

DI1 |

x |

x |

DI1 |

|

1 |

0 |

x |

x |

DI2 |

x |

DI2 |

|

1 |

1 |

x |

x |

x |

DI3 |

DI3 |

Принципиальная схема мультиплексора 4→1 представлена на рис. 2.1.

Рис. 2.1. Схема мультиплексора 4→1

2.3. Описание работы 4-х разрядного мультиплексора 4→1 с тристабильными выходами

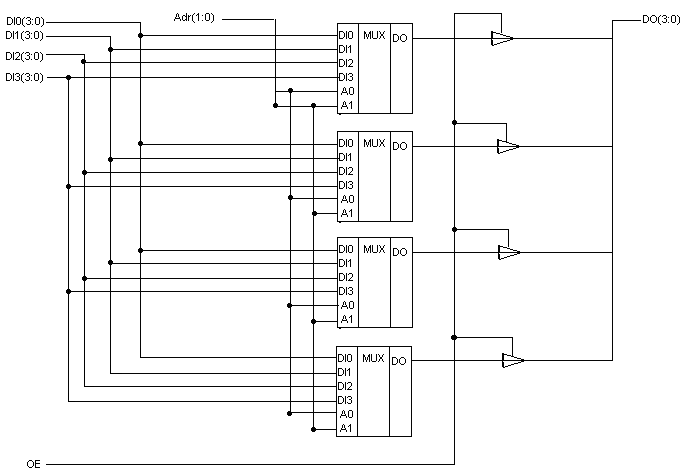

Для построения 4-х разрядного мультиплексора 4→1 с тристабильными выходами было использовано четыре мультиплексора 4→1 и четыре тристабильных элемента.

Принципиальная схема 4-х разрядного мультиплексора 4→1 с тристабильными выходами приведена на рис. 2.2.

Рис. 2.2. Схема 4-х разрядного мультиплексора 4→1