- •«Санкт-Петербургский государственный электротехнический университет «лэти» имени в.И. Ульянова (Ленина)» (спбгэту)

- •2012 Г. Оглавление

- •Техническое задание

- •Предмет проектирования

- •Общие требования к разрабатываемому процессору

- •Исходные данные для курсового проектирования

- •Средства реализации модели

- •Результаты проектирования

- •Последовательность выполнения курсового проекта

- •Общая последовательность

- •Разработка архитектуры цп

- •Уточнение структуры системы

- •Разработка архитектуры внешних выводов

- •Выбор форматов данных

- •Определение модели памяти и структуры регистровой памяти

- •Выбор форматов команд

- •Разработка системы команд

- •Внутренняя организация

- •Основные алгоритмы функционирования

- •Алгоритмы работы отдельных операций

- •Временные диаграммы

- •Руководство пользователя по использованию симулятора

Средства реализации модели

В качестве языка реализации используется С++.

Результаты проектирования

В процессе выполнения курсового проекта разрабатываются:

архитектура ЦП;

приложение (программный эмулятор).

В процессе разработки архитектуры определяются:

Форматы команд и данных.

Регистровая модель процессора (включая пользовательские и системные регистры).

Структура выводов кристалла.

Система команд (включая семантику их выполнения и установку флажков).

Обобщенный алгоритм функционирования процессора (включая алгоритмы выполнения основных команд).

Алгоритмы выполнения основных операций на шине (чтение, запись, ввод, вывод, захват шины, прерывание). Необходимо предусмотреть пакетный режим обмена между ОП и кэш-памятью.

Внутренняя организация (до структурного уровня) (включая механизмы виртуальной памяти, механизмы защиты памяти и механизмы работы с кэш-памятью).

В процессе разработки модели создаются:

UML-диаграммы, описывающие функционирование модели;

собственно приложение;

комплект документации на программную систему.

Должны быть разработаны, как минимум, следующие UML-диаграммы:

диаграммы вариантов использования (usecasediagrams);

диаграмма классов (classdiagram).

В состав документации на созданное приложение входят:

руководство оператора;

руководство системного программиста;

программа и методика испытания.

Документация оформляется в соответствии с действующими ГОСТ.

Последовательность выполнения курсового проекта

Общая последовательность

Выполнение проекта осуществляется в следующем порядке:

Разработка архитектуры ЦП.

Разработка программной модели.

Разработка документации на программный проект.

Оформление отчета.

Разработка архитектуры цп

Уточнение структуры системы

Разрабатываемый процессор предназначен для использования в качестве встроенного процессора.

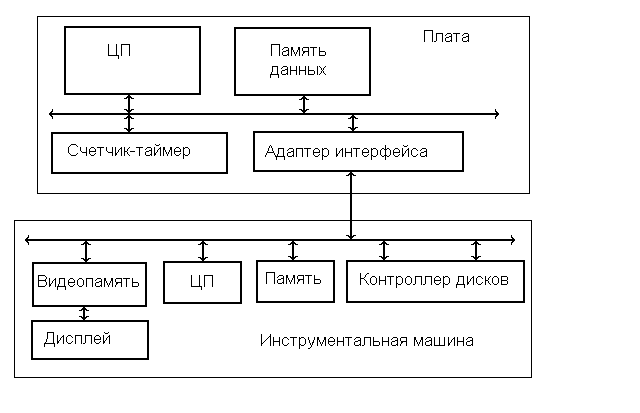

Обобщенная структура процессора, соответствующая гарвардской архитектуре, приведена на рис. 1. Она представляет собой одноплатную ЭВМ, предназначенную для встроенных применений. На плате размещаются: ЦП, память данных, счетчик-таймер, адаптер интерфейса. Кроме того, на плате могут размещаться вспомогательные схемы и интерфейсные схемы для подключения внешних устройств (на рис. 1 эти схемы не показаны).

Разрабатываемая плата не имеет собственной дисковой памяти, дисплея и клавиатур. Предполагается, что разработка и отладка программного обеспечения осуществляются на инструментальной машине с использованием кросс-систем программирования. В качестве инструментальной машины может использоваться, например рабочая станция, имеющая в своем составе дисплей, клавиатуру, дисковую память и т. п.

Основной задачей данного этапа проектирования является уточнение структуры и разрядности внутренней шины.

Рисунок 1

Разработка архитектуры внешних выводов

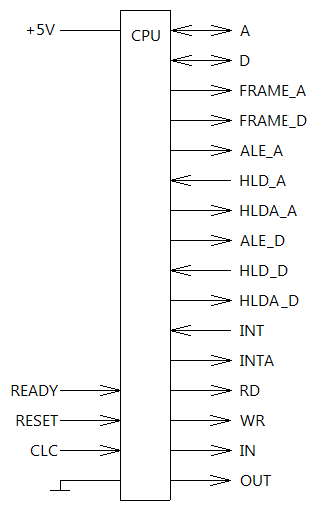

Рисунок 2

Процессор имеет раздельные шину адреса (A) и данных (D). Сигнал ALE используется для фиксации адреса на внешнем регистре-защелке, а пара сигналов HLD и HLDA – для реализации механизма захвата шины. Сигналы INT и INTA являются сигналами запроса и подтверждения прерывания. Если на корпусе имеется достаточное число свободных выво-дов, то целесообразно ввести несколько уровней запроса на прерывание.

Линии RD (Чтение), WR (Запись), IN (Ввод), OUT (Вывод), BHE (Разрешение записи старшего байта) задают выполняемую на шине операцию. Линия FRAME используется для организации режима пакетного обмена между ОЗУ и внутренними кэшами. Появление данного сигнала на шине означает начало транзакции, а снятие – указывает на то, что следующий цикл передачи данных на шине является последним.

Порты с суффиксом _Aслужат для работы с шиной адреса, а _D– с шиной данных.

Контакт READY (Готовность) служит для приема сигнала готовности от медленных внешних устройств. Назначение выводов питания, RESET и CLC (Синхронизация) очевидны.