- •«Санкт-Петербургский государственный электротехнический университет «лэти» имени в.И. Ульянова (Ленина)» (спбгэту)

- •2012 Г. Оглавление

- •Техническое задание

- •Предмет проектирования

- •Общие требования к разрабатываемому процессору

- •Исходные данные для курсового проектирования

- •Средства реализации модели

- •Результаты проектирования

- •Последовательность выполнения курсового проекта

- •Общая последовательность

- •Разработка архитектуры цп

- •Уточнение структуры системы

- •Разработка архитектуры внешних выводов

- •Выбор форматов данных

- •Определение модели памяти и структуры регистровой памяти

- •Выбор форматов команд

- •Разработка системы команд

- •Внутренняя организация

- •Основные алгоритмы функционирования

- •Алгоритмы работы отдельных операций

- •Временные диаграммы

- •Руководство пользователя по использованию симулятора

Временные диаграммы

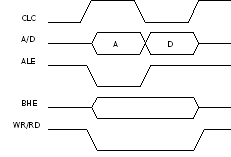

Временная диаграмма чтения и записи данных/команд в память приведена на рис. 8. По фронту CLCпроцессор выставляет сигналы ALE (сообщает, что по шине будет передаваться адрес) и BHE (помогают определить, сколько байт данных нужно передать), а также одновременно с ними сигналWR. Потом выставляет адрес. По спаду сигнала CLCпроцессор убирает сигнал ALE, сообщая памяти, что готов принять данные. Память держит данные на шине данных до тех пор, пока по следующему фронту процессор либо снова не установит сигнал ALE, либо не уберет сигналWR.

Рисунок 8. Чтение/запись.

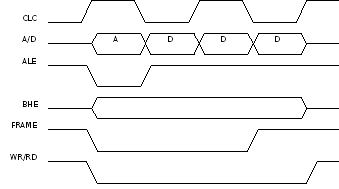

Пакетное чтение выполняется аналогичным образом с той лишь разницей, что длина обмена задаётся сигналом FRAME, который снимается за 1 такт до окончания. Адрес подаётся на шину один раз, так как читаются/записываются соседние данные.

Рисунок 9. Пакетное чтение/запись.

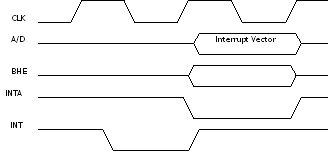

В случае появления прерывания его источник посылает процессору сигнал INTи ждёт, когда тот ответит ему сигналом готовностиINTA, после чего посылает вектор прерывания.

Рисунок 10. Прерывание.

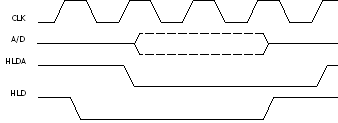

Аналогично происходит и захват шины некоторым устройством: оно посылает сигнал HLD и ждёт от процессора сигнала разрешения HLDA.

Рисунок 11. Захват шины.

Руководство пользователя по использованию симулятора

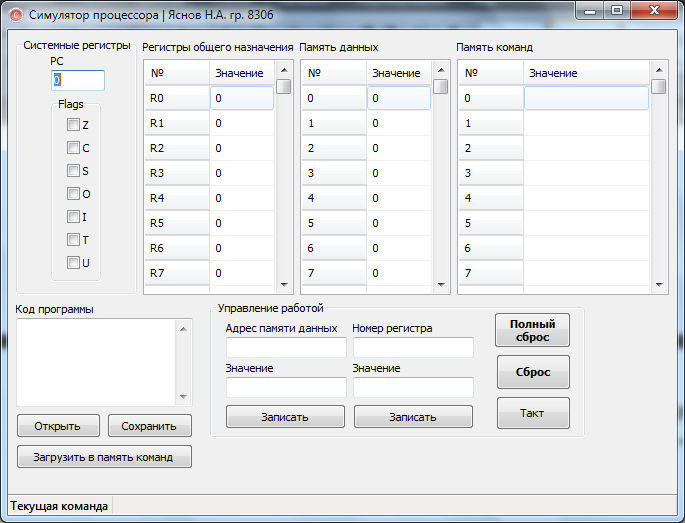

Для работы с симулятором необходимо запустить файл Simulator.exe, после чего появится главное окно программы.

В окне находятся следующие элементы управления:

Редактор флагов – в нем по ходу выполнения программы можно установить значения флагов процессора и увидеть те, которые появились в ходе выполнения операций;

Редактор программы – в нем можно загрузить, отредактировать исходный код программы, выполняемом на процессоре;

Упраление работой – здесь можно записать данные в конкретный регистр или ячейку памяти, управлять ходом работы программы;

Состояние памяти – в табличной форме отображаются все ячейки памяти данных и команд, а также регистров.

Стандартный алгоритм работы выглядит следующим образом:

Открыть файл с кодом программы или ввести её в Редакторе программы.

Нажать кнопку «Загрузить в память команд».

В зависимости от требований программы записать данные в память данных и регистры в Управлении работой.

Последовательно нажимать кнопку «Такт» до окончания работы программы.

Кнопка «Сброс» возвращает программу в начальное состояние. Кнопка «Полный сброс», кроме того, устанавливает в 0 ячейки памяти данных, регистров и флагов.

Каждое нажатие кнопки «Такт» увеличивает PCна 1.

Формат команд выглядит следующим образом:

код_операции [адрес1] [[, адрес2] [~ адрес3]]

В безадресных операциях присуствует только код_операции; адрес1 и адрес2 означает источники данных, адрес3 – конечный регистр/ячейку памяти. Если адрес3 отсутствует, запись резаультата ведётся в аккумулятор.

Формат записи адреса:

Rx– регистр под номеромx;

@x– ячейка памяти под номеромx.