- •«Санкт-Петербургский государственный электротехнический университет «лэти» имени в.И. Ульянова (Ленина)» (спбгэту)

- •2012 Г. Оглавление

- •Техническое задание

- •Предмет проектирования

- •Общие требования к разрабатываемому процессору

- •Исходные данные для курсового проектирования

- •Средства реализации модели

- •Результаты проектирования

- •Последовательность выполнения курсового проекта

- •Общая последовательность

- •Разработка архитектуры цп

- •Уточнение структуры системы

- •Разработка архитектуры внешних выводов

- •Выбор форматов данных

- •Определение модели памяти и структуры регистровой памяти

- •Выбор форматов команд

- •Разработка системы команд

- •Внутренняя организация

- •Основные алгоритмы функционирования

- •Алгоритмы работы отдельных операций

- •Временные диаграммы

- •Руководство пользователя по использованию симулятора

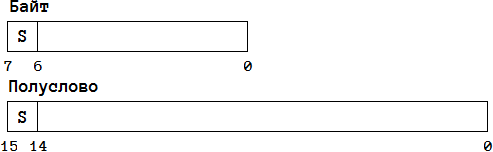

Выбор форматов данных

На рис. 3 показаны основные используемые типы данных.

Рисунок 3

Целые числа представляют собой числа со знаком или без знака. Целые числа со знаком представляются в дополнительных кодах. Целые числа без знака используются также и для представления адресов.

В задании указаны 8- и 16-битные целые типы данных, потому используются слова и полуслова.

Отрицательные числа представляются в памяти следующим образом.

7-й бит служит флагом знака (0 – положительное, 1 – отрицательное).

При представлении положительного числа в биты 6..0 записывается двоичный код числа.

При представлении отрицательного – дополнительный код (обратный код модуля числа с прибавлением единицы).

Например, число 610будет представлено как 000001102, а -610– как 111110102.

Определение модели памяти и структуры регистровой памяти

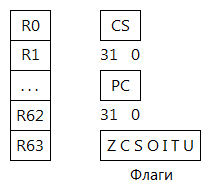

Процессор в общем случае содержит две группы регистров – пользовательские и системные. (Системные регистры доступны только при работе в режиме ядра.)

В данной работе имеются 64 16-разрядных пользовательских регистра, используемых как в качестве адресных, так и в качестве целочисленных (РОН). Кроме того, имеются управляющие регистры: CS(“codesegment”, сегмент кода; хранит адрес в ОЗУ, по которому загружен исполняемый код программы) иPC(“programcounter”, программный счётчик; хранит адрес следующей исполняемой команды).

В состав системных регистров могут входить и такие регистры:

регистр физического адреса таблицы векторов прерывания;

регистр физического адреса таблицы переадресации;

регистр для записи адреса страничной ошибки, куда записывается адрес страницы, отсутствующей в памяти.

Один из возможных вариантов организации пользовательской регистровой памяти ЦП для вариантов с использованием внешнего сопроцессора показан на рис. 4.

Рисунок 4

В структуре, приведенной на рис. 4, регистровая память включает 64 16-разрядных РОН и 32-разрядные счетчик команд, указатель на вершину стека и на адрес кодового сегмента в ОП. Регистр флажков содержит семь флажков, которые используются следующим образом:

Z – признак нулевого результата;

С – признак переноса из старшего разряда;

S – знак результата;

O – признак переполнения результата;

I – разрешение прерывания;

T – пошаговый режим;

U – режим супервизор-пользователь.

Необходимо отметить, что в RISC-процессорах аппаратный стек не используется, а адрес возврата запоминается в одном из РОН. В представленном процессоре этоR63.

В качестве аккумулятора используется регистр R0.

Выбор форматов команд

При выборе форматов следует исходить из принципов RISC-обработки, в соответствии с которыми используется минимальное число форматов команд. Наиболее желательным является использование одного формата. Была выбрана длина в 32 разряда.

Рисунок 5

На рис. 6 приведены возможные форматы команд.

Общий формат команд следующий: Код операции, Адресность, [Тип операнда, Операнд].

В случае одноадресной команды (рис. 6.1) в поле тип адресации:

00 – относительная;

01 – косвенная;

10 – прямая;

11 – регистровая.

Одноадресная команда с операндом-адресом является единственной, которая позволяет прямой доступ к ячейкам памяти.

В случае двух- и трёхадресной команд (рис 6.2 и 6.3) поле типа операнда либо не используется (работа с регистрами), либо означает тип адресации:

0 – относительная;

1 – косвенная;

в зависимости от команды.

Результат двухадресной команды записывается в аккумулятор (регистр R0). Место записи результата трёхадресной команды определяется в операнде 1.