- •«Санкт-Петербургский государственный электротехнический университет «лэти» имени в.И. Ульянова (Ленина)»

- •1.3. Исходные данные для курсового проектирования

- •Нет поддержки графики

- •2.2. Разработка архитектуры цп

- •2.2.1. Уточнение структуры системы

- •2.2.2. Архитектура внешних выводов

- •2.2.3. Выбор форматов данных

- •2.2.4. Определение модели памяти и структуры регистровой памяти

- •2.2.5. Выбор форматов команд

- •2.6. Разработка системы команд

- •2.7.Внутренняя организация

- •2.8.Основные алгоритмы функционирования

- •2.9. Основные алгоритмы функционирования

- •2.10. Алгоритмы выполнения операций на шине.

2.7.Внутренняя организация

Общая структура представлена ниже и соответствует двухступенчатому конвейеру.

Для него выделяются фаза выборки команды и фаза выполнения команды. Параллельно и асинхронно могут работать два процессора: процессор памяти и исполнительный процессор. Процессор памяти обеспечивает работу с памятью команд и памятью данных, а также с кэш-памятью. На исполнительный процессор возлагаются функции, связанные с дешифрацией и выполнением команд.

В процессоре предусмотрен одноуровневый кэш данных и кэш команд прямого отображения.

Структура кэш-памяти команд:

Размер памяти команд – 128 кб, т.е. 2^2*2^15 байт. Адрес команды – 16-разрядный. Был выбран размер страницы 2^12 (4096) байт, т.е. разделение памяти команд на 2^5 (32) страницы. Таким образом, тег состоит из пяти разрядов. Пусть размер строки кэша равен 32 байта. Для адресации по строке потребуется еще 5 бит. Таким образом, получаем количество бит под адрес строки кэша команд, равное 16 – 5 – 5 = 6. То есть, в кэше команд содержится 2^6 = 64 строки по 32 байта, и объем кэша равен 64*32 = 2048 байт.

Формат адреса принимает вид:

5 бит – тег;

6 бит – строка;

5 бит – байт.

Для памяти данных, размер которой равен 16 кб, т.е. 2*2^13 байт. Был выбран размер страницы 2^8 (256) байт, т.е. разделение памяти команд на 2^5 (32) страницы. Таким образом, тег состоит из пяти разрядов. Пусть размер строки кэша равен 32 байта. Для адресации по строке потребуется еще 5 бит. Таким образом, получаем количество бит под адрес строки кэша команд, равное 16 – 5 – 5 = 6. То есть, в кэше команд содержится 2^6 = 64 строки по 32 байта, и объем кэша равен 64*32 = 2048 байт.

Формат адреса принимает вид:

5 бит – тег;

6 бит – строка;

5 бит – байт.

.

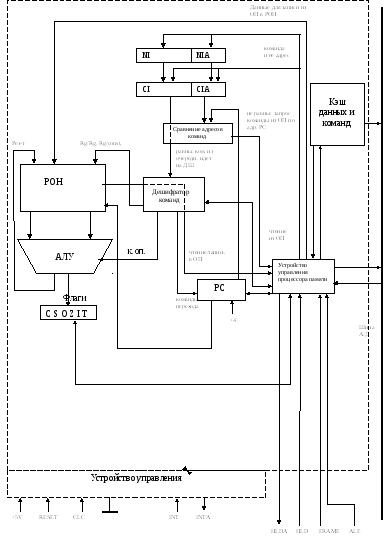

Структурно-функциональная

схема процессора:

На данной схеме присутствуют все регистры из раздела «структура регистровой памяти», а также АЛУ, дешифратор команд, кэш-память, устройства управления испольнительным процессором и процессором памяти, а также вспомогательные устройства – КУ (коммутирующее устройство) и схема сравнения адресов команд. Краткие пояснения связей даны на схеме;.

Устройство управления исполнительным процессором координирует работу всех устройств исполнительной части процессора, выставляя необходимые управляющие сигналы на входы устройств.

Устройство управления процессором памяти управляет процессами записи в память и чтения из нее. При поступлении в устройство сигналов на получение данных и команд, устройство обращается к контролеру КЭШа данных и команд. Если данные находиться там, то устройство передает их, в противном случае оно обращается к основной памяти, а контроллер КЭШа инициирует цикл замены строки. Так же это устройство имеет свои служебные регистры для образования очереди заявок.

Для организации прерываний была выделена первая страница памяти данных, в нее сохраняются все служебные регистры и рон.

В процессоре реализован двухступенчатый конвейер из двух операций: выборка команды и выполнение. Команды хранятся в очереди из двух мест. Параллельно с выполнением текущей команды происходит чтение команды из устройства управления процессором памяти и сохранение ее в последнем месте очереди. По выполнении команды очередь сдвигается и процесс повторяется.