- •«Санкт-Петербургский государственный электротехнический университет «лэти» имени в.И. Ульянова (Ленина)»

- •1.3. Исходные данные для курсового проектирования

- •Нет поддержки графики

- •2.2. Разработка архитектуры цп

- •2.2.1. Уточнение структуры системы

- •2.2.2. Архитектура внешних выводов

- •2.2.3. Выбор форматов данных

- •2.2.4. Определение модели памяти и структуры регистровой памяти

- •2.2.5. Выбор форматов команд

- •2.6. Разработка системы команд

- •2.7.Внутренняя организация

- •2.8.Основные алгоритмы функционирования

- •2.9. Основные алгоритмы функционирования

- •2.10. Алгоритмы выполнения операций на шине.

2.8.Основные алгоритмы функционирования

Общий алгоритм работы процессора представлен на схеме ниже.

2.9. Основные алгоритмы функционирования

Выполнение операции обращения к памяти на схеме ниже.

Операция чтения следующей команды из кэша команд аналогична операции чтения данных из кэша данных за тем исключением, что команда сохраняется не в РОН, как в случае с данными, а в регистре NC. В случае, когда текущая команда в регистре CI недействительна (ее адрес не совпадает с PC), из кэша данных считываются сразу две команды.

2.10. Алгоритмы выполнения операций на шине.

Ниже показана временная диаграмма на шине в случае прерывания. Источник прерывания выставляет на шину сигнал INT; процессор, выполнив необходимую подготовку (завершив последнюю команду) выставляет сигнал INTA (готовность принять прерывание); источник посылает вектор прерывания по шине.

Временная диаграмма прерывания.

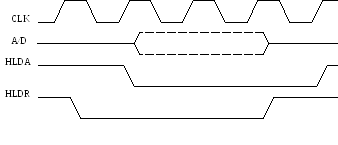

Захват шины неким устройством показан на рис. ниже. Сигнал HLDR означает желание сделать захват, HLDA, исходящий от процессора, является разрешающим (т.е. процессор завершил нужные операции и освободил шину).

Захват шины.

Запись в память данных: временная диаграмма приведена на рисунке ниже. По фронту CLK процессор выставляет сигналы ALE (сообщает, что по шине будет передаваться адрес), а также одновременно с ними сигнал WR. Потом выставляет адрес на шину адреса/данных. По спаду сигнала CLK процессор убирает сигнал ALE, сообщая памяти, что на шину будут выставлены данные. Процессор держит данные на шине данных до тех пор, пока по следующему фронту либо снова не установится сигнал ALE, либо не уберется сигнал WR.

CLC ALE A/D WR A D

Временная диаграмма записи в память

Пакетное чтение выполняется схожим образом; см. рис. ниже. Разница в том, что выставляется сигнал RD вместо WR, а также сигнал FRAME, который снимается за 1 такт до конца пакетного обмена; адрес при этом подается на шину адреса всего один раз, т.к. при пакетном чтении / записи данные записываются / читаются подряд.

CLC ALE A/D A D

D D

RD

В

FRAME