- •Принцип двоичного кодирования

- •0 D 0 0 1 0 0 0 инверт

- •1) Проверить, выровнены ли порядки, и. Если нет. То выровнять.

- •2} Сложить мантиссы (одна из них. Возможно, денормализовша).

- •С 1992 г. - неотъемлемая часть Intel и amd.

- •271 Команда - групповые арифметические и логические операции , сдвиги , сравнения , перегруппировка и извлечение отдельных чисел , различные варианты пересылок .

- •Команды управления виртуальной памятью .

- •6} В режиме ss&2

- •3 Register ImmediateFormat 1a

- •Instruction -Level Pa га I lei ism

- •Instruction -Level Parallel ism

- •Su perscalarArch itectu res

- •Intel 486 - один конвейер , Pentium - 2 конвейера из 5 стадий .

- •Su perscalarArch itectu res

- •Su perscalarArch itectu res

- •Instruction

- •1011X j|I 2 - все параллельно

- •1 Упрощается архитектура процессора ; вместо распараллеливающей логики на eric процессоре можно разместить больше регистров , функциональных устройств .

- •BusWidth

- •1. Арбитраж пин

- •3. Методы повышения эффективности пин

- •4. Стандарты шинS Примеры

- •Bus Arbitration (2)

- •Способы расширения полосы пропускания шин :

- •Pci BusTransactions

- •Сокращённые обозначения -kj,Mi7 Gi.Ti.Pi и Ei.

- •Vax/1980 pPra/1996

- •MemoryChips

- •Volatile

- •1. Блочная организация основной памяти

- •2. Микросхемы памяти

- •Расслоение памяти

- •Расслоение памяти

- •1. Динамические сву

- •Динамические сву для видеоадаптеров

- •Многопортовые os/

- •Volatile

- •2. (Пни -память

- •3. Ассоциативные 3/

- •4. Организация fau -памяти

- •Пример 2

- •Пример 2

- •1. Организация fcu -памяти

- •2. Система ввода -вывода

- •Ёмкость каи - 32kb , строки го 25б байт .

- •Address

- •64 Kb cache, direct -mapped,32 -byte cache block

- •32 Kb cache, 2 -wayset -associative, 16 -byteblocks

- •16Kb,4 -wayset-associativecache732 -bitaddress, byte -addressablememory/32 -byte cache blocks/lines

- •Write -through - прежде всего обновляется слово ,

- •Средства обнаружения и защиты от ошибок . Архитектура современных н)¥щ основана на полностью ассоциативном отображении .

- •Структура гу

- •1. Понятие конвейера

- •If: Instruction fetch

- •Id: Instruction decode/ register file read

- •Риск го данным - взаимосвязь команд го данным

- •Pipelined Datapath

- •Hazards

- •Superscalar Architectures

- •Instruction

- •Instruction decode

- •1. Очередность вьщачи декодированных команд на исполнительные блоки отличается от последовательности предписанной программой -неупорядоченная выдача команд (out-of-orderissue ),

- •Sisd,misd,simd,mimd.

- •Классификация Флинна

- •Heterogeneous multiprocessor chip with six cores

- •Организация памяти вс

- •Message-passing interconnection network

- •3 Stages

- •3 Stages

- •Num am ulti processors

- •Interconnection network

- •18Bits 8

- •18Bits 8

- •And memories are not shown.

- •(A) a star, (b) a complete interconnect.

- •(C) a tree, (d) a ring, (e) a grid, (f) a double torus.

- •(G) a cube, (h) a 4d hypercube.

- •Red Storm (2)

1. Динамические сву

2. Статические СВУ

3. Многопортовые СВУ

4. Специализированные СВУ

5. Постоянные 3/

Printed

with FinePrint- purchase atwww.fineprint.com

Слайд 2

Динамические СВ/

Динамические

ОЗУ

Асинхронные

Синхронные

FPM

EDO

EDRAM

|

1 * 1 |

t |

|

t |

|

t |

|

SDRAM |

E SDRAM |

|

SLDRAM |

|

RDRAM -± |

|

DDR |

CDRAM |

|

T DRDRAM | ||

DEDO

DDRSDRAM

-

Double

Data Rate Synchronous DRAM. Главное

отличие - данные в пакетном режиме

выдаются

го обоим фронтам импульса синхронизации

,

за счёт чего пропускная способность возрастает вдвое .

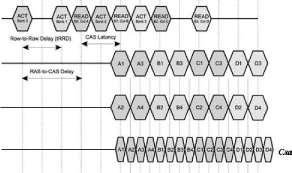

Слайд 3

Динамические СВ/

Работа

SDRSDRAM

:

Подаётся адресный си тал в соответствующую строку . Данныецелой строки попадают на усилители и через некоторое времямогут быть считаны . Такая операция называется активацией строки(го-английски Activate ).

Данные считыБаются из соответствующей колонки . Для этогоподаётся команда на чтение (го-английски Read ) Данныепоявляются на выходе с некоторой задержкой . В современнойпамяти используется чтение пакета данных (го-английски Burst),представляющего собой несколько последовательнорасположенных данных . Обычно равен 8.

Пока строка остаётся активной , возможно считывание или записьдругих ячеек памяти (текущей строки ).

-Так как при чтении заряд ёмкостей ячеек памяти теряется , то производится подзарядка этик ёмкостей или закрытие строки (Prechange ) После закрытия строки дальнейшее считывание данных невозможно без повторной активации .

Слайд 4

Printed with FinePrint- purchase atwww.fineprint.com

Динамические СВ/

Clock

RAS#

WE*

Data

(OQ] IUU0...DQ?}"

- СЬ временем конденсаторы ячеек

разражаются и vk необходимо подзаряжать . Операция подзарядки называется регенерацией (Refresh ) и выполняется каждые 64 мс для каждой строки массива памяти .

Частоте Частота буфера Чаеиня вывода

ЯДра 133 МГц нкщл.&ыипи 133 МГц данны 1 133 МГц

иплл иитя

Curt' F"rt-j Clock Fmq P.ilu Fmq.

Ядро

пЭмиш

SDRSDRAM

ЛЛЛЛЛЛЛЛЛЛЛЛЛЛЛЛЛУ

\J

C*£ Lnfimcy

ski 5

(HCO a 2; tCL - г; Длина щнетд BL ■ *

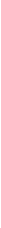

Динамические

СВ/

DDRSDRAM.

В

DCR-памяти

каждый буфер ввода-вывода на каждой

из 64 линий шины данных передает два

бита за один такт, то

есть фактически работает на удвоенной

тактовой частоте , оставаясь

гри этом полностью синхронизированным

с ядром памяти

. Такой режим работы возможен в

случае , если эти два бита доступны

буферу ввода -вывода на каждом такте

работы памяти . Для

этого требуется , чтобы каждая команда

чтения приводила к передаче

из ядра памяти в буфер ввода -вывода

сразу 2п бит . С этой

целью используются две независимые

линии передачи а

ядра

памяти

к буферам ввода -вы вед а шириной п

бит каждая , откуда биты

поступают на шину данных в требуемом

порядке .

Чтение

|

|

|

Регистр |

п бкг |

|

| |||

|

Очядра |

лшнных (в бит) |

"^* |

DO |

и бкт | ||||

|

|

|

|

МУХ Ч |

/ ►■ | ||||

|

(DRAM Core) Ъ, бит |

|

Регистр |

it бнт |

DI |

| |||

|

|

|

|

| |||||

Gustd

Printed

with FinePrint- purchase atwww.fineprint.com

Динамические СВ/

DDRSDRAM.

При

таком способе организации работы

памяти происходит

пред выборка 2п

бит

перед передачей ик на шину данных -

«2п Prefetch

» (предвыборка 2п бит ) Доступ к данным

осуществля -ется

«попарно »

— каждая

одиночная команда чтения данных

приводит

к отправке го внешней [Щ

двух

элементов (разрядность = разрядности

внешней [Щ).

Аналогично каждая команда записи

данных

ожидает поступления 2х элементов го

внешней шине данных

. Именно поэтому длина пакета (BurstLength

)

гри передаче данных

в устройствах DDRSDRAM

нэ может быть меньше 2

л Бит

(л бит)

Запись

.

—I

Регистр ц храпения Лепных (« бит)

jj Регистр

хранении

данных

(In бит)

2л 6in

й

7

Динамические

Гичто

вы? сигналы

Копищы

Сзсема работы DDH.1 такт \,

Printed with FinePrint- purchase atwww.fineprint.com

Gustd

Динамические СВ/

DDRSDRAM

-

имеет

4 банка

памяти

.

Частота Частота буфорэ Частота пыпэда

едва 1^3 МГц ввода-вывода 133 МГц данных 2б£ МГц

|_ппп иигл miw,

Core Freq. Clock Fueq. Dale Freq.

Ядро

памяти

Буферы

ввода-вывода

ODR

SDRAM

тЁшшшитииж

й

9

Перин линия шириной л Бит

Вторая линия шириной п бит

Внешняя

шина данных

шириной 2л

DCR 2 SDRAM.

Printed

with FinePrint- purchase atwww.fineprint.com

й 10

Динамические СВ/

DCR 2 SDRAM.

|

JJ |

бит -1 ъ |

PtiHti-p хранения |

|

|

|

данных (n бит) |

|

|

| |

|

|

Регистр | |

|

Or ядра |

|

данных (л бит) |

|

памяти ~^~ (DRAM Core) 4я5нт |

|

Религгр хранения |

|

|

данным (п с>ит) | |

|

| ||

|

Регистр хранения данных (п бит) |

жй 11

Динамические

DCR

2

SDRAM.

Реги<ггр q рав

1 бит

Регистр

q

хранения

Запись

6HTJ

DQS

лаиг|ы>с (п бит)

Printed with FinePrint- purchase atwww.fineprint.com

Clock

жй 12

Динамические СВ/

Параан

линия (инринон

п бит

Вторая

линия

ШИРИНОЙ

17 6НТ

Третья

линия шириной

л бит

Четвертая

линия шириной

п

Сит

Внешняя

шина

данных

шириной 2пСит

Чаеюта буфера Чаетсла быаоца

(адра 133 МГц вмща.вывада 2ЩЗ МГц данныи S33 МГц

итпл шил йш

Rape

памяти

Со» Freq. CkKfc Fraq. Data Freq.

|

|

Буфер» ваола-вывопа |

|

|

|

| |||

|

| |||

|

>->» |

|

|

DDR2SDRAM

Слайд 13

Динамические

СВ/

Сравнение

разных типов памяти.

100 МГц 100 МГц ЮОМбнт/сек

SDR

100

SDRAM

Массив памяти

Блок ввода/вывода

Передача [

L I

100

МГц

Передача

)_^ данных

DDE-ZOO SDRAM

юамгц

100 МГц 200 МГц 400М6нт/сек

Г\_П_ГЦ" QJIXIX

SDRAM

Массив памяти

Блок

ББОД^'ЕЫЕОГВ

Передача данных

Printed

with FinePrint- purchase atwww.fineprint.com

Слайд П

Динамические СВ/

DDR3.

Ожидается

, что массовое распространение DDR3

-память

получит

к концу 2006 года , а в 2009 -м станет основным

типом памяти

на рынке .

Эффективная частота работы DDR3 -памяти будет составлять от 800 до 1600 М~ц . Кроме увеличенной пропускной способности , память DDR3 будет также выгодно отличаться и уменьшенным энергопотреблением . Так, если мод\ш DDR -памяти работают при напряжении питания 2£ В, а модули памяти DDR2 — при ЦЗ В, то мод^и DDR3 -памяти работают при напряжении питания 1^5 В (на 1^5% меньше , чач для памяти DDR2). Снижение напряжения питания достигается за счет использования 90-нм техпроцесса производства микросхем памяти и применения транзисторов с двойным затвором (Dual -gate ), что способствует снижению токов утечки .

Ожидается , что первоначально емкость модулей памяти DDR3 составит 1 Гбайт , а впоследствии появятся мод\ш памяти емкостью 2 и 4 Гбайт .

Динамические

СВ/

DDR3.

Для

памяти DDR3

будет реализована 8-банковая логическая

структура

, а размер страницы составит 1 Кбайт

для чипов с шиной х4

и х8 и 2 Кбайт для чипов с шиной х1б.

Принципиальное отличие памяти DDR3 от памяти DDR2 - в реализации механизма 8i -Prefetch вместо 4n -Prefetch .

Для организации данного режима работы памяти необходимо , чтобы буфер ввода -вывода (мультиплексор ) работал на частоте в 8 раз большей го сравнению с частотой ядра памяти . Достигается это следующим образом : ядро памяти , как и прежде , синхронизируется го положительному фронту тактирующих импульсов , а с приходом каждого положительного фронта го восьми независимым линиям в буфер ввода -вывода (мультиплексор ) передаются £h бита информации (выборка 8i битов за такт). Сам буфер ввода -вывода тактируется на учетверенной частоте ядра памяти и синхронизируется как го положительному , так и го отрицательному фронту данной частоты . Это позволяет за каждый такт работы ядра памяти передавать восемь слов на шину данных , то есть в восемь раз повысить пропускную способность памяти .

Printed

with FinePrint- purchase atwww.fineprint.com

Динамические СВ/

Частота

ядра 100 МГц

Частота Ёуфера Частота вывода

4П0 МГц данных ВПО МГц

![]()

Clock Fr*q.

Буферы веоаа&ыеода

DDR3.

По

сравнению с пам5тгью ООк2лООкЗ

-пам5тгь позволяет обеспечить

ту хе

пропускную

способность при вдвое меньшей частоте

ядра . К примеру, в памяти DDR2

-800

ядро функционирует на

частоте 200 М~ц , а в памяти DDR3

-800

— на частоте 100 М~ц .

Слайд 17

Динамические СВ/

DDR3SDRAM

DDR3.

ei~k ШШВШШВ&ШШШ.

Первая лииин шириной л бит

линия и бит

Восьмая линия шириной л бит

Внешняя шина данных шириной 2л-бнт

18

Printed

with FinePrint- purchase atwww.fineprint.com

Динамические СВ/

Динамические

ОЗУ

|

|

|

|

|

4 |

|

|

| ||||||||||

|

Асинхронные |

|

Синхронные |

|

| |||||||||||||

|

i |

|

i |

|

| |||||||||||||

|

i i |

♦ t t |

1 * | |||||||||||||||

|

FPM |

|

EDRAM |

|

SDRAM |

|

E SDRAM |

|

SLDRAM |

RDRAM | ||||||||

|

EDO _L |

|

|

|

t DDR |

|

CDRAM |

|

DRDRAM | |||||||||

DEDO

Микросхемы

FD

FW ,DRDRAM .

Обычный способ повышения КГЩ памяти -повышение тактовой частоты или ширины ИД . В большинстве DRAM - широкая выборка 64 бита при ограниченной частоте шины .

Слайд

19

Динамические

RDRAM(

Rambus DynamicRAM) -три

технологии Base,

Concurrent

and Direct. Вэ всех используется DDR -

частоты удваиваются

500 -600,700 и 800 Мц (соотве -ю).

Direct Rambus DRflM - DRDRAM имеет оригинальную систему обмена данными между ядром и контроллером памяти на основе «канала Rambus »- асинхронный блочно -ориентированный протокол пакетной передачи данных .

Три вида пакетов - данных , строк и столбцов . Пакеты строк /столбцов - вместо системы управления RAS,CAS,WE,CS.

Массив ЗЭ разбит на банки (для 64 Мбит - 8 независимых и 16 сдвоенных банков ). В сдвоенных - общие УЧЗ . Внутренняя шина данных - 128 бит, го каждому адресу столбца можно передавать Ъ байт. rty записи можно использовать маску , в кот . сщн бит обозначает один байт пакета - можно указать сколько и какие байты д.б. записаны в память .

Слайд Т)

Printed with FinePrint- purchase atwww.fineprint.com

Динамические СВ/

RDWl

.

Линии

данных , строк и столбцов в «канале »

полностью

независимы - команды стр . стоп . и

дан . могут передаваться

независимо для разных банков .

Пакеты столбцов - два поля и передаются го пяти линиям . Первое поле - операция Чг или 3i. Второе - маска либо уточнение операции .

Пакеты строк (три линии ) - пакеты активации , отмены , регенерации и команды переключения режима энергопотребления .

Операция записи может следовать сразу за чтением (задержка только за каналом - от £5 до 30 не). Чтобы выровнять задержки - проводники д.б. строго параллельно и нэ более 12 см + дел . требования разработчиков .

Каждая запись в канале м.б. конвейеризирована -время задержки первого пакета - 5D не, остальные - непрерывно , задержка при смене операции (чг .-эп .).

Слюй 21

Новые разработки Rambus -Intel - nDRAM - до 1600 ГГц .

Динамические

СВ/

Динамические

ОЗУ

|

|

+ i |

|

|

| |||||||||||||||

|

Асинхронные |

|

Синхронные |

|

| |||||||||||||||

|

i |

|

i |

|

| |||||||||||||||

|

i i |

+ t . * , |

| |||||||||||||||||

|

FPM |

|

EDRAM |

|

SDRAM |

|

E SDRAM |

SLDRAM |

RDRAM | |||||||||||

|

|

if | ||||||||||||||||||

|

EDO |

|

|

|

DDR |

|

CDRAM |

|

DRDRAM | |||||||||||

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

DEDO |

| ||||||||||||||||||

Микросхемы

SLDRAM

-

основной конкурент DRDRAM

,

открытый стандарт

от SyncLink

Consortium. На системном уровне очень похож

на

DRDRAM. Контроллер - память -> пакеты 4

или 8 посылок . Команды

, адрес , vnp .

сигналы - го однонаправленной Ю битной

командной шине . Данные - го 18 разрядной

ИД . Частота - 200 М~ц , нэ

используется CCR

-

т.е. 400 М~ц (будет 400 -800 М"ц ) К одному

контроллеру

м.б. подключено др 8 микросхем памяти

. Для избегания запаздывания

- самодетекция и сокр . характер -к при

вкл . питания .

Printed

with FinePrint- purchase atwww.fineprint.com

Динамические СВ/

Динамические

ОЗУ

FPM

EDO

Асинхронные

EDRAM

|

|

|

i |

|

|

|

|

|

|

|

Синхронные |

| |||

|

|

|

i |

| |||

|

|

1 * 1 |

t + | ||||

|

SDRAM |

Е SDRAM |

SLDRAM |

|

RDRAM | ||

т

DDR

CDRAM

DRDRAM

DEDO

Микросхемы

ESDRAM

-

синхронная версия EDFftM

-

с использованием

встроенной кш -памяти . Операция

записи в отличие

от чтения - в обход кш -памяти , что

увеличивает производительность

при повторном чтении из «старой

строки в кэше

». Два банка памяти в микросхеме - мин

. простои из-за подготовки

к операциям чтения /записи .

Минуы те же - усложнение контроллера , т.к. он дол>кенучитывать загрузку в кш новой строки ядра , а так же -неэффективность при произвольном чтении . ^^ ъ

Динамические

Динамические

ОЗУ

Асинхронные

Синхронные

DRDRAM

EDO

EDRAM

|

i |

|

t |

|

t |

|

t | |

|

SDRAM |

|

ESDRAM |

|

SLDRAM |

|

RDRAM | |

|

|

| ||||||

|

DDR |

CDRAM | ||||||

DEDO

Микросхемы

CDFflM

-

усовершенствование ESDRAM

компанией Mitsubishi.

Изменены ёмкость кш -памяти и принцип

размещения в ней

данных . Ёмкость одного блока - 128 бит,

т.е.

в 16 Кбит кэша -до

128 участков памяти . Замена первого

помещённого в кш блока -только

после полного заполнения кэша .

ML24-

Используются раздельные Ш\ для статического кэша и динамического ядра . Перенос данных из ядра в кш совмещён с выдачей данных на шину -> частые внутренние пересылки нэ влияют на производительность . Но ещё большее усложнение

Printed

with FinePrint- purchase atwww.fineprint.com

Статические СВ/

Статические

СВУ

![]()

Асинхронные

Синхронные

Спец . прим -я Энергонезав -е

![]()

![]()

си л

X

ь

о

си л

X

ь

о

и

и О

си

X

л

X

5

о.

л со

|

■*■■■ ш |

|

>• |

|

|

|

|

8 |

|

|

й |

|

|

|

ш D. |

|

|

п. |

|

|

|

Е |

изаци |

|

'си |

|

овые |

|

си |

о. си |

|

|

|

о. |

|

X |

|

|

о |

|

о |

|

едова |

конве! |

|

здыва |

|

Двухп |

|

о. |

|

|

та |

|

|

|

ш |

|

|

с |

|

|

|

т |

|

|

та |

|

|

|

|

|

|

m |

|

|

ш л ш о

О

с

о

X

ш Р

л

X

та

8

и

Слайд 25

Статические СВ/

Асинхронные

статические СВУ

- применялись в кэшпамяти

2го уровня начиная с ВО 386. Время

доступа -Б-20

нс (в лучшем случае 12 не).

Синхронные статические СВУ - SSRAM и PBSRAM . Отличительная особенность SSRAM - входные регистры , фиксирующие входную информацию . Работают в режиме 3-1-1-17 нэ если частота выше , то 3-2-2-2.

PBSRAM - Pipelined Bursts RAM - внутренняя конвейеризация , скорость возрастает вдвое . Хорошо работает при повышенных частотах системной шины . Время доступа - от 4,5 до 8 не - 3-1-1-1 даже при 133 Мц .

Слайд 25

Printed with FinePrint- purchase atwww.fineprint.com

Статические СВ/

Запись

в статических QB/

-

стандартная

- адрес и данные на шине

в одном и тем »€ такте и запаздывающая

- данные на шине нэ

сразу , а в следующем такте после адреса

. Оба варианта работают

на частоте шины .Разница -лишь при

переключении операции

- чтение /запись , запись /чтение .

В стандартном режиме - потеря нескольких тактов на переключение . В каи памяти - нэ страшно , запись -гораздо реже , чал чтение - количество переключений нэ велико .

В режиме с запаздыванием потери тактов нэ происходит .

ZBTSRAM - ZeroBusTurnaround -нулевое время переключение шины от IDT (Integrated Device Technology) -запись с запаздыванием производить с теч же интервалом , что требуется для чтения . Если SF&M с конвейером требует три тактовых периода для чтения данных из ячейки , то данные для записи нужно передавать с таким же промедлением относительно адреса . В результате циклы чтения и записи - один за одним , без задержек .

Слайд 27

Статические СВ/

Энергонезависимые

СВУ - (NVRAM

-

Non

-VolatileRAM) -несколько

типов памяти - от ГЕУ они отличаются

отсутствием операции «стирания » и

нового «программирования » информации

.

BBSRAM - обычные статические СВУ аэ встроенным литиевым аккумулятором и усиленной защитой от екл ./выкл . внешнего питания .

NVRAM от Simtec - в одном корпусе - SF&M и перепрограммируемое EEPROM .При включении -данные из EEPROM в SR4M , гри выключении - из SR4M в EEPROM.

FF&M (Ferroelectric RAM) - ферроэлектрическая память от компании Ramtron - быстродействие чуть ниже динамических ОБУ, альтернатива флаи -памяти . Отсутствие явно выраженного стирания перед записью . Принцип действия аналогичен DF№M , нэ конденсатор - из ВаТО 3 и нэ разряжается так быстро . При чтении требует регенерации . Количество циклов записи - 10 млрд .

Слюй "В

Printed with FinePrint- purchase atwww.fineprint.com

Специализированные

Специализированные

СВ/ - кроме стандартных функций в

схеме реализованы

дел . возможности :

Память для видеоадаптеров

Память с множественным доступом (-статическая )

Память типа очереди (RPO) (- статическая )

Видеопамять . Динамические сцены - вместо пересылки данных го шине - изменение ик положения средствами самой микросхемы памяти . Изменение цвета точек - пикселей .

SGRAM -SynchronousGraphicDRAM -может самостоятельно совершать блочную запись данных . Два режима записи - можно менять цвет сразу 8 пикселей и блочная запись с маскированием -отдельные пиксели блока нэ меняют цвет при перезаписи . Модификация микросхемы - DDRSGRAM.

VFftM - VideoRAM -высокая производительность . Постоянное обновление данных на экране - поток 200 Мбит /с. Процессору очень сложно получить доступ к памяти при такой интенсивности^^

СВ/

Видеоадаптеров