Министерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР) Кафедра безопасности информационных систем (БИС)

РАЗРАБОТКА ВЫЧИСЛИТЕЛЬНОГО БЛОКА

Отчет по лабораторной работе №5

по дисциплине «Электроника и схемотехника 2» Вариант №9

Студент гр. 731-2

_____________

03.06.2023

Руководитель Доцент каф. КИБЭВС, к.т.н., доцент

_________ _____________ А.Н. Мальчуков

03.06.2023

Томск 2023

|

|

Оглавление |

|

Введение................................................................................................................... |

3 |

||

1 |

ОБОБЩЕННАЯ ФУНКЦИОНАЛЬНАЯ СХЕМА ........................................... |

5 |

|

2 |

ТАБЛИЦЫ ФУНКЦИОНИРОВАНИЯ .............................................................. |

6 |

|

3 |

ФУНКЦИОНАЛЬНАЯ СХЕМА....................................................................... |

10 |

|

4 |

МОДЕЛИРОВАНИЕ.......................................................................................... |

14 |

|

5 |

ОПИСАНИЕ ФУНКЦИОНАЛЬНОЙ СХЕМЫ НА HDL .............................. |

18 |

|

|

5.1 |

Описание входной части ............................................................................. |

21 |

|

5.2 |

Описание операционного блока ................................................................. |

23 |

|

5.3 |

Описание выходной части .......................................................................... |

25 |

6 |

МОДЕЛИРОВАНИЕ ФУНКЦИОНАЛЬНОЙ СХЕМЫ ОПИСАННОЙ НА |

|

|

HDL |

......................................................................................................................... |

28 |

|

Заключение ............................................................................................................ |

31 |

||

2

Введение

Цель работы: научиться совместно применять устройства средней

степени интеграции.

Постановка задачи:

1.разработать обобщенную функциональную схему устройства согласно варианту №9 и описать составные части схемы.

2.составить таблицы функционирования операционного блока, а также составить план моделирования используя для каждой операции по два различных набора данных. Поставить в плане моделирования вызов значения счётчика операций в конце моделирования до сброса и после него.

3.собрать схему на холсте .bdf, используя встроенные блоки регистров

(lpm_dff, lpm_shiftreg и lpm_counter) организовав прием и выдачу данных согласно варианту №9, а именно приём данных задним фронтом параллельным кодом с синхронным сбросом, а выдачу данных передним фронтом последовательным кодом старшими разрядами вперед при активном сигнале «Read» = 1.

4. создать схему реализации вычислительного блока, выполняющие заданные операции согласно варианту №9. Вычислительный блок должен после получения входных данных выполнить операцию согласно коду операции: 00 - операция не производится, на выход передаётся значение счётчика выполненных операций; 01 – проверка Commodore GCR-кода; 10 – над 3-х разрядными А и В выполняется логическая побитовая операция ,

после 3-х разрядный результат подаётся на выход; 11 – над 3-х разрядными А и В выполняется арифметическая операция A-B, после 3-х разрядный результат подаётся на выход.

5. промоделировать работу схемы в двух режимах. Провести анализ результатов моделирования разных режимов. Сверить результаты моделирования с составленной таблицей истинности.

3

5. повторить пункты 3-4, только для описания устройств вместо схем используя заданный вариантом №9 язык описания HDL, а именно VHDL.

6. написать выводы о проделанной работе.

4

1 ОБОБЩЕННАЯ ФУНКЦИОНАЛЬНАЯ СХЕМА

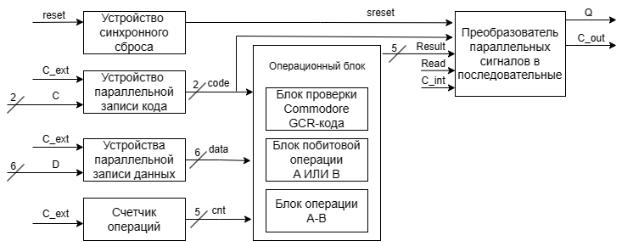

Обобщенная функциональная схема, представлена на рисунке 1.1.

Устройство состоит из трех основных частей: входной части, операционного блока и выходной части. Входная часть состоит из 4 других устройств:

устройства параллельной записи кода, устройства параллельной записи данных, счетчика операций, а также устройства синхронизации сброса.

Операционный блок состоит из трех блоков: блока побитовой операции ,

блока операции разности и блока проверки Commodore GCR-кода. Выходная часть состоит из устройства, преобразующего параллельные сигналы в последовательные, где учитываются сигнал «Read», а также синхроимпульс.

Рисунок 1.1 – Обобщенная функциональная схема

5

2 ТАБЛИЦЫ ФУНКЦИОНИРОВАНИЯ

Таблица истинности для задачи согласно варианту №9, а именно для проверки Commodore GCR-кода, представлена в таблице 2.1.

Таблица 2.1 – Таблица истинности проверки Commodore GCR-кода

|

|

Входы |

|

|

|

|

Выходы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x4 |

x3 |

x2 |

x1 |

x0 |

ST2 |

ST1 |

SP2 |

|

SP1 |

FB |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

Таблица истинности для побитовой логической операции согласно варианту №9, а именно для операции А B, представлена в таблице 2.2.

Таблица 2.2 – Таблица истинности побитовой логической операции

6

А B

|

|

Входы |

|

|

|

|

Выходы |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||

|

A |

|

|

B |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

A2 |

A1 |

A0 |

B2 |

B1 |

B0 |

Q4 |

Q3 |

|

Q2 |

|

Q1 |

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

- |

- |

|

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

X |

0 |

0 |

1 |

- |

- |

|

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

X |

0 |

0 |

1 |

0 |

- |

- |

|

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

X |

X |

0 |

1 |

1 |

- |

- |

|

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

0 |

1 |

0 |

0 |

- |

- |

|

1 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

X |

1 |

0 |

1 |

- |

- |

|

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

0 |

1 |

1 |

0 |

- |

- |

|

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

X |

1 |

1 |

1 |

- |

- |

|

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

- |

- |

|

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

0 |

X |

- |

- |

|

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

X |

0 |

- |

- |

|

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

X |

X |

- |

- |

|

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

X |

0 |

0 |

- |

- |

|

1 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

X |

0 |

X |

- |

- |

|

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

X |

X |

0 |

- |

- |

|

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

X |

X |

X |

- |

- |

|

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица истинности для арифметической операции согласно варианту №9, а именно для операции А - B, представлена в таблице 2.3.

Таблица 2.3 – Таблица истинности арифметической операции

A-B

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

||

|

A |

|

|

B |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

A2 |

A1 |

A0 |

B2 |

B1 |

B0 |

|

Q5 |

Q3 |

Q2 |

|

Q1 |

Q0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

- |

- |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

- |

- |

1 |

|

1 |

1 |

|

|

|

|

|

|

7 |

|

|

|

|

|

|

Продолжение таблицы 2.3.

A-B

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

||

|

A |

|

|

B |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

A2 |

A1 |

A0 |

B2 |

B1 |

B0 |

|

Q5 |

Q3 |

Q2 |

|

Q1 |

Q0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

- |

- |

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

- |

- |

1 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

- |

- |

1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

- |

- |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

|

- |

- |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

- |

- |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

|

- |

- |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

- |

- |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

- |

- |

1 |

|

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

|

- |

- |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

|

- |

- |

1 |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|

- |

- |

1 |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

- |

- |

0 |

|

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

|

- |

- |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

- |

- |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

- |

- |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

|

- |

- |

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

|

- |

- |

1 |

|

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|

- |

- |

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

|

- |

- |

1 |

|

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

|

- |

- |

1 |

|

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

|

- |

- |

0 |

|

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

|

- |

- |

0 |

|

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

- |

- |

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

- |

- |

0 |

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

- |

- |

0 |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

|

- |

- |

1 |

|

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

|

- |

- |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

- |

- |

1 |

|

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

- |

- |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

- |

- |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

|

- |

- |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

|

- |

- |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

- |

- |

0 |

|

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

|

- |

- |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

- |

- |

1 |

|

1 |

1 |

|

|

|

|

|

|

8 |

|

|

|

|

|

|

Продолжение таблицы 2.3.

A-B

|

|

Входы |

|

|

|

|

Выходы |

|

|

||

|

A |

|

|

B |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

A2 |

A1 |

A0 |

B2 |

B1 |

B0 |

Q5 |

Q3 |

Q2 |

|

Q1 |

Q0 |

1 |

0 |

0 |

1 |

1 |

0 |

- |

- |

1 |

|

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

- |

- |

1 |

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

- |

- |

1 |

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

- |

- |

1 |

|

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

- |

- |

0 |

|

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

- |

- |

0 |

|

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

- |

- |

0 |

|

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

- |

- |

0 |

|

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

- |

- |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

- |

- |

1 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

- |

- |

1 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

- |

- |

1 |

|

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

- |

- |

1 |

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

- |

- |

0 |

|

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

- |

- |

0 |

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

- |

- |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

- |

- |

0 |

|

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

- |

- |

1 |

|

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

- |

- |

1 |

|

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

- |

- |

1 |

|

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

- |

- |

1 |

|

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

- |

- |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

- |

- |

0 |

|

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

- |

- |

0 |

|

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

- |

- |

0 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

- |

- |

0 |

|

0 |

0 |

9

3 ФУНКЦИОНАЛЬНАЯ СХЕМА

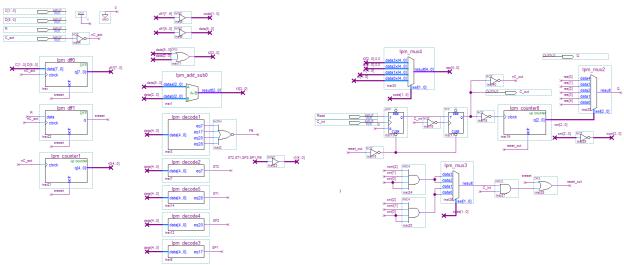

Функциональная схема согласно варианту №9, а именно с приёмом данных задним фронтом параллельным кодом с синхронным сбросом и выдачей данных передним фронтом последовательным кодом старшими разрядами вперед при активном сигнале «Read» = 1, а также с операционным блоком для проверки Commodore GCR-кода, логической побитовой операции и арифметического разности, представлена на рисунке 3.1.

Рисунок 3.1 –Функциональная схема

Далее на рисунке 3.2 представлена входная часть. Входная часть состоит из записывающего регистра, на вход которого подаются два набора данных: A

и B и кода операции. После выхода из записывающего регистра данные разделяются на два набора. Счетчик данных входной части работает задним фронтом, на вход которого подается сигнал синхроимпульса. Выход счетчика используется как код операции для операционного блока. Также присутствует регистр, ответственный за синхронный сброс.

10