gosy_voprosy / вопрос_36

.docxОсобенности архитектуры

Основная статья: Intel P6

Первые процессоры архитектуры P6 в момент выхода значительно отличались от существующих процессоров. Процессор Pentium Pro отличало применение технологии динамического исполнения (изменения порядка исполнения инструкций), а также архитектура двойной независимой шины (англ. Dual Independent Bus), благодаря чему были сняты многие ограничения на пропускную способность памяти, характерные для предшественников и конкурентов. Тактовая частота первого процессора архитектуры P6 составляла 150 МГц, а последние представители этой архитектуры имели тактовую частоту 1,4 ГГц. Процессоры архитектуры P6 имели 36-разрядную шину адреса, что позволило им адресовать до 64 ГБ памяти (при этом линейное адресное пространство процесса ограничено 4 ГБ, см PAE).

Суперскалярный механизм исполнения инструкций с изменением их последовательности

Принципиальным отличием архитектуры P6 от предшественников является RISC-ядро, работающее не с инструкциями x86, а с простыми внутренними микрооперациями. Это позволяет снять множество ограничений набора команд x86, таких как нерегулярное кодирование команд, переменная длина операндов и операции целочисленных пересылок регистр-память[2]. Кроме того, микрооперации исполняются не в той последовательности, которая предусмотрена программой, а в оптимальной с точки зрения производительности, а применение трёхконвейерной обработки позволяет исполнять несколько инструкций за один такт[3].

Суперконвейеризация

Процессоры архитектуры P6 имеют конвейер глубиной 12 стадий. Это позволяет достигать более высоких тактовых частот по сравнению с процессорами, имеющими более короткий конвейер при одинаковой технологии производства. Так, например, максимальная тактовая частота процессоров AMD K6 на ядре (глубина конвейера — 6 стадий, 180 нм технология) составляет 550 МГц, а процессоры Pentium III на ядре Coppermine способны работать на частоте, превышающей 1000 МГц.

Для того, чтобы предотвратить ситуацию ожидания исполнения инструкции (и, следовательно, простоя конвейера), от результатов которого зависит выполнение или невыполнение условного перехода, в процессорах архитектуры P6 используется предсказание ветвлений. Для этого в процессорах архитектуры P6 используется сочетание статического и динамического предсказания: двухуровневый адаптивный исторический алгоритм (англ. Bimodal branch prediction) применяется в том случае, если буфер предсказания ветвлений содержит историю переходов, в противном случае применяется статический алгоритм[3][4].

Двойная независимая шина

С целью увеличения пропускной способности подсистемы памяти, в процессорах архитектуры P6 применяется двойная независимая шина. В отличие от предшествующих процессоров, системная шина которых была общей для нескольких устройств, процессоры архитектуры P6 имеют две раздельные шины: Back side bus, соединяющую процессор с кэш-памятью второго уровня, и Front side bus, соединяющую процессор с северным мостом набора микросхем

Родоначальник семейства “x86” – процессор i8086 имеет один единственный режим работы (который впоследствии назвали “Real Mode” – или режим реального адреса). Начиная с процессора i80286, все последующие модели имеют возможность работать так же и в защищенном режиме “Protected Mode” (режим виртуального адреса). Процессоры i80386 и выше имеют также режим виртуального процессора i8086 – “V86 Mode”, который расширяет возможности защищенного режима (эмуляция реального режима).

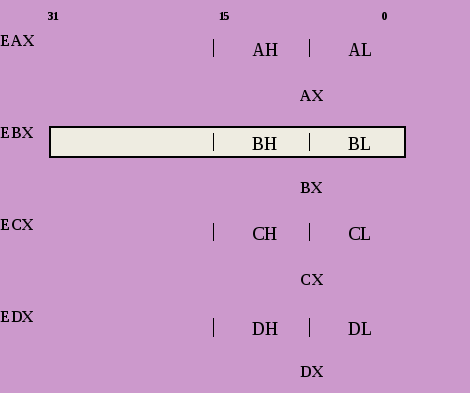

В реальном режиме любой “x86” - совместимый процессор имеет архитектуру 8086, но обладает повышенным быстродействием и расширенной системой команд. При этом возможно использование для программирования как 16-ти, так и 32-х разрядных регистров, в том числе и новых («32-разрядный 8086»).

Особенность архитектуры 8086 состоит в ограниченности объема используемой (адресуемой) памяти = 220 байтов = 1 Мбайт. (ША =20 разрядов)

Используется принцип сегментной адресации любого байта этого адресного пространства.

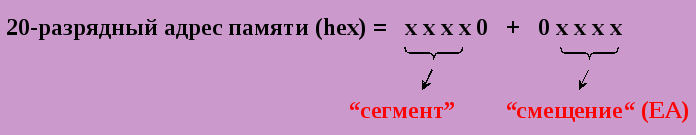

Программно задаваемые “сегмент” и “смещение” являются логическими (программными) компонентами адреса памяти.

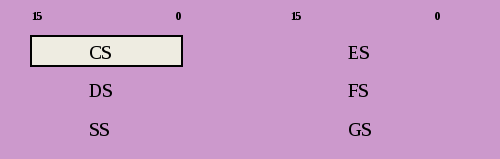

“сегмент” – старшие 16 разрядов адреса. Находится в одном из сегментных регистров.

“смещение” – 16-ти разрядная величина внутрисегментного смещения (индекс внутри сегмента).

20-разрядный физический адрес памяти вычисляется микропроцессором из логических компонент аппаратно.

Реальный режим сохранен в 32-разрядных современных процессорах для поддержки исполнения однопрограммных операционных систем, ориентированных на архитектуру 8086 (MSDOS, PCDOS), и сохранения архитектурной и программной преемственности с процессорами ранних моделей.

При включении процессор находится в реальном режиме. Переход в защищенный режим выполняется программно (см. приложение 2).

Архитектура защищенного режима принципиально отличается от архитектуры реального режима. Программно эти режимы не совместимы в силу различных механизмов управления памятью! Программы, написанные под реальный режим в защищенном режиме (на процессоре i80286) работать не могут (процессоры i80386 и выше в защищенном режиме имеют возможность эмуляции виртуальной машины 8086 – режим “V86 Mode”).

Строго говоря, защищенный режим процессора i80286 (во времена этого процессора) программистами не использовался. Так как его преимущества не были столь очевидными (объём памяти 286-ого компьютера редко превышал один мегабайт), а совместимость таких программ с большим, на то время, парком 86-х компьютеров бы терялась. Средств выполнения программ реального режима под операционной системой защищенного режима тогда не было (режим V86 появился в процессорах начиная с i80386). Поэтому 286-е машины использовались просто как скоростные варианты 86-х. И только с появлением первого 32-х разрядного процессора i80386 – защищенный режим (сильно измененный и дополненный) стал набирать популярность. Появлялись первые операционные системы защищенного режима, которые, кстати, в дань совместимости, поначалу поддерживали и защищенный режим процессора i80286.

Далее мы будем рассматривать защищенный режим, опираясь именно на его реализацию в i80386, так как в последующих процессорах (i80486, Pentium и т.п.) он не претерпел существенных изменений, а был лишь немногим дополнен.

1.2 Основные возможности и преимущества защищенного режима.

Защищенный режим и все принципы работы процессора в этом режиме разрабатывались с целью возможности мультизадачного выполнения программ. Если поставить вопрос о создании операционной системы реального режима с поддержкой многозадачности, то сразу возникает проблема: как изолировать программы от взаимного влияния друг на друга, а при необходимости разрешить обмен информацией. Чтобы ввести такое регулирование, нужно иметь больше информации о самих задачах, что эффективно реализовать в реальном режиме невозможно. Можно предложить различные способы структурной организации и размещения такой информации. Intel не стала нарушать принцип сегментации памяти. Так как каждая задача может занимать один или несколько сегментов, то целесообразно иметь о них больше информации, как об объектах, реально существующих в данный момент в системе. Если каждому из этих объектов (сегментов) присвоить определенные атрибуты, то контроль за ними можно переложить на процессор. Что и было сделано корпорацией Intel.

Основные преимущества защищенного режима:

-

Аппаратные механизмы управления памятью, позволяющие адресовать большой физический объем оперативной памяти – 16Мб для процессора i80286 (ША=24 разряда) и 4Гб для процессора i80386+ (ША=32 разряда);

-

Аппаратные механизмы защиты адресных пространств загруженных задач друг от друга;

-

Аппаратные механизмы для переключения исполнения с одной задачи на другую;

-

Возможность использования «виртуальной памяти»;

-

Возможность страничной адресации памяти;

-

Аппаратная возможность эмуляции виртуальной машины 8086 для исполнения программ реального режима (на процессорах 386+).

1.3 Программная модель 32-разрядных микропроцессоров в защищенном режиме.

Регистры общего назначения.

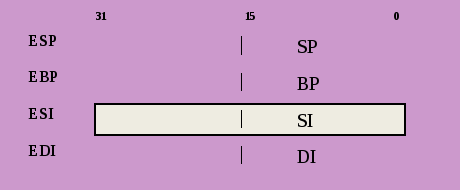

Регистры указатели адреса.

Регистры указатели сегментов памяти.

FS, GS – регистры дополнительных сегментов данных

Регистр указатель команд.

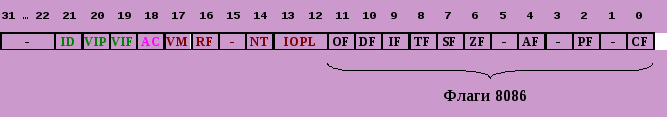

Регистр признаков (флагов) (8086, 80386, 80486, Pentium).

Флаги ID, VIP, VIF, AC, VM, RF, NT, IOPL используются операционной системой только в защищенном режиме.

IOPL (Input/Output Privilege Level) - задает минимальный уровень привилегий задачи для выполнения команд ввода/вывода (для реального режима всегда 0) (см. главу 3)

NT (Nested Task) = 1 показывает, что текущая задача является вложенной в другую. Устанавливается при переключении задач. Используется командой IRET для определения алгоритма ее функционирования (см. главу 5)

RF (Restart Flag) – используется для аппаратной отладки, совместно с отладочными регистрами

VM (Virtual Mode) – используется для перехода в режим «виртуального 8086». Бит может устанавливаться только в защищенном режиме – инструкцией IRET на нулевом уровне привилегий (см. главу 3) или переключением задач на любом уровне привилегий (см. главу 6)

AC (Alignment Check) – флаг контроля выравнивания (для задач с уровнем привилегий 3). При установленном флаге и обращении к не выровненному операнду происходит исключение #AC (см. главу 4)

VIF (Virtual Interrupt Flag) – виртуальный флаг IF (разрешение прерывания) для многозадачных систем (см. главу 6)

VIP (Virtual Interrupt Pending) – виртуальный запрос прерывания.

ID (Identification flag) – флаг доступности инструкции CPUID (аппаратная идентификация процессора)

Системные регистры.

Используются при управлении памятью и переключении задач. К ним относятся:

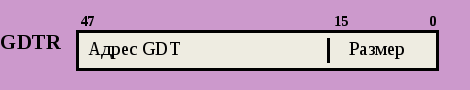

Регистр адреса глобальной дескрипторной таблицы (GDT) (см. главу 2).

Регистр адреса таблицы дескрипторов прерываний (IDT) (см. главу 4).

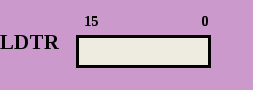

Регистр – селектор сегмента локальной дескрипторной таблицы (LDT) (см. главу 2).

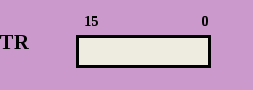

Регистр – селектор сегмента состояния задачи (TSS) (см. главу 5).

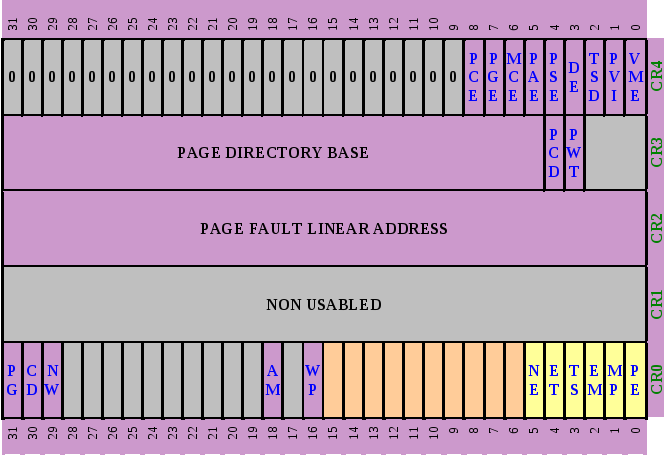

Регистры управления – 32-разрядные CR0, CR1, CR2, CR3, CR4

Управляющие регистры (Control Registers) CR0, CR1, CR2, CR3 хранят признаки состояния процессора, общие для всех задач. Регистр СR0[015] включает в себя биты регистра MSW процессора 80286. Для обеспечения программной совместимости команды LMSW и SMSW затрагивают только эти младшие 4 бита.

Таблица 1.1 Регистры управления

Назначение бит регистра СR0:

-

РЕ (Protection Enable) - разрешение защиты. Установка этого флага инструкцией LMSW или LOAD CR0 переводит процессор в защищенный режим, сброс флага (возврат в реальный режим) возможен только по инструкции LOAD CR0. Сброс бита РЕ является частью довольно длинной последовательности инструкций, подготавливающих корректное переключение в реальный режим.

-

МР (Monitor Processor Extension) - мониторинг сопроцессора. Позволяет вызывать исключение #NM по каждой команде WAIT при TS=1. При исполнении программ для процессоров 286/287 и 386/387 на процессорах 486DX и старше бит МР должен быть установлен.

-

EM (Processor Extension Emulated) - эмуляция сопроцессора. Установка этого флага вызывает появление исключения #NM при каждой команде, относящейся к сопроцессору, что позволяет прозрачно осуществлять его программную эмуляцию.

-

TS (Task Switch) - переключение задач. При установке этого флага следующая команда, относящаяся к сопроцессору, вызовет исключение #NM, что позволяет программно определить, относится ли контекст сопроцессора к текущей задаче. Бит сбрасывается инструкцией CLTS.

Сочетание MP=0 EM=0 TS=0, устанавливаемое по аппаратному сбросу, обеспечивает полную совместимость с 8086/88 (исключение #NM не вырабатывается). Сочетание МР=1, EM=0 используется при наличии сопроцессора, а МР=0, EМ=1 при его программной эмуляции.

-

ЕТ (Extension Туре) - индикатор поддержки инструкций математического сопроцессора. Используется в процессорах 486+, для 486SX - ET=0, для остальных процессоров — ET=1.

-

NE (Numeric Error) - разрешение стандартного (для Intel, но не для PC) механизма сообщения об ошибке FPU через генерацию исключения (486+).

-

WP (Write Protect) - разрешение защиты страниц памяти.

-

AM (Alignment Mask) - разрешение контроля выравнивания (контроль выравнивания выполняется только на уровне привилегий 3 при АМ=1 и флаге АС=1).

-

NW (Not Write through) - запрет сквозной записи кэша и циклов аннулирования.

-

CD (Cache Disable) - запрет заполнения кэша (попадания в ранее заполненные строки при этом обслуживаются кэшем).

-

PG (Paging Enable) - включение механизма страничной переадресации памяти.

Регистр CR1 не используется.

Регистр CR2 (Page Fault Linear Address) хранит 32-битный линейный адрес, по которому был получен последний отказ страницы памяти.

Регистр СRЗ (Page Directory Base Register) в старших 20 битах хранит физический базовый адрес таблицы каталога страниц. Из младших 12 бит в процессорах 486+ используются следующие:

-

PCD (Page-Level Cache Disable) - запрет кэширования страницы (один из источников аппаратного сигнала PCD для управления внешним кэшем).

-

PWT (Page-Level Writes Trough) - кэширование страницы со сквозной записью (один из источников аппаратного сигнала PWT для управления внешним кэшем).

Регистр CR4 (присутствует в процессорах Pentium и старше) содержит биты разрешения архитектурных расширений. Назначение бит регистра CR4:

-

VME (Virtual-8086 Mode Extensions) - разрешение использования виртуального флага прерываний в режиме V86, что позволяет повысить производительность за счет сокращения вызовов монитора виртуальных машин.

-

PVI (Protected-Mode Virtual Interrupts) - - разрешение использования виртуального флага прерываний в защищенном режиме.

-

TSD (Time Stamp Disable) - превращение инструкции RDTSC (чтение счетчика меток реального времени) в привилегированную.

-

DE (Debugging Extensions) - расширение отладки (разрешение точек останова на инструкциях обращения к заданным портам ввода/вывода).

-

PSE (Page Size Extension) - расширение размера страницы (4 Кбайт и 4 Мбайт).

-

РАЕ (Physical Address Extension) - расширение физического адреса (страницы 4 Кбайт и 2 Мбайт, 36-битная адресация).

-

MCE (Machine-Check Enable) - разрешение машинного контроля (выработки исключения #МС по машинной ошибке, Р5+).

-

PGE (Paging Global Extensions) - разрешение глобальности в страничной переадресации. При PGE=1 по команде MOV CR3 в TLB (Translation Lookaside Buffer – буфер ассоциативной трансляции адресов страниц) очищаются только вхождения с не установленным битом глобальности G (P6+).

-

РСЕ (Performance-monitoring Counter Enable) - разрешение обращения к счетчикам событий (инструкция RDPMC) на любом уровне привилегий.

Регистры отладки – 32-разрядные DR0, DR1, . . . DR7

Предназначены для аппаратной отладки. Средства аппаратной отладки машинного кода появились только в процессоре i80486. Аппаратно процессор содержит восемь регистров отладки – реально используются только шесть. Регистры DR0DR3 предназначены для задания линейных адресов четырех точек прерывания. Механизм таков: любой формируемый текущей программой адрес сравнивается со значениями этих регистров, и при совпадении генерируется исключение отладки с номером 1. Регистр DR6 – регистр состояния отладки, его биты устанавливаются в соответствии с причинами, которые вызвали исключение с номером 1.

-

b0 – прерывание по достижению контрольной точки в DR0;

-

b1 – тоже в DR1;

-

b2 – тоже в DR2;

-

b3 – тоже в DR3;

-

bd (13) – служит для защиты регистров отладки;

-

bs (14) – устанавливается в «1», если исключение 1 было вызвано состоянием флага tf=1 в регистре Eflags;

-

bt (15) – устанавливается в «1», если исключение 1 было вызвано переключением на задачу с установленным битом ловушки в TSS t=1;

Все остальные биты заполняются нулями. Обработчик исключения 1 должен определить его причину по этому регистру и выполнить необходимые действия.

Регистр DR7 – регистр управления отладкой. Содержит поля, для всех четырех регистров отладки, уточняющие условия генерации исключения.

Современные модели процессоров семейства “x86” имеют дополнительные управляющие биты в регистре признаков, управляющих регистрах, дополнительные регистры для контроля и управления. Их количество и назначение индивидуально для каждого процессора.