- •Глава1 Что такое цифровые микросхемы. Виды цифровых микросхем

- •Глава 2 Области применения цифровых микросхем

- •Глава 3 Условные графические изображения цифровых микросхем (гост)

- •Параметры цифровых микросхем

- •Уровни логического нуля и единицы

- •Входные и выходные токи цифровых микросхем

- •Параметры, определяющие быстродействие цифровых микросхем

- •Описание логической функции цифровых схем

- •Раздел 2

- •Логический элемент "и"

- •Логический элемент "или"

- •Глава 2 Диодно-транзисторная логика (дтл)

- •Глава 3 Транзисторно-транзисторная логика (ттл)

- •Логические уровни ттл микросхем

- •Семейства ттл микросхем

- •Глава 4 Цифровые логические микросхемы, выполненные на комплементарных моп транзисторах (кмоп) Логические кмоп (кмдп) инверторы

- •Логические кмоп (кмдп) элементы "и"

- •Логические кмоп (кмдп) элементы "или"

- •Особенности применения кмоп микросхем

- •Логические уровни кмоп микросхем

- •Семейства кмоп микросхем

- •Глава 5 Согласование цифровых микросхем различных серий между

- •Согласование микросхем из различных серий между собой

- •Согласование по току

- •Согласование микросхем с различным напряжением питания

- •Глава 6 Регенерация цифрового сигнала (Триггер Шмитта)

- •Раздел 3 Арифметические основы цифровой техники.

- •Глава 1

- •Арифметические основы цифровой техники

- •Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •Восьмеричная система счисления

- •Шестнадцатеричная система счисления

- •Глава 2 Преобразование чисел из одной системы счисления в другую

- •Преобразование целых чисел

- •Глава 3 Преобразование дробной части числа

- •Раздел 4

- •2. Законы отрицания a. Закон дополнительных элементов

- •B. Двойное отрицание

- •C. Закон отрицательной логики

- •3. Комбинационные законы

- •A. Закон тавтологии (многократное повторение)

- •B. Закон переместительности

- •Совершенная дизъюктивная нормальная форма (сднф)

- •Совершенная конъюктивная нормальная форма (скнф)

- •Глава 3 Дешифраторы (декодеры)

- •Десятичный дешифратор (декодер)

- •Семисегментный дешифратор

- •Глава 4 Шифраторы (кодеры)

- •Глава 5 Мультиплексоры

- •Особенности построения мультиплексоров на ттл элементах

- •Особенности построения мультиплексоров на кмоп элементах

- •Глава 6 Демультиплексоры

- •Раздел 5 Генераторы

- •Глава 1

- •Генераторы периодических сигналов

- •Усилительные параметры кмоп инвертора

- •Глава 2 Осцилляторные схемы генераторов

- •Глава 3 Мультивибраторы

- •Глава 4 Особенности кварцевой стабилизации частоты цифровых генераторов

- •Глава 5 Одновибраторы (ждущие мультивибраторы)

- •Укорачивающие одновибраторы

- •Расширяющие одновибраторы (ждущие мультивибраторы)

- •Раздел 6 Последовательностные устройства (цифровые устройства с памятью)

- •Глава 1

- •Триггеры

- •Глава 2 rs триггер

- •Синхронный rs триггер

- •Глава 3 d триггеры, работающие по потенциалу (статические d триггеры)

- •Глава 4 Явление метастабильности

- •Глава 5 d триггеры, работающие по фронту (динамические d триггеры)

- •Глава 6 t триггеры

- •Глава 7 jk триггер

- •Глава 8 Регистры

- •Параллельные регистры

- •Глава 9 Последовательные (сдвиговые) регистры

- •Глава 10 Универсальные регистры

- •Глава 11 Счётчики

- •Двоичные асинхронные счётчики

- •Двоичные вычитающие асинхронные счётчики

- •Глава 12 Недвоичные счётчики с обратной связью

- •Глава 13 Недвоичные счётчики с предварительной записью

- •Глава 14 Синхронные счётчики

- •Глава 15 Синхронные двоичные счётчики

- •Раздел 7

- •Современные виды цифровых микросхем.

- •Глава 1

- •Микросхемы малой степени интеграции (малая логика)

- •Глава 2 Программируемые логические интегральные схемы (плис).

- •Классификация плис

- •Глава 3 Программируемые логические матрицы.

- •Глава 4 Программируемые матрицы логики (pal).

- •Глава 5 Сложные программируемые логические устройства (cpld).

- •Внутреннее устройство cpld

- •Разработка цифровых устройств на cpld

- •Глава 6 Программируемые пользователем вентильные матрицы (fpga).

- •Раздел 8

- •Индикаторы.

- •Глава 1

- •Виды индикаторов.

- •Малогабаритные лампочки накаливания

- •Расчет транзисторного ключа

- •Глава 2 Газоразрядные индикаторы.

- •Глава 3 Светодиодные индикаторы.

- •Глава 4 Жидкокристаллические индикаторы.

- •Принципы работы жидкокристаллических индикаторов

- •Режимы работы жидкокристаллических индикаторов

- •Параметры жидкокристаллических индикаторов

- •Формирование цветного изображения

- •Формирование напряжения для работы жидкокристаллического индикатора

- •Глава 5 Динамическая индикация.

- •Раздел 9

- •Синтезаторы частоты.

- •Глава 1

- •Цифровой фазовый детектор.

- •Глава 2 Фазовый компаратор.

- •Глава 3 Цепи фазовой автоподстройки частоты.

- •Глава 4 Умножители частоты

- •Глава 5 Частотный детектор, построенный на основе фапч

- •Раздел 10

- •Особенности аналого-цифрового и цифро-аналогового преобразования.

- •Глава 1

- •Квантование аналогового сигнала по времени

- •Глава 2 Погрешности дискретизатора

- •Погрешность хранения

- •Погрешность выборки

- •Глава 3 Фильтры устранения эффекта наложения спектров (Антиалайзинговые фильтры)

- •Глава 4 Дискретизация сигнала на промежуточной частоте (субдискретизация)

- •Глава 5 Параллельные ацп (flash adc)

- •Глава 6 Последовательно-параллельные ацп

- •Глава 7 ацп последовательного приближения (sar adc)

- •Глава 8 Сигма-дельта ацп

- •Глава 9 Цифроаналоговые преобразователи (цап) с суммированием токов

- •Глава 10 Цифроаналоговые преобразователи r-2r

- •Раздел 11

- •11.1 Основные блоки цифровой обработки сигналов

- •Глава 1 Двоичные сумматоры

- •Глава 2 Умножители

- •Глава 3 Постоянные запоминающие устройства.

- •Глава 4 Цифровые фильтры.

- •11.2 Микросхемы прямого цифрового синтеза радиосигналов.

- •Глава 5 Фазовые аккумуляторы

- •Глава 6 Полярные модуляторы

- •Глава 7 Квадратурные модуляторы.

- •Глава 8 Интерполирующие цифровые фильтры.

- •Глава 9 Однородные интерполирующие цифровые фильтры.

- •Микросхемы цифрового приема радиосигналов

- •Глава 10 Квадратурные демодуляторы.

- •Глава 11 Децимирующие цифровые фильтры.

- •Децимирующий фильтр с конечной импульсной характеристикой

- •Глава 12 Однородные децимирующие цифровые фильтры.

- •Раздел 12 Примеры реализации цифровых устройств

- •12.1 Электронные часы

- •Разработка структурной схемы

- •Глава 2 Разработка принципиальной схемы

- •Глава 3 Разработка принципиальной схемы индикации часов

- •12.2 Последовательные порты

- •Глава 4

- •Глава 5

Синхронный rs триггер

Схема RS триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется опасные гонки), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены.

Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Для того чтобы отличать от них рассмотренные ранее варианты (RS триггер и триггер Шмитта) эти триггеры получили название асинхронных.

Формировать синхронизирующие сигналы с различной частотой и скважностью при помощи генераторов и одновибраторов мы уже научились в предыдущих главах. Теперь научимся записывать в триггеры входные логические сигналы только при наличии разрешающего сигнала.

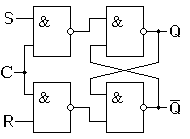

Для этого нам потребуется схема, пропускающая входные сигналы только при наличии синхронизирующего сигнала. Такую схему мы уже использовали при построении схем мультиплексоров и демультиплексоров. Это логический элемент "И". Триггеры, записывающие сигналы только при наличии синхронизирующего сигнала называются синхронными. Принципиальная схема синхронного RS-триггера приведена на рисунке 2.5.

Рисунок 2.5.

Схема синхронного RS триггера,

построенного на элементах "И-НЕ".

Рисунок 2.5.

Схема синхронного RS триггера,

построенного на элементах "И-НЕ".

В таблице 2.2 приведена таблица истинности синхронного RS триггера. В этой таблице символ x означает, что значения логических уровней на данном входе не важны. Они не влияют на работу триггера.

Таблица 2.2 Таблица истинности синхронного RS триггера.

|

С |

R |

S |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

x |

0 |

0 |

Режим хранения информации |

|

0 |

x |

x |

1 |

1 | |

|

1 |

0 |

0 |

0 |

0 |

Режим хранения информации |

|

1 |

0 |

0 |

1 |

1 | |

|

1 |

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

|

1 |

0 |

1 |

1 |

1 | |

|

1 |

1 |

0 |

0 |

0 |

Режим записи нуля R=1 |

|

1 |

1 |

0 |

1 |

0 | |

|

1 |

1 |

1 |

0 |

* |

R=S=1 запрещенная комбинация |

|

1 |

1 |

1 |

1 |

* |

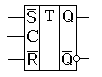

Как мы уже показали выше, RS триггеры могут быть реализованы на различных логических элементах. При этом логика работы синхронных RS триггеров не изменяется. В то же самое время триггеры часто выпускаются в виде готовых микросхем (или реализуются внутри БИС в виде готовых модулей), поэтому на принципиальных схемах синхронные триггеры обычно изображаются в виде условно-графических обозначений. Условно-графическое обозначение синхронного RS триггера приведено на рисунке 2.6.

Рисунок 2.6.

Условно-графическое обозначение

синхронного RS триггера.

Рисунок 2.6.

Условно-графическое обозначение

синхронного RS триггера.

Глава 3 d триггеры, работающие по потенциалу (статические d триггеры)

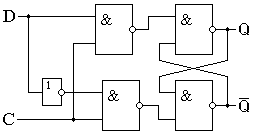

В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Как мы уже видели ранее, сигналы установки и сброса триггера не могут появляться одновременно, поэтому можно объединить эти входы при помощи инвертора, как показано на рисунке 1.

Рисунок 3.1.

Схема D триггера (защелки).

Рисунок 3.1.

Схема D триггера (защелки).

Такой триггер получил название D триггер. Название D триггера происходит от английского слова delay — задержка. Конкретное значение задержки определяется частотой следования импульсов синхронизации. Условно-графическое обозначение D триггера на принципиальных схемах приведено на рисунке 2.

Рисунок 3.2.

Условно-графическое обозначение

D триггера (защелки).

Рисунок 3.2.

Условно-графическое обозначение

D триггера (защелки).

Таблица истинности D триггера достаточно проста, она приведена в таблице 1. Как видно из этой таблицы, этот триггер способен запоминать по синхросигналу и хранить один бит информации.

Таблица 3.1. Таблица истинности D триггера.

|

С |

D |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

0 |

0 |

Режим хранения информации |

|

0 |

x |

1 |

1 | |

|

1 |

0 |

x |

0 |

Режим записи информации |

|

1 |

1 |

x |

1 |

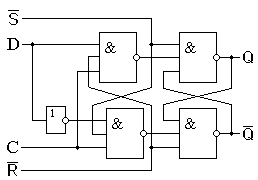

Нужно отметить, что в ТТЛ микросхемах самый распространённый элемент — это "2И-НЕ". Принципиальная схема D триггера на элементах "2И-НЕ" приведена на рисунке 3.3.

Рисунок 3.3

Принципиальная схема D триггера на

элементах "2И-НЕ".

Рисунок 3.3

Принципиальная схема D триггера на

элементах "2И-НЕ".

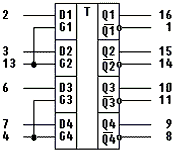

Подобные статические триггеры применяются очень часто. В качестве примера можно назвать микросхемы 555ТМ5 и 555ТМ7 (74ALS75). На подобных триггерах- защелках реализована микросхема 8-ми разрядного параллельного регистра 1533ИР33. Пример цоколевки микросхемы 555ТМ7 приведен на рисунке 3.4.

Рисунок 3.4.

Цоколевка 4-х статических D-триггеров

1533ТМ7 (74ALS75).

Рисунок 3.4.

Цоколевка 4-х статических D-триггеров

1533ТМ7 (74ALS75).

В данном условно-графическом обозначении микросхемы К555ТМ7 входы синхронизации обозначены G от английского слова gate — затвор. В микросхеме размещены одновременно четыре статических триггера. При этом входы синхронизации у каждой пары (G1 и G2), (G3 и G4) оьбъединены в один вывод.

Расширить функциональные возможности синхронных триггеров можно добавлением асинхронных потенциальных входов. На практике чаще всего добавляют асинхронные потенциальные входы S и R записи в триггер логического нуля и единицы. Для этого в схеме статического триггера, приведенной на рисунке 3 добавим еще один вход в логических элементах "2И-НЕ", как это показано на рисунке 4.

Рисунок 3.5.

Схема статического D-триггера с

дополнительными входами R и S.

Рисунок 3.5.

Схема статического D-триггера с

дополнительными входами R и S.

Условно-графическое изображение этого триггера приведено на рисунке 3.6.

Рисунок 3.6.

Условно-графическое статического

D-триггера с дополнительными входами R

и S.

Рисунок 3.6.

Условно-графическое статического

D-триггера с дополнительными входами R

и S.

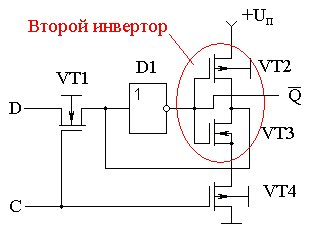

Ещё проще реализуется D триггер на КМОП логических элементах. В КМОП микросхемах вместо логических элементов "И" используются обычные транзисторные ключи. Схема D триггера приведена на рисунке 3.7.

Рисунок 3.7.

Схема D триггера, реализованная на

КМОП элементах.

Рисунок 3.7.

Схема D триггера, реализованная на

КМОП элементах.

При подаче высокого уровня синхросигнала C МОП-транзистор VT1 открывается и обеспечивает передачу сигнала с входа D на инверсный выход Q через инвертор D1. Транзистор VT2 при этом закрыт и отключает второй инвертор, собранный на транзисторах VT2 и VT3. При подаче низкого потенциала на вход C включается второй инвертор, который вместе с инвертором D1 и образует D триггер.

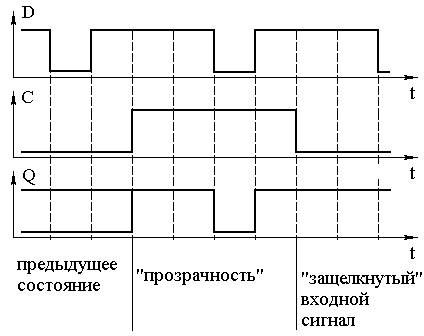

Во всех рассмотренных ранее схемах синхронных триггеров синхросигнал работает по уровню, поэтому триггеры называются триггерами, работающими по уровню или статическими триггерами. Ещё одно название статических D триггеров, пришедшее из иностранной литературы — триггеры-защёлки (latch). Легче всего объяснить появление этого названия по временной диаграмме, приведенной на рисунке 3.8.

Рисунок 3.8.

Временная диаграмма статического

D триггера (защелки).

Рисунок 3.8.

Временная диаграмма статического

D триггера (защелки).

Для формирования подобной временной диаграммы уже недостаточно механических ключей на входе схемы и логических пробников на светодиодах. Для формирования входных сигналов потребуются генераторы импульсов, а для наблюдения временных диаграмм к выходу схемы следует подключить многоканальный осциллограф.

По временной диаграмме, приведенной на рисунке 8 видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера.

Входное напряжение запоминается в статическом D триггере только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы "защелкиваются" в этот момент, отсюда и название — триггер-защелка.

Принципиально в схеме статического D триггера входной переходной процесс (опасные гонки) может беспрепятственно проходить на выход D триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту.