- •Cодержание

- •Задание 1.1.10,10

- •Условие задачи

- •Краткие теоретические сведения

- •Синтез принципиальной схемы

- •Задание 1.2.6,101

- •Условие задачи

- •Краткие теоретические сведения

- •Синтез принципиальной схемы

- •Задание 1.3.2,л

- •Условие задачи

- •Краткие теоретические сведения

- •Синтез принципиальной схемы

- •Задание 1.4.7,д

- •Условие задачи

- •Краткие теоретические сведения

- •Синтез принципиальной схемы

- •Задание 1.5.11

- •Условие задачи

- •Краткие теоретические сведения

- •Синтез принципиальной схемы

- •Элементная база

- •Микросхема кр1533ла3

- •Микросхема кр1533ла4

- •Микросхема кр1533лр11

- •Микросхема кр1533кп2

- •Микросхема кр1533тв9

- •Микросхема кр1533ле1

- •Микросхема кр1554тм8.

- •Микросхема к555им6

- •Микросхема к555кп16

- •Заключение

- •Список используемых источников

- •Приложение а

Задание 1.3.2,л

Условие задачи

На базе двух JK-триггеров одной ИМС КР1533ТВ9 и логических элементах той же серии построить генератор чисел 8-2-5-11.

Краткие теоретические сведения

Триггер является элементом хранения информации, который широко применяется при построении счетчиков, регистров и других устройств памяти. Одним из наиболее важных свойств триггера является его способность устанавливать состояние своего выхода в одно из двух возможных состояний, которые могут быть представлены как логические нуль и единица. В соответствие с этим состояние триггера может рассматриваться как бит информации.

Триггер — цифровой автомат, имеющий два устойчивых состояния равновесия, 0 или 1.

Состояние

триггера распознается по его входному

сигналу. Под влиянием входного сигнала

триггер скачкообразно переходит из

одного устойчивого состояния в другое,

при этом скачкообразно изменяется

уровень напряжения его выходного

сигнала. Для удобства использования в

схемах вычислительных устройств триггеры

обычно имеют два выхода: прямой Q ( «выход

1») и инверсный

(«выход 0»). В единичном состоянии триггеры

на выходе Q имеют высокий уровень сигнала,

а в нулевом — низкий. На выходе

(«выход 0»). В единичном состоянии триггеры

на выходе Q имеют высокий уровень сигнала,

а в нулевом — низкий. На выходе наоборот.

наоборот.

Если хотя бы с одного входа информации в триггер заносится принудительно под воздействием синхронизирующего сигнала, то триггер называется синхронизируемым (синхронным). Если занесение информации в триггер с любого входа производится без синхронизирующего сигнала, то триггер называется несинхронизируемым (асинхронным).

Состояние

триггера определяется сигналом Q на

прямом выходе триггера (или сигналом

на его инверсном выходе).

на его инверсном выходе).

Законы функционирования триггеров задаются таблицами переходов с компактной записью, при которой в столбце состояний может быть указано, что новое состояние совпадает с предыдущим либо является его отрицанием.

Синтез принципиальной схемы

Построим таблицу истинности JK-триггера.

Таблица 3.1 – Таблица состояний JK- триггера

|

J |

K |

|

|

0 |

0 |

|

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

|

Построим таблицу JK-триггера, гдеQ1Q2 будут состояния двухJK-триггеров, аJ1 иK1,J2иK2 - переменные, которые нужно подать на входы триггера, чтобы получить нужное нам состояние.

Выбираем последовательность состояний 00- 01- 10- 11- 00…

Таблица 3.2 – Таблица входных переменных JK-триггера

|

Q1 |

Q2 |

J1 |

K1 |

J2 |

K2 |

|

0 |

0 |

0 |

X |

1 |

X |

|

0 |

1 |

1 |

X |

X |

1 |

|

1 |

0 |

X |

0 |

1 |

X |

|

1 |

1 |

X |

1 |

X |

1 |

Из таблицы 3.2 видно, что J2=K2=1, а дляJ1,K1cтроим карты Карно, чтобы их минимизировать, принимаяXкак любой уровень сигнала.

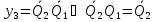

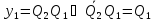

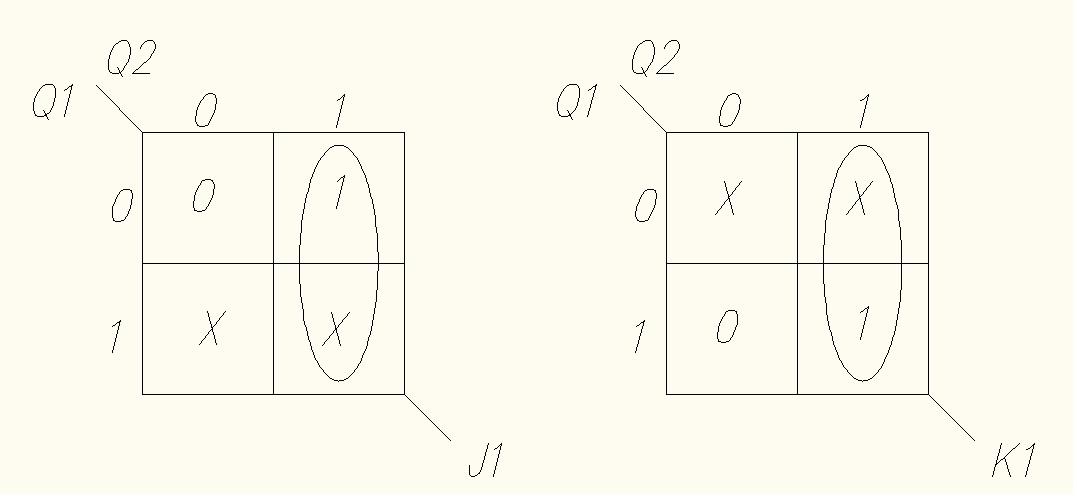

Рисунок 1.3.1 - Карты Карно для J1 иK1

Из карт Карно получим, что J1=K1=Q2.

Для построения

генератора нужна последовательностная

схема на 4 состояния (два триггера), к

выходам которой подключается выходная

логика, имеющая четыре выхода

,

, ,

, ,

, ,

так как для кодирования числа 11

необходимо четыре двоичных разряда.

Четыре состояния можно получить по

схеме регистра сдвига, суммирующего

счетчика, вычитающего счетчика или

пересчетного устройства, обеспечивающего

любую заданную последовательность

состояний. Выберем схему вычитающего

двухразрядного счетчика. Выходы

,

так как для кодирования числа 11

необходимо четыре двоичных разряда.

Четыре состояния можно получить по

схеме регистра сдвига, суммирующего

счетчика, вычитающего счетчика или

пересчетного устройства, обеспечивающего

любую заданную последовательность

состояний. Выберем схему вычитающего

двухразрядного счетчика. Выходы определим из таблицы 3.2.

определим из таблицы 3.2.

Таблица 3.2 – Таблица выходов счетчика

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

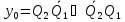

Построим и

минимизируем функции

,

, ,

, ,

, .

.

|

|

(3.1) (3.2) (3.3) (3.4) |

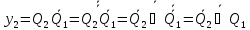

Поскольку было

решено реализовать схему на элементах

ИЛИ-НЕ, избавимся от конъюнкции в функциях

,

используя законы де Моргана и двойного

отрицания:

,

используя законы де Моргана и двойного

отрицания:

|

|

(3.5) (3.6) |

Для реализации такой последовательности нам понадобятся микросхемы КР1533ТВ9 (по условию) и КР1533ЛЕ1.

Электрическая принципиальная схема генератора чисел представлена на чертеже БГУИ.431239.003 Э3 приложения A.

Параметры используемых микросхем в пунктах 6.5 и 6.6.

(t+1)

(t+1) (t)

(t)