Uchebnik_kolosnitsin_v2_5

.pdf

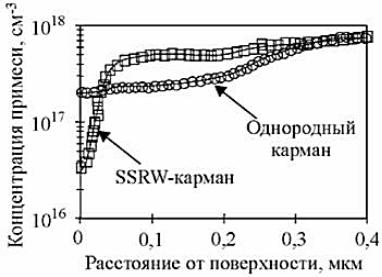

Рисунок 4.32 – Крутое ретроградное распределение примеси

Следующей проблемой является обеспечение малого порогового напряжения, которое, наряду с напряжением питания, ограничивает динамический диапазон аналоговой схемы. Это требование вступает в противоречие с противоположным требованием со стороны цифровых схем, для которых пороговое напряжение определяет запас помехоустойчивости и подпороговый ток, а следовательно, потребляемую мощность в режиме покоя. Для аналоговых схем подпороговый ток не влияет на энергопотребление, так как ток покоя в них обычно задаѐтся генераторами тока. Кардинальным решением этой проблемы является усложнение техпроцесса, которое позволяет делать МОПТ с разными пороговыми напряжениями на одном кристалле. Этого можно добиться или добавлением к стандартному процессу двух технологических операций для «аналоговых» транзисторов: селективное травление окислов и последующая эпитаксиальное наращивание нелегированного кремния или применение двух материалов затвора с разными работами выхода для разных транзисторов, например, поли-SiGe и поли-Si.

В связи с низкой себестоимостью технологии цифровых СБИС и наличием хорошо отработанной инфраструктуры автоматизированного проектирования и производства, обеспечивающей быстрый выход изделий на рынок, представляет особый интерес применение технологий цифровых СБИС для разработки и производства аналоговых схем. Однако такое применение наталкивается на ряд проблем: количество доступных активных и пассивных элементов довольно ограничено, технология оптимизирована только по двум критериям: быстродействие и потребляемая мощность, активные элементы контролируются только на основе простых тестов, таких как задержка вентиля и нагрузочная способность. Тем не менее, этот подход считается перспективным, и предпринимаются шаги по его развитию.

141

4.4 Физические и конструктивно-технологические ограничения при проектировании маломощных МОПТ

В табл. 4.2приведены факторы, ограничивающие масштабирование ряда параметров МОП транзисторов

Таблица 4.2 – Физические ограничения масштабирования МОПТ

Параметр |

Физическое ограничение |

Минимальная величина одного |

Статистические флуктуации легирования |

элемента, 0,03 нм |

подложки, разрешение фоторезиста, |

|

космические лучи и радиоактивность, |

|

конечная ширина p-n перехода |

Минимальное напряжение |

Тепловой потенциал kT/q |

питания 0,025 В |

|

Минимальная плотность тока, |

Дискретность заряда электрона, |

10-6 А/см2 |

флуктуации встроенного заряда |

Минимальная мощность, 10-12 |

Шумы, тепловая энергия, диэлектрическая |

ВТ/элемент при f=1 кГц |

постоянная |

Предельное быстродействие, |

Скорость света |

0,03 нс |

|

Минимальная толщина |

Туннельные токи через диэлектрик |

подзатворного диэлектрика |

|

Максимальное напряжение |

Пробой подзатворного диэлектрика, |

питания |

смыкания областей истока и стока |

Максимальное легирование |

Туннельный пробой p-n перехода стока |

подложки |

|

Максимальная плотность тока |

Электромиграция, падения напряжения на |

|

паразитных сопротивлениях контактов |

Максимальная мощность |

Теплопроводность подложки и |

|

компонентов схемы |

Количество элементов на |

Совокупность всех ранее перечисленных |

кристалл, 109 |

ограничений |

Квантовый теоретический предел на нижнюю границу мощности информационного сигнала проистекает из фундаментального принципа неопределенности Гейзенберга. Применительно к микроэлектронике его можно переформулировать следующим образом: для того, чтобы иметь возможность измерить энергию (мощность) переключения с временем продолжительностью t , величина энергии должна быть больше, чем соотношение h / t , а именно:

P |

h |

, |

(4.73) |

|

|

||||

( t)2 |

||||

|

|

|

где h – постоянная Планка.

142

Фундаментальный предел на основе электромагнитной теории в нашем случае приводит к ограничению скорости распространения высокочастотного импульса по межсоединению до его величины, меньшей чем скорость света в свободном пространстве (С0):

L |

C0 , |

(4.74) |

|

|

|||

|

|

где L – длина критического межсоединения БИС;

τ – время передачи сигнала по этому межсоединению.

Если говорить о материалах и их предельных свойствах, то можно отметить основные характеристики полупроводникового материала, которые определяют свойства созданного прибора, это: подвижность носителей (µ), скорость насыщения носителей (Vs), напряженность электрического поля самоионизации (Ес) и теплопроводность ( ).

Еще одной причиной, мешающей дальнейшему уменьшению размеров транзисторов, является квантово-механическая природа инверсионного слоя, которая не позволяет электронам располагаться непосредственно у поверхности кремния. Максимум пространственного распределения электронов находится на расстоянии 1 нм от поверхности. Это увеличивает эффективную толщину окисла примерно на 0,3 нм. Кроме того, вследствие ограниченной концентрации примеси в поликремниевом затворе в нем наступает режим обеднения, из-за которого увеличивается эффективная толщина подзатворного слоя диэлектрика. Общее увеличение эффективной толщины составляет около 0,7 нм, что уменьшает ток стока и нагрузочную способность транзистора.

Теоретический расчет предельного значения энергии переключения P и времени переключения t с учетом предельных параметров полупроводниковых материалов, которые не зависят от структуры и геометрии приборов, в конкретном практическом приложении дал величину отношения P/t для кремния 0,21 Вт/нс, а для аресенида галлия – 0,69 Вт/нс. Это показывает, что в то время, как GaAs имеет преимущество по быстродействию по сравнению с кремнием, он должен отводить тепла в три раза больше при том же времени переключения.

И. наконец, фундаментальное ограничение (по материалу межсоединений) проистекает из соображений конечной скорости света (с0). Время распространения сигнала через межсоединение длиной L материала с относительной диэлектрической постоянной должно удовлетворять очевидному соотношению

td |

|

L |

|

|

. |

(4.75) |

|

|

|

|

|

||||

|

|

|

|

||||

c0 |

/ |

|

|||||

|

|

|

|

На уровне приборно-технологического представления межсоединения БИС могут моделироваться как каноническая распределенная сеть «сопротивление – емкость». Когда такая сеть управляется идеальным источником напряжения, который формирует функцию одиночной ступеньки, то 90 % времени переключения сети характеризуется выражением

143

RC Rs CsL2, |

(4.76) |

где Rs – поверхностное сопротивление проводника, в Омах на квадрат; Cs – поверхностная емкость, в фарадах на см2;

L – длина межсоединения.

Это выражение характеризует ограничение минимального времени отклика межсоединения при заданной длине.

Немаловажной проблемой являются межсоединения. При технологии 0,25 мкм только 20% задержек в БИС определяются затворами МОПТ, а 80% - межсоединениями (табл. 1.3). Для технологии 0,18 мкм задержка даже в медных линиях связи сравнялась с задержкой в вентилях.

Таблица 4.3– Задержки в транзисторе и линиях межсоединений интегральных микросхем

Технология |

Задержка в |

Задержка в линии |

|

транзисторе, пкс |

межсоединений, Lint =1 мм |

||

|

|||

1,0 мкм (Al,SiO2) |

≈20 |

≈1 |

|

100 нм (Cu) |

≈5 |

≈30 |

|

35 нм (Сu) |

≈2,5 |

≈250 |

В последние годы масштабирование, или увеличение плотности размещения элементов микросхем, решили определять по шагу затвора МОПТ. К 2024 году, согласно ITRS, он должен составить 15 нм (табл. 1.4.)

Таблица 4.4–Изменение характеристик МОПТ в соответствии с ITRS

Параметр |

|

Годы |

|

||

2015 |

2018 |

2020 |

2024 |

||

|

|||||

Шаг затвора, нм |

42 |

30 |

24 |

15 |

|

Длина затвора Lз, нм |

17 |

13 |

13 |

7 |

|

Размер контактов истока и стока, нм |

13 |

9 |

7 |

4 |

|

Сопротивление исток/сток открытого МОПТ, мОм |

140 |

130 |

120 |

110 |

|

Напряжение питания, В |

0,81 |

0,73 |

0,68 |

0,6 |

|

Пороговое напряжение, В |

0,21 |

0,21 |

0,22 |

0,23 |

|

Ток стока в режиме насыщения, мкА/мкм |

3000 |

2720 |

2733 |

2812 |

|

Емкость затвора, фФ/мкм |

0,5 |

0,42 |

0,37 |

0,28 |

|

Поверхностная концентрация носителей заряда в |

7,3 |

7,1 |

6,4 |

5,1 |

|

канале, *1012 см -2 |

|

|

|

|

|

Эффективная скорость дрейфа носителей заряда, |

2,6 |

2,3 |

2,6 |

3,5 |

|

*105 мс-1 |

|

|

|

|

|

144

Контрольные вопросы

1.Почему этот тип транзисторов называют «полевым» или «униполярным»?

2.По каким признакам классифицируют полевые транзисторы?

3.Как моделируется сопротивление каналов в канальных и МОП транзисторах?

4.В чем заключается идеализация МОПТ?

5.Какие зарядовые состояния на границе Si-SiO2 вы знаете?

6.Что влияет на величину порогового напряжения МОПТ? Как млжно ее регулировать?

7.Что влияет на частотные свойства МОПТ?

8.Почему МОПТ с самосовмещенным затвором более высокочастотные?

9. Какие |

критерии, разграничивают |

МОПТна длинно- |

и |

короткоканальные? |

|

|

|

10.Что такое «DIBL эффект»? |

|

|

|

11.За счет |

какой составляющей величины |

порогового напряжения |

его |

значение уменьшается в короткоканальных МОПТ?

12.Почему подвижность носителей в канале является одним из основных параметров МОПТ?

13.Какие существуют методы увеличения подвижности в МОПТ?

14.Для чего производят подлегирование канала МОПТ?

15.В чем заключается «эффект паразитного биполярного транзистора» в короткоканальных МОПТ?

16. Какую роль выполняют вcтроенные LDD области в структуре современных МОПТ?

17.Kакие перспективные структуры МОПТвы знаете?

ГЛАВА 5. Комплементарные МОП схемы

5.1 Общие сведения

Уже на ранних стадиях разработки МОП ИС стало ясно, что в цифровых схемах, выполненных на р- и n- канальных МОП транзисторах, включенных последовательно, можно получить очень малую «статическую» рассеиваемую мощность (мощность в установившемся режиме). Такие схемы называются комплементарными МОП-схемами или просто КМОП-схемами. Чтобы понять, почему в КМОП-схемах рассеиваемая мощность очень мала, рассмотрим основной функциональный блок цифровых схем и систем – инвертор. Инвертор представляет собой схему, выходной (двоичный) сигнал которой есть инверсия его входного сигнала. Соединяя инверторы надлежащим образом, можно строить логические схемы произвольной сложности. Поэтому мощность, потребляемая отдельной инверторной схемой, есть основной показатель общей мощности, которая потребуется для работы цифровой системы.

145

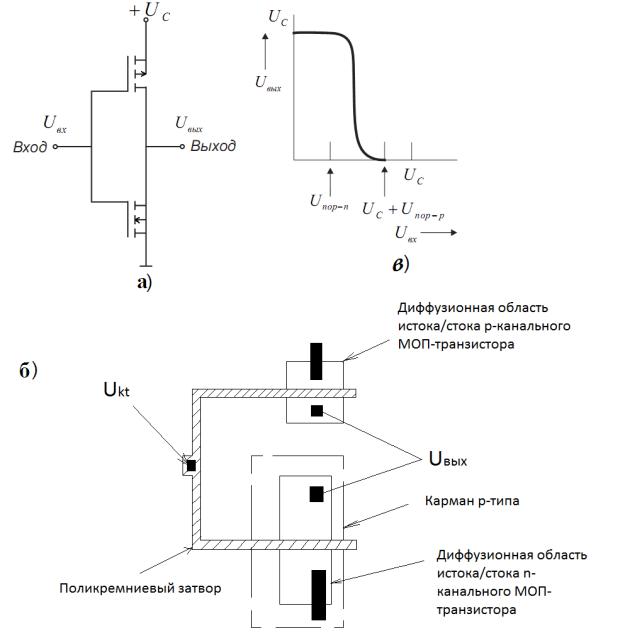

Электрическая схема и топология базового КМОП инвертора показаны на рис. 5.1,а и 5.1,б, а передаточная характеристика по напряжению – на рис. 5.1, в. Последняя представляет собой график зависимости выходного напряжения инверторной схемы от ее входного напряжения. В таком инверторе для МОП транзистора соединены последовательно (сток р-канального транзистора соединен со стоком n-канального), а их затворы соединены друг с другом. Чтобы объяснить работу этого инвертора, допустим, что его входное напряжение ниже порогового напряжения n-канального транзистора и вместе с тем имеет большую отрицательную величину относительно подложки р- канального МОП транзистора, достаточную для его включения.

Рисунок 5.1– а – схема КМОП инвертора, б – передаточная характеристика по напряжению для КМОП инвертора, в – топология КМОП инвертора с карманом р-типа.

В таком режиме р-канальный МОП транзистор образует проводящую цепь между выходом инвертора и источником питания Uc, а n-канальный

146

транзистор выключен. Так как выходной электрод инвертора обычно соединен с входами других инверторных схем, которые не потребляют статического тока, его выходное напряжение (напряжение на стоке р-канального МОП транзистора) находится в своем «высоком» состоянии (равно UВХ ). Если теперь входное напряжение увеличивается, то р-канальный МОП транзистор выключается, а когда входное напряжение становится больше порогового напряжения n-канального прибора, его канал включается и выходное напряжение инвертора уменьшается до напряжения земли. Поэтому в статическом режиме работы тот или другой МОП транзистор инвертора всегда выключен и между источником питания и землей нет цепи для протекания постоянного тока (за исключением лишь токов утечки переходов). По этой причине почти вся мощность, рассеиваемая КМОП схемами, - это мощность, рассеиваемая при переключательных процессах.

Малое потребление мощности в статическом режиме – одно из существенных преимуществ КМОП схем перед цифровыми МОП ИС других типов. Другие их преимущества – крутая и четко определенная передаточная характеристика КМОП инверторов по напряжению (рис. 5.1,в), что облегчает построение цифровых схем и устройств, и высокая помехоустойчивость благодаря малому сопротивлению между выходом логического сигнала и шиной питания или земли. Эти преимущества КМОП схем были известны и понятны задолго до того, как удалось успешно решить значительно более сложные технологические проблемы производства КМОП ИС.

5.2 Особенности проектирования КМОП схем с технологической нормой более 0,25мкм

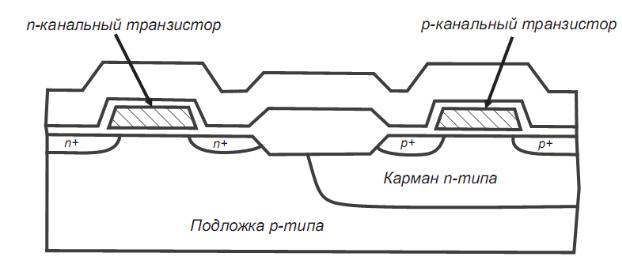

Главный принцип КМОП технологии состоит в том, чтобы выполнить на одном кристалле как n-, так и р-канальные МОП транзисторы, поэтому на поверхности пластины требуется иметь области как р-, так и n-типа. Если ИС изготавливается на подложке n-типа и ее р-канальные транзисторы изготавливаются непосредственно в подложке, то для изготовления n- канальных МОП транзисторов в местах их расположения необходимо сформировать диффузионные области р-типа (сделать так называемые карманы р-типа). КМОП ИС можно также делать на пластинах р-типа, формируя в них карманы n-типа. Сечение пары КМОП транзисторов на подложке с карманами n-типа показано на рис. 5.2.

Оба конструктивных варианта КМОП схем – с карманами n- и р-типа – имеют свои достоинства и свои недостатки, поэтому ни один из них пока не завоевал однозначного преимущества при производстве КМОП схем. Например, при проектировании следует учитывать, что изготавливаемый в кармане транзистор делается в компенсированном кремнии, в котором из-за более высокой полной примесной концентрации падение подвижности носителей оказывается больше, чем в приборах, изготовленных непосредственно в подложке.

147

Рисунок 5.2– Сечение запоминающего КМОП элемента с карманом n-типа

Желательно, чтобы выходные управляющие токи n-канальных и р- канальных МОП транзисторов были примерно равны, поэтому с данной точки зрения предпочтительнее структура с карманами р-типа, так как подвижность электронов выше подвижности дырок. Однако это различие в подвижности можно скомпенсировать, изменив ширину канала транзистора, так как из других соображений более предпочтительной может оказаться структура с карманами n-типа. Особенно это важно если значительная часть логических схем (для адресации, чтения и записи), располагаемых на периферии КМОП ИС памяти, строится на n-канальных транзисторах, именно по этим соображениям, например, выбраны карманы n-типа для КМОП структуры, показанной на рис.

5.2.

Чтобы обеспечить оптимальные характеристики КМОП схем, пороговые напряжения МОП транзисторов обоих типов проводимости должны быть антисимметричны (т.е.Vтр = - Vтn). Применение ионного легирования для подгонки пороговых напряжений позволило решить эту задачу на практике. Дальнейшие замечания относительно КМОП-технологии будут приведены после обсуждения некоторых соображений по проектированию приборов и схем при создании КМОП ИС.

В любой КМОП технологии по крайне мере один тип МОП транзисторов делается в карманах, поэтому две области объемного заряда – одна, связанная с переходами исток – карман и сток – карман, другая, связанная с переходами карман – подложка, - могут смыкаться друг с другом и вызывать сквозное обеднение по вертикали. В качестве конкретного примера рассмотрим КМОП технологию с карманами n-типа, для которой исток р-канального МОП транзистора и карман электрически соединены с положительным полюсом источника питания. Подложка ИС находится при потенциале земли. Поэтому в области кармана эти две обедненные области распространяются навстречу друг другу. Падение потенциала на переходе исток – карман равно всего лишь

148

контактной разности потенциалов перехода k , тогда как на переход карман –

подложка дополнительно действует напряжение смещения Uс. Чтобы избежать отбора больших токов из истоковой области, соответствующая нейтральная область (а следовательно, и глубина кармана n-типа) должна быть достаточных размеров, исключающих сквозное обеднение между истоком и подложкой. Однако эта глубина не должна быть и слишком большой, так как

горизонтальная диффузия примеси n-типа на стадии |

разгонки |

примеси |

вызывает непроизводительное расходование ценной |

площади |

схемного |

кристалла ИС. Концентрацию примеси n-типа в кармане можно увеличить и тем самым уменьшить ширину обедненных областей и избежать сквозного обеднения, однако это приведет к уменьшению подвижности носителей в канале и увеличению паразитной емкости стока. Следствием станет снижение быстродействия при переключении схемы. Для оптимального проектирования конструкции и технологии изготовления КМОП-схемы необходимо тщательно подобрать и сбалансировать все эти факторы.

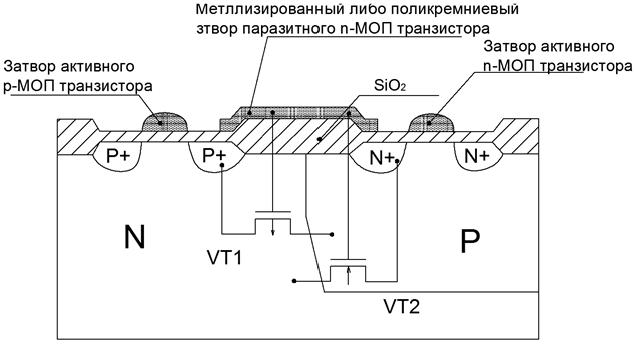

5.3Паразитные транзисторные структуры

ВКМОП БИС паразитные МОП-транзисторы могут быть сформированы между активными МОП-транзисторами разных типов проводимости. Паразитные структуры такого типа представленына рис.5.3. В этом случае исток паразитного p-МОП транзистора образован p+-областью активного p- МОП транзистора, а его сток — p-карманом активного n-МОП транзистора. Исток паразитного n-МОП транзистора образован n+-областью активного n- МОП транзистора, а его сток — n-подложкой схемы. Затворы паразитных транзисторов образованы металлизированным либо поликремниевым

межсоединением на изолирующем окисле SiO2 между активными p-МОП транзисторами. Поскольку концентрации примесей в областях таких паразитных транзисторов существенно различаются, такие структуры являются ассиметричными. Влияние таких структур проявляется в образовании каналов проводиости между областями активных p- и n-МОП транзисторов. Так,

полагая, что на n-подложку подано напряжение высокого уровня ~Uc, а p- карман — нулевой потенциал, паразитный p-МОП транзистор будет способствовать передаче нулевого потенциала на p-область активного p-МОП

транзистора, а паразитный n-МОП транзистор – потенциала ~Uc на n+-область активного n-МОП транзистора. Полагая, что p+- и n+-области являются стоками p- и n- МОП транзисторов логического элемента (ЛЭ), такие каналы при включении активных транзисторов будут изменять уровн напряжений на активных транзисторах, что будет эквивалентно потере логического состояния ЛЭ и отказу БИС в целом. Помимо функционального отказа, этот тип паразитной структуры будет проявляться в большом статическом токе потребления стока.

Поскольку данные паразитные структуры практически устранить нельзя, основными методами ослабления ее величины является повышение пороговых

напряжений n-МОП и p-МОП транзисторов до уровня, значительно

149

превышающего максимально допустимые уровни напряжении в БИС. Это достигается увеличением толщины изолирующего окисла и повышеним конценитрации примесей p+-типа в карман и n+-типа в область под изолирующимокислом.

Рисунок 5.3– Структура паразитного МОП-транзистора.

Наличие в КМОП схемах n-и p-канальных МОП транзисторов обуславливает появление в структуре двух типов паразтных биполярных транзисторов p-n-p и n-p-n(рис.5.3). Биполярный транзистор p-n-p типа образован p+ областью (исток p-канального МОП транзистора), n--областью (база — подложка КМОП схемы) и p--облстью (коллектор — карман КМОП схемы), а вертикальный n-p-n транзистор образован n+-областью (эмиттер — исторк n-канального транзистора), p--областью (база — карман КМОП схемы) и n--областью (коллектор — подложка КМОП схемы). Видно, что эти транзисторы соединены друг с другом по схеме: база n-p-n транзистора соединениа с коллектором p-n-p транзистора, а база n-p-n транзистора с коллектором p-n-p транзистора. Транзисторы, образуя общий коллекторный переход. Следовательно, получится одна из разновидностей схем с положительной обратной связью — тиристорная структура. И если в какой-то момент времени по входу (выходу) работающей схемы приложить напряжение, превышающее значение напряжения питания (+Uc) или меньшее, чем на общей шине –Uc, то в результате регенеративного срабатывания биполярных структур между источником питания и общим выводом образуется фиксированная низкоомная проводимая нить, приводящая к резкому скачку тока потребления. При этом микросхема не реагирует на управляющее воздействие (не выполняет систему команд), даже если дестабилизирующие факторы, вызывающие перевод микросхемы в этот режим устранены. Такое состояние КМОП-схем

150