- •Реверсивные «бегущие огни»

- •1 Анализ исходного устройства.

- •1.1 Анализ исходной схемы.

- •1.2 Анализ элементной базы

- •2. Синтез схемы на базе плис

- •2.1 Реализация исходной элементной базы и синтез схемы на плис

- •2.2 Выбор микросхемы плис

- •2.3 Уровни реализации структуры плис

- •2.4 Назначение выводов плис

- •2.5 Расчет энергопотребления с помощью утилиты xPower

- •Vertex4

1 Анализ исходного устройства.

1.1 Анализ исходной схемы.

Схема

устройства состоит из генератора на

элементахDD1.1,DD1.2

и транзистореVT1, буферный

элементDD1.3, счетчикDD2,

набор инверторов-повторителейDD4.1-DD4.4,

узел управления ими (DD1.4,DD3.1) и дешифраторDD5,

к выходам которого подключены светодиодыHL1-HL16.

Тактовые импульсы с выхода генератора,

собранного на элементахDD1.1,DD1.2 и транзистораVT1,

через буферный элементDD1.3

поступают на вход С1 счетчикаDD2.

Его выходные сигналы подаются на входы

микросхемыDD4. Она

представляет собой четыре независимых

элемента “Исключающее ИЛИ” и работает

по следующему алгоритму: если на обоих

входах элемента присутствуют одинаковые

логические сигналы, то на выходе элемента

– лог. 0, а если разные – лог. 1. В данном

случае элементы микросхемыDD4

выполняют функции управляемых инверторов

–повторителей: в зависимости от уровня

напряжения на объединенных входах они

либо “пропускает” сигналы с выходов

счетчикаDD2 на входы

дешифратораDD5 напрямую,

либо инвертируют их, за счет чего и

происходит смена направления переключения

светодиодовHL1-HL16

гирлянды. ЭлементамиDD4

управляет триггерDD3.1,

включенный делителем на 2 (входDсоединен с инверсным выходом). С приходом

на его вход С каждого импульса с выхода

8 счетчикаDD2 триггер

изменяет сове состояние на противоположное

и происходит смена направления

переключения светодиодовHL1-HL16.

Схема

устройства состоит из генератора на

элементахDD1.1,DD1.2

и транзистореVT1, буферный

элементDD1.3, счетчикDD2,

набор инверторов-повторителейDD4.1-DD4.4,

узел управления ими (DD1.4,DD3.1) и дешифраторDD5,

к выходам которого подключены светодиодыHL1-HL16.

Тактовые импульсы с выхода генератора,

собранного на элементахDD1.1,DD1.2 и транзистораVT1,

через буферный элементDD1.3

поступают на вход С1 счетчикаDD2.

Его выходные сигналы подаются на входы

микросхемыDD4. Она

представляет собой четыре независимых

элемента “Исключающее ИЛИ” и работает

по следующему алгоритму: если на обоих

входах элемента присутствуют одинаковые

логические сигналы, то на выходе элемента

– лог. 0, а если разные – лог. 1. В данном

случае элементы микросхемыDD4

выполняют функции управляемых инверторов

–повторителей: в зависимости от уровня

напряжения на объединенных входах они

либо “пропускает” сигналы с выходов

счетчикаDD2 на входы

дешифратораDD5 напрямую,

либо инвертируют их, за счет чего и

происходит смена направления переключения

светодиодовHL1-HL16

гирлянды. ЭлементамиDD4

управляет триггерDD3.1,

включенный делителем на 2 (входDсоединен с инверсным выходом). С приходом

на его вход С каждого импульса с выхода

8 счетчикаDD2 триггер

изменяет сове состояние на противоположное

и происходит смена направления

переключения светодиодовHL1-HL16.

1.2 Анализ элементной базы

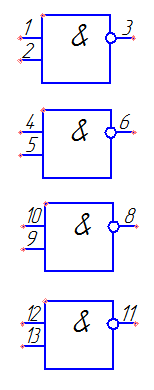

КР1533ЛА3 – микросхема представляющая 4 логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ:

Рис.1 – Условное графическое изображение КР1533ЛА3

Функции выводов микросхем:

− 1,2,4,5,9,10,12,13 - входы;

− 3,6,8,11 - выходы;

− 7 - “земля”;

− 14 - питание.

КР1533ИД3 – дешифратор, имеющий 4 адресных входа, 2 инверсных входа стробирования, 16 выходов.

Рис.2 – Условное графическое изображение КР1533ИД3

Функции

выводов микросхемы:

Функции

выводов микросхемы:

− 23,22,21,20 – адресные входы;

− 18, 19 – входы стробирования;

− 1-12,14-17 – выходы;

− 13 – питание;

− 24 - “Земля”.

КР1533ИЕ5 – счетчик с максимальным коэффициентом пересчета 16.

Рис.3 – Условное графическое изображение КР1533ИЕ5.

Функции выводов микросхемы:

− 1,14 – входы для счетных импульсов;

− 2,3 – входы для сброса счетчика;

− 8,9,11,12 – выходы.

КР1533ТМ2 – D-триггер со сбросом и предустановкой.

Рис.4 – Условное графическое изображение КР1533ТМ2

Функции

выводов микросхемы:

Функции

выводов микросхемы:

− 1,4 – входы установки триггера в единичное, либо в нулевое состояние;

− 2 – вход установки триггера по тактовым импульсам входа С;

− 3 – вход тактовых импульсов;

− 5,6 – выходы триггера.

КР1533ЛА3 – микросхема содержащая 4 логических элемента 2И-НЕ

Рис.5 – Условное графическое изображение КР1533ЛА3

Функции выводов микросхемы:

− 1,2,4,5,10,9,12,13 – входы;

− 3,6,8,11 – выходы;

− 7 - “земля”;

− 14 - питание.

2. Синтез схемы на базе плис

2.1 Реализация исходной элементной базы и синтез схемы на плис

Для реализации исходной электрической схемы устройства и его функций на ПЛИС, необходимо заменить имеющуюся элементную базу на стандартные компоненты библиотеки XilinxISE, либо описать работу элементов в программном модулеVHDLMODULE.

Согласно алгоритму работы, устройство должно последовательно, поочередно зажигать светодиоды так, чтобы после последнего 16-го включенного светодиода процесс поочередного включения светодиодов шел в обратном направлении. При анализе исходной схемы были обнаружены ошибки в ее построении, из-за которых принцип работы схемы не соответствовал изначальному требованию. Модификация схемы коснулись кодовой комбинации, снимаемой со счетчика на вход триггера – основываясь заявленному алгоритму работы, кодовая комбинация должна включать все четыре разряда, что обеспечивает число 16, а не 8, как представлено в схеме журнала. В связи с этим, для переключения триггера по 16-му импульсу был использован логический элемент И, содержащий четыре инверсных входа и один выход. Вид переработанной схемы в XilinxISEпредставлен на рис. 6.

Рис.6 –

Синтезированная схема в XilinxISE

В

синтезированной схеме использовались

библиотечные компоненты и компоненты

написанные наVHDL. Из

стандартных компонентов использовались

элементыXOR2, заменяющие

логические элементы “искл. ИЛИ”DD4, а так же триггерFDcоединенным инверсным

элементом, заменяющим триггерDD3.1.

Логический элемент “И-НЕ”DD1.4

был заменен на логический элемент И с

четыремя инверсными входами.

В

синтезированной схеме использовались

библиотечные компоненты и компоненты

написанные наVHDL. Из

стандартных компонентов использовались

элементыXOR2, заменяющие

логические элементы “искл. ИЛИ”DD4, а так же триггерFDcоединенным инверсным

элементом, заменяющим триггерDD3.1.

Логический элемент “И-НЕ”DD1.4

был заменен на логический элемент И с

четыремя инверсными входами.

Элемент XOR2 выполняет функцию “искл. ИЛИ”. Условно-графическое изображение вXilinxISEпредставлено на рис.7. Временная диаграммы работы на рис.8.

Рис.7 – Условно-графическое изображение элемента “искл. ИЛИ”.

Рис.8 – Временная диаграмма работы “искл. ИЛИ”.

Данный элемент используется в схеме с целью инвертирования входной последовательности кодов со счетчика на дешифратор: после того как его значение достигнет 16, сигнал с триггера активирует этот логический элемент и произойдет инверсия кодовой послежовательности.

Триггер FDcвыходом подключенным на вход данных через инверсный элемент выполняет функцию триггераDD3, который включен в режиме Т-триггера: меняет свое состояние по фронту тактового импульса. Условно-графическое изображение вXilinxISEпредставлено на рис.9. Временная

диаграммы работы на рис.10.

диаграммы работы на рис.10.

Рис.9 – Условно-графическое изображение триггера.

Рис.10 – Временная диаграмма работы триггера.

Элемент AND4B4 инверитрует входящие сигналы и выдает на выходе сигнал являющийся результатом логической операции “И”. Условно-графическое изображение вXilinxISEпредставлено на рис.11. Временная диаграммы работы на рис.12.

Рис.11 – Условно-графическое изображение логического элемента “И” c4-мя инверсными входами.

Рис.12 – Временная диаграмма работы логического элемента “И” c4-мя инверсными входами.

Элемент DD22 написан на языкеVHDL. Он представляет собой счетчик, аналогичный счетчикуDD2. По фронту тактового импульса выдает на выходе счетное число импульсов в двоичном коде. Коэффициент пересчета равен 16. Код счетчика наVHDL:

ibrary IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity DD22 is

Port ( C1 : in STD_LOGIC;

C_OUT : out STD_LOGIC_VECTOR (3 downto 0));

end DD22;

architecture Behavioral of DD22 is

begin

process (C1)

variable count : integer range 0 to 31:=0;

begin

if C1='1' and C1'event then

case

count is

case

count is

when 0 => C_OUT <= "0000";

when 1 => C_OUT <= "0001";

when 2 => C_OUT <= "0010";

when 3 => C_OUT <= "0011";

when 4 => C_OUT <= "0100";

when 5 => C_OUT <= "0101";

when 6 => C_OUT <= "0110";

when 7 => C_OUT <= "0111";

when 8 => C_OUT <= "1000";

when 9 => C_OUT <= "1001";

when 10 => C_OUT <= "1010";

when 11 => C_OUT <= "1011";

when 12 => C_OUT <= "1100";

when 13 => C_OUT <= "1101";

when 14 => C_OUT <= "1110";

when 15 => C_OUT <= "1111";

when others => C_OUT <= "0000";

end case;

count := count + 1;

end if;

if count=16 then count:=0;

end if;

end process;

Условно-графическое изображение в XilinxISEпредставлена на рис.11. Временная диаграммы работы на рис.12.

Рис.13 – Условно-графическое изображение счетчика.

Рис.14 – Временная диаграмма работы счетчика.

ЭлементDD5VHDнаписан

также на языкеVHDL,

представляет собой дешифратор на 16 с

инверсными выходами. Код на

языке VHDL:

ЭлементDD5VHDнаписан

также на языкеVHDL,

представляет собой дешифратор на 16 с

инверсными выходами. Код на

языке VHDL:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity DD5VHD is

Port ( A : in STD_LOGIC_VECTOR (3 downto 0);

D : out STD_LOGIC_VECTOR (15 downto 0);

E : in STD_LOGIC);

end DD5VHD;

architecture Behavioral of DD5VHD is

begin

process (E,A)

begin

if ( E = '1') then

case A is

when "0000" => D <= "1111111111111110";

when "0001" => D <= "1111111111111101";

when "0010" => D <= "1111111111111011";

when "0011" => D <= "1111111111110111";

when "0100" => D <= "1111111111101111";

when "0101" => D <= "1111111111011111";

when "0110" => D <= "1111111110111111";

when "0111" => D <= "1111111101111111";

when "1000" => D <= "1111111011111111";

when "1001" => D <= "1111110111111111";

when "1010" => D <= "1111101111111111";

when "1011" => D <= "1111011111111111";

when "1100" => D <= "1110111111111111";

when "1101" => D <= "1101111111111111";

when "1110" => D <= "1011111111111111";

when "1111" => D <= "0111111111111111";

when others => D <= "1111111111111111";

end case;

end if;

end process;

Условно-графическое изображение в XilinxISEпредставлена на рис.13. Временная диаграммы работы на рис.14.

Рис.15 – Условно-графическое изображение дешифратор.

Рис.16 – Временная диаграмма работы дешифратора.

Используя совокупность выбранных элементов, собранных в единую схему в XilinxISE, удалось получить ее временные диаграммы работы. Она представлена на рис.16.

Рис.16 – Временная диаграмма работы всего устройства.