- •Электронный конспект лекций по курсу «Системы ввода - вывода и интерфейсы»

- •Глава 1. Основные принципы построения систем ввода-вывода и интерфейсов

- •1.1. Роль и место систем ввода-вывода и интерфейсов в компьютере

- •1.2. Основные принципы организации передачи информации в вычислительных системах

- •1.3. Компьютерные коммуникации и интерфейсы

- •1.4. Системные интерфейсы и шины расширения

- •1.5. Интерфейсы периферийных устройств

- •1.6. Структура систем ввода-вывода

- •1.7. Основные функции и принципы построения интерфейсов

- •1.8. Протоколы передачи данных в компьютерных интерфейсах

- •1.8.1. Алгоритмы протоколов передачи данных

- •1.8.2. Протокол параллельных интерфейсов

- •1.8.3. Протоколы последовательных интерфейсов

- •1.8.4. Принципы взаимодействия шин расширения и интерфейсов периферийных устройств

- •Глава 2. Шины расширения

- •2.1. Шина isa

- •2.1.1. Введение

- •2.1.1.1. Виды устройств, работающие на шине isa

- •2.1.1.1. Виды устройств, работающие на шине isa

- •2.1.2. Характеристики задатчиков на шине

- •2.1.2.2. Контроллер пдп

- •2.1.2.3. Внешняя плата

- •2.1.2.4. Режимы прямого доступа к памяти или к устройствам ввода/вывода

- •2.1.2.5. Режим сброса

- •2.1.2.6. Контроллер регенерации памяти

- •2.1.3. Общее описание шины isa

- •2.1.3.2. Адресное пространство для устройств ввода/вывода

- •2.1.3.3. Структура прерываний

- •2.1.3.4. Перестановщик байтов

- •2.1.4. Описание сигналов на шине isa

- •2.1.4.2. Командные сигналы

- •2.1.4.3. Центральные сигналы управления

- •2.1.4.4. Сигналы прерывания

- •2.1.4.5. Сигналы режима пдп

- •2.1.4.6. Питание

- •2.1.5. Циклы шины

- •2.1.5.1. Цикл Доступа к Ресурсу

- •2.1.5.1.1. Цикл Доступа к Ресурсу - 0 тактов ожидания

- •2.1.5.1.2. Цикл Доступа к Ресурсу - Нормальный цикл

- •2.1.5.1.3. Цикл Доступа к Ресурсу - Удлиненный цикл

- •2.1.5.2. Цикл Регенерации - Введение

- •2.1.5.2.1. Цикл Регенерации - Нормальный цикл

- •2.1.5.2.2. Цикл Регенерации - Удлиненный цикл

- •2.1.5.3. Цикл пдп

- •2.1.5.3.1. Цикл пдп - Нормальный цикл

- •2.1.5.3.2. Цикл пдп - Удлиненный цикл

- •2.1.5.4. Цикл Захвата Шины

- •2.2. Шина pci

- •2.2.1. Архитектура шины pci

- •2.2.2. Описание сигналов шины

- •2.2.3. Команды шины

- •2.2.4. Разновидности операций на шине

- •2.2.4.1. Начало и продолжение транзакции

- •2.2.4.2. Окончание транзакции

- •2.2.4.3. Способы завершения транзакций

- •2.2.4.4. Цикл чтения

- •2.2.4.5. Цикл записи

- •2.2.4.6. Арбитрация

- •2.2.4.7. Цикл конфигурации

- •2.3. Шина 3gio и Hyper Transport

- •2.3.1.1. Архитектура 3gio

- •2.3.2.1. Топологии

- •2.3.2.2. Совместимость с шиной pci

- •Глава 3. Интерфейсы периферийных устройств

- •3.1. Параллельный интерфейс: lpt-порт

- •3.1.1. Интерфейс Centronics

- •3.1.2. Традиционный lpt-порт

- •3.1.3. Функции bios для lpt-порта

- •3.1.4. Стандарт ieee 1284-1994

- •3.1.5. Физический и электрический интерфейс

- •3.1.6. Режим ерр

- •3.1.7. Режим еср

- •3.1.8. Конфигурирование lpt-портов

- •3.1.9. Использование параллельных портов

- •3.1.10. Параллельный порт и РпР

- •3.2. Последовательные интерфейсы: com-порт

- •3.2.1. Интерфейс rs-232с

- •3.2.2. Электрический интерфейс

- •3.2.3. Управление потоком передачи

- •3.2.4. Микросхемы асинхронных приемопередатчиков

- •3.3. Интерфейс scsi

- •3.3.1.2.1. Краткий обзор многочисленных разновидностей scsi.

- •3.3.1.2.2. Основные отличия scsi-2 от scsi-1

- •3.3.1.2.3. Быстрее, выше, сильнее

- •3.3.1.4. Совместимость устройств scsi

- •3.3.2. Описание сигналов

- •3.3.2.1. Физический интерфейс

- •3.3.2.2. Фазы шины

- •3.3.2.1. Физический интерфейс

- •3.3.2.2. Фазы шины

- •3.3.3. Описание сообщений и управление интерфейсом

- •3.3.4. Описание команд

- •3.3.4.1. Адресация и система команд

- •3.3.4.2. Выполнение команд

- •3.3.4.1. Адресация и система команд

- •3.3.4.2. Выполнение команд

- •3.3.5. Типы пу

- •3.3.5.1. Устройства прямого доступа (0)

- •3.3.5.2. Устройства последовательного доступа (1)

- •3.3.5.3. Принтеры (2)

- •3.3.5.4. Процессорными устройствами (3)

- •3.3.5.5. Устройства однократной записи (4)

- •3.3.5.6. Приводы cd-rom (5)

- •3.3.5.7. Сканеры (6)

- •3.3.5.8. Устройства оптической памяти (7)

- •3.3.5.9. Устройства смены носителей (8)

- •3.3.5.10. Коммуникационные устройства (9)

- •3.3.6. Конфигурирование устройств scsi

- •3.3.6.1. Хост-адаптер scsi

- •3.3.6.1. Хост-адаптер scsi

- •3.4. Интерфейс usb

- •3.4.1. Общая информация

- •3.4.2. Обзор архитектурыch2

- •3.4.2.1. Структура системы usb

- •3.4.2.1.1. Топология шины

- •3.4.2.2. Устройства usb

- •3.4.2.2.2. Функция

- •3.4.2.3. Физический интерфейс

- •3.4.2.3.1. Электрические характеристики

- •3.4.2.3.2. Механические характеристики

- •3.4.3. Модель передачи данныхch3

- •3.4.3.1. Конечные точки устройств usb

- •3.4.3.2. Каналы

- •3.4.3.2.1. Потоки

- •3.4.3.2.2. Сообщения

- •3.4.3.3. Типы передачи данных

- •3.4.4. Протоколch4

- •3.4.4.1. Форматы полей пакетов

- •3.4.4.1.1. Поле синхронизации

- •3.4.4.1.2. Поле идентификатора пакета

- •3.4.4.2.2. Маркер начала кадра (sof)

- •3.4.4.2.3. Пакет данных

- •3.4.4.2.4. Пакет подтверждения

- •3.4.4.3. Типы транзакций

- •3.4.4.3.1. Сплошные передачи

- •3.4.4.3.2. Управляющие посылки

- •3.4.4.3.3. Прерывания

- •3.4.4.3.4. Изохронные передачи

- •4.1.1.1.Структурная схема таймера

- •4.1.1.2. Назначение входов и выходов бис

- •4.1.1.3. Назначение блоков и сокращения, используемые в окне иммитационной модели таймера

- •4.1.2. Программирование таймера

- •4.1.3. Режимы работы таймера

- •4.1.3.1. Режим 0 - прерывание терминального счета

- •4.1.3.2. Режим 1 - программируемый ждущий мультивибратор

- •4.1.3.3. Режим 2 - импульсный генератор частоты

- •4.10. Функционирование таймера в режиме 2

- •4.1.3.4. Режим 3- генератор меандра

- •4.11. Функционирование таймера в режиме 3

- •4.1.3.5. Режим 4 - программно-формируемый строб

- •4.1.3.6. Режим 5 - аппаратно-формируемый строб

1.8. Протоколы передачи данных в компьютерных интерфейсах

1.8.1. Алгоритмы протоколов передачи данных

в начало

Управление передачей информации при выполнении процессов ввода или вывода с помощью того или иного стандартного интерфейса (шины) осуществляется посредством специальных команд или циклов шины (интерфейса). Каждая команда интерфейса реализуется по определенным правилам, называемыми протоколами интерфейса. Эти протоколы регламентируются стандартом соответствующего интерфейса и должны выполняться независимо от типа компьютера или периферийного устройства. За одну команду от источника к приемнику передается одна порция или блок информации, имеющих определенную структуру.

Несмотря на большое разнообразие интерфейсов, их протоколы строятся на основе достаточно общего алгоритма процесса передачи данных или алгоритма взаимодействия задатчика (устройства-инициализатора) и исполнителя (целевого устройства).

Прежде чем рассматривать алгоритмы процессов передачи информации на шине, определим основные состояния, в которых может находиться интерфейс.

Шина может находиться в двух главных состояниях:

состояние холостого хода (Idle State), когда шина свободна и по ней нет передачи информации;

активное состояние, когда шина занята текущим задатчиком, и идет процесс передачи данных между ним и соответствующим исполнителем.

Если состояние холостого хода одно, активных состояний может быть несколько, и они определяются теми этапами передачи данных, с помощью которых реализуется процесс чтения или записи информации.

Следует подчеркнуть, что новый задатчик может захватывать шину только тогда, когда ее освободит текущий задатчик, и шина будет находиться в состоянии холостого хода.

Состояние холостого хода и активное состояние задают определенным набором управляющих сигналов или определенным физическим состоянием линии передачи данных.

Процесс передачи информации на шине состоит из двух основных этапов: этап захвата шины и этап передачи информации от источника к приемнику.

На первом этапезадатчик должен захватить шину. Алгоритм захвата состоит из следующих шагов:

1. Задатчик подает запрос арбитру на захват шины.

2. Арбитр через определенное время (задержка арбитрации tзарб), которое в основном зависит от уровня приоритета задатчика, выдает задатчику разрешение на захват шины.

3. Задатчик, получив разрешение, через время tЗШ, захватывает шину в момент, когда текущий задатчик освобождает шину, и она переходит в состояние холостого хода.

На втором этапеидет собственно передача информации под управлением задатчика, т.е. на этом этапе задается вид команды и способ ее выполнения.

Процесс ввода/вывода может реализоваться как в режиме программного ввода/вывода, так и в режиме прерываний (см. §1.2). В том и другом случаях управление процессом передачи информации осуществляет задатчик (активное устройство).

Алгоритм передачи при программном вводе/выводе включает в себя выполнение следующих шагов:

1. Задатчик в начале передачи данных выставляет специальный сигнал занятости шины.

2. Задатчик устанавливает адрес исполнителя.

3. Задатчик устанавливает код (сигнал) соответствующей команды.

4. Когда задатчик и исполнитель готовы, начинается передача данных, передача идет слово за словом. В параллельном интерфейсе разряды слова передаются параллельно, в последовательном – разряд за разрядом.

5. После передачи последнего слова в блоке данных задатчик заканчивает процесс передачи информации и шина переходит в состояние холостого хода.

Алгоритм передачи при режиме прерываний отличается тем, что инициатором процесса ввода/вывода является исполнитель (периферийное устройство). Причем задатчик может работать сразу с несколькими ПУ. Если задатчик получил одновременно несколько запросов от разных ПУ, то он проводит селекцию и идентификацию устройства с наибольшим приоритетом и начинает работать с ним по вышеописанному алгоритму. Т.е. предварительно задатчик по требованию исполнителей выполняет шаг селекции и идентификации (см. §1.7), а затем уже переходит к процессу передачи данных в соответствии с вышеизложенным алгоритмом.

Первый и второй этапы имеют определенные протоколы их реализации.

Как правило, протоколы первого этапа и протокол шага селекции и идентификации второго этапа достаточно просты и являются одинаковыми для всех задатчиков и не зависит от типа команд интерфейса.

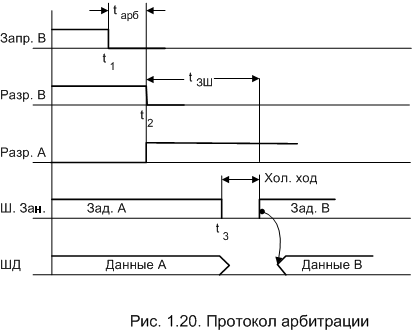

На рисунке 1.20 показан протокол захвата шины задатчиком В при условии, что на шине уже работает текущий задатчик А. В момент t1 задатчик В подает арбитру запрос на захват шины. Арбитр сбрасывает разрешение для задатчика А и устанавливает в момент t2 разрешение для задатчика В. В момент t3 задатчик А освобождает шину, и она переходит в состояние холостого хода, после чего задатчик В захватывает шину и начинает передачу информации.

Линии запроса и разрешения, которые идут к арбитру от всех задатчиков, могут реализоваться либо в виде отдельных проводников, либо с использованием линий шины адреса/данных. В первом случае этап арбитрации может выполняться параллельно с передачей информации, а во втором этап арбитрации должен предшествовать этапу передачи данных.

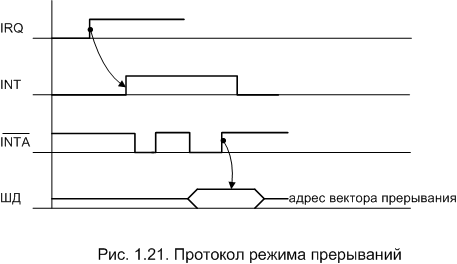

На рисунке 1.21 показан протокол этапа селекции и идентификации при вводе/выводе в режиме прерываний. Он выполняется стандартной микросхемой 8259А программируемого контроллера прерываний фирмы Intel.

Периферийное устройство подает на контроллер прерываний запрос прерывания IRQ, контроллер проводит селекцию (выбор устройства с наибольшим приоритетом) и подает на микропроцессор сигнал INT, запрашивая у микропроцессора разрешение на прерывание.

Микропроцессор разрешает процедуру ввода/вывода в режиме прерываний выдав сигнал разрешения INTA на контроллер прерываний. Сигнал INTA двойной.

По первому импульсу контроллер прерываний фиксирует разрешение на работу, а по второму – выдает на шину данных адрес вектора прерываний, по которому микропроцессор идентифицирует ПУ и передает управление драйверу этого ПУ.

Протоколы второго этапа по передаче информации различаются в зависимости от типа передаваемых данных, архитектуры шины, направления передачи и других характеристик.

Но вместе с тем второй этап характеризуется некоторыми основными принципами его реализации, которые являются общими для многих интерфейсов.

В данном параграфе будут рассмотрены протоколы второго этапа сначала для параллельных, затем последовательных интерфейсов, для операций чтения и записи в синхронном и асинхронном режимах передачи данных, для трехшинной и двухшинной архитектур.

Перед рассмотрением протоколов следует отметить два существенных момента, которые являются общими для всех протоколов и их необходимо учитывать при дальнейших рассмотрениях.

Первый момент заключается в том, что шина работает на определенной частоте, которая задается синхронизирующими импульсами интерфейса (CLK) и все временные параметры шины измеряются количеством импульсов и величиной периода их следования (τ).

Второй момент связан с тем, что протокол команды интерфейса реализуется поэтапно, в виде определенных шагов, в течение которых, как правило, передается или не передается та или иная информация. Эти этапы в параллельных интерфейсах часто называют фазами шины, а в последовательных интерфейсах информацию, передаваемую на каждом этапе, называют пакет.

Совокупность фаз или пакетов одной команды часто называют транзакцией.