- •Проектирование цифрового устройства

- •Предисловие

- •Введение

- •1. Цель и задачи курсового проектирования

- •2. Требования к оформлению курсового проекта

- •3. Общие указания по курсовому проектированию

- •4. Пример выполнения курсовой работы в среде Multisim.

- •4.1. Расчет и синтез схем дсс.

- •4.2. Расчет и синтез счетных схем.

- •4.3. Синтез схемы делителя частоты

- •4.4. Синтез схемы гти.

- •Библиографический список

- •Проектирование цифрового устройства

- •Содержание

4. Пример выполнения курсовой работы в среде Multisim.

Программа Multisim является удобным средством курсового проектирования, так как располагает не только обширной библиотекой компонентов, но и разнообразными инструментами синтеза и анализа работы проектируемых электронных устройств.

Рассмотрим пример построения цифрового устройства (ЦУ), формирующего определенные последовательности кодовых слов размером байт. Последние должны отображаться двумя семисегментными индикаторами в виде двух 16-тиричных символов.

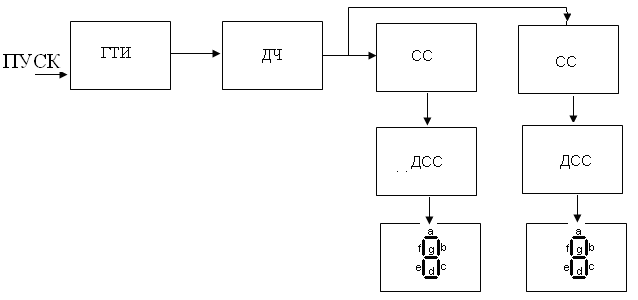

ЦУ состоит из следующих функциональных блоков:

- источник (генератор) цифровых тактовых импульсов (ГТИ);

- делитель частоты (ДЧ);

- счетные схемы (СС);

- дешифраторы состояний счетных схем (ДСС);

- семисегментные индикаторы (СИ).

ГТИ формирует цифровые импульсы заданной частоты f1, поступающие на ДЧ. На выходе ДЧ формируются цифровые импульсы частоты f2 = f1/Кд, где Кд - заданный коэффициент деления частоты f1. С выхода ДЧ импульсы поступают на СС. Схемы СС имеют заданное число состояний. В начальном состоянии в СС записаны нули. С каждым новым импульсом происходит переход СС в следующее определенное состояние, которое отображается на СИ в виде шестнадцатиричных чисел. Для преобразования состояний СС в символы на СИ служит ДСС.

Блок-схема данного ЦУ представлена на рис.1.

Рис.1

На блок-схеме левая цепочка однотипных блоков СС и ДСС служит для преобразования и отображения на СИ кода символа старшего разряда, а правая – младшего.

Пусть заданы 6 состояний СС, в каждом из которых должны последовательно отображаться на СИ следующие шестнадцатеричные числа: 00, 3С, A7, 41, d5, 9 Е.

Расчет и синтез данной схемы ЦУ следует начинать с конца, то есть с расчета схем ДСС.

4.1. Расчет и синтез схем дсс.

Проектирование начнем с ДСС. младшего разряда СИ. На индикаторе младшего разряда в соответствие с заданием должны отображаться следующие числа: 0, С, 7, 1, 5, Е.

Для синтеза схемы ДСС составляется его таблица истинности

(таблица 1). В ней записываются двоичные эквиваленты заданных символов и соответствующие им состояния сегментов СИ: если сегмент должен светиться для отображения данного символа, то в соответствующей клетке записывается 1, если нет, то 0.

В таблице состояние каждого сегмента следует рассматривать как функцию 4-х входных переменных: Х0, Х1, Х2, Х3, так как с помощью 4-х разрядов можно представить исходные 16-тиричные числа.

Таблица 1

|

Номер состояния СС |

Символ на СИ |

Входы ДСС |

Состояние сегментов СИ | |||||||||

|

x3

|

x2

|

x1

|

x0

|

a

|

b

|

c

|

d

|

e

|

f

|

g

| ||

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

1 |

С |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

2 |

7 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

|

3 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

4 |

5 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

5 |

Е |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

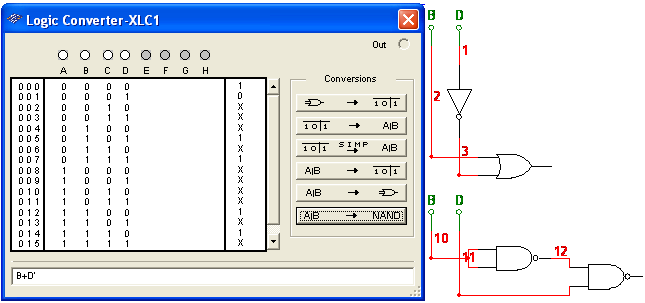

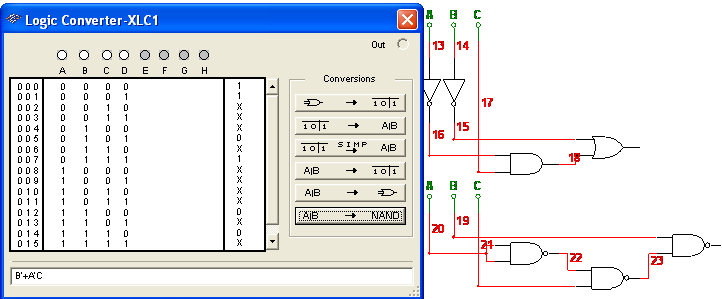

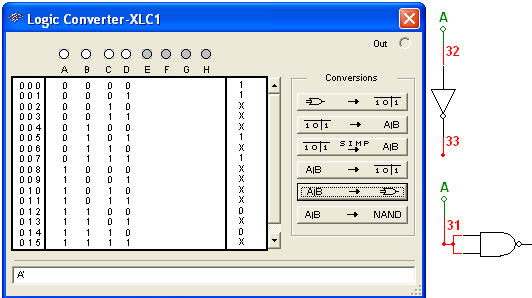

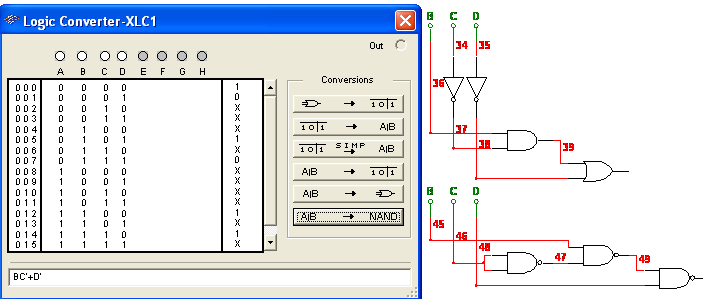

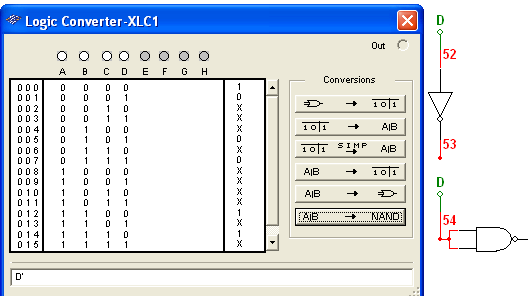

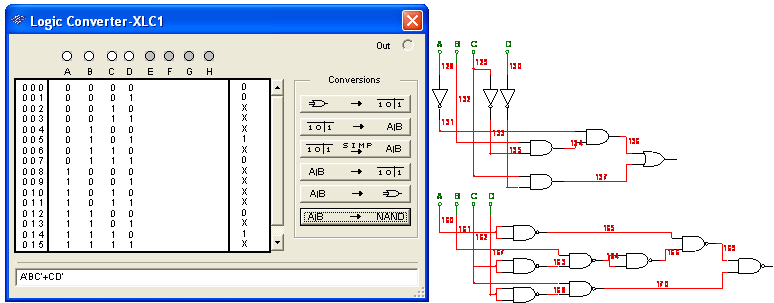

На основе таблицы истинности необходимо выполнить минимизацию указанных функцтй. Обычно это осуществляется с помощью карт Карно или диаграмм Вейча. Более просто эту минимизацию можно выполнить в программе Multisim. Для этого нужно воспользоваться специальным инструментом - логическим преобразователем, позволяющим по таблице истинности получить готовую схему. При этом, в логическом преобразователе переменные A, B, C, D будут соответствововать переменным Х3, Х2, Х1, Х0 таблицы 1. На рис. 2 - 7 показана реализация функций сегментов Fa – Fd, Fе, Fg. Верхняя схема на этих рисунках построена в булевом базисе, а нижняя в базисе И-НЕ. Как видно из таблицы 1 функция Ff и Fd равны. Поэтому, после нажождения Fd функцию Ff получать уже не требуется.

Рис. 2

Рис. 3

Рис.4

Рис.5

Рис.6

Рис.7

Также из таблицы 1 и рис. 4, 6 видно, что Fс= Х’3, а Fе= Х’0 (штрих означает инверсию). То есть для реализации Fс и Fе нужно использовать инверсию переменных, соответственно Х3 и Х0.

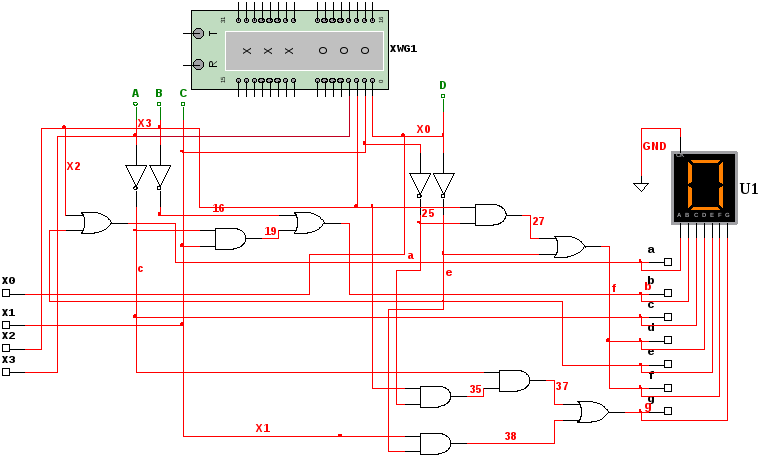

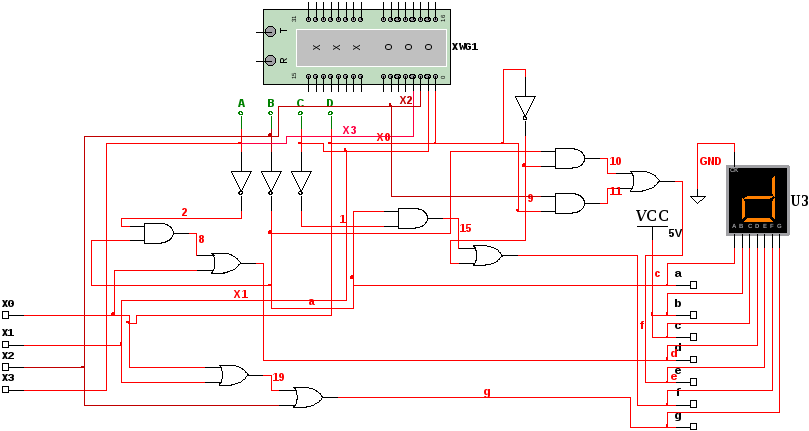

Далее следует объединить схемы всех функций сегментов в одну схему ДСС младшего разряда СИ. На рис. 8 показан пример этой схемы в булевом базисе. Синтез ДСС в базисе И-НЕ (если требуется по заданию) также не составит труда.

Рис. 8

Для проверки правильности синтеза и работы схемы следует подключить ее входы, например к генератору слов, а к выходам – семисегментный индикатор (группа Indicators, семейство HEX_DISPLAY, компонент SEVEN_SEG_COM_K_ORANGE)..

Синтез ДСС старшего разряда СИ выполняется так же, как и младшего. При этом Fa=Х’2, Fb=Fс=1, Fd=Х’3Х’2+Х0, Fе=Х’2Х’0+ Х2Х0, Ff=Х’2Х’1+Х’0, Fg= Х0+Х1+Х2. Нужно заметить, что случай равенства единице функций сегментов Fb и Fс дает самую легкую схемную их реализацию. Нужно просто подключить сегменты b и с к источнику логической единицы - VCC.

На рис. 9 показан пример схемы ДСС старшего разряда СИ в булевом базисе.

Рис. 9