- •Проектирование цифрового устройства

- •Предисловие

- •Введение

- •1. Цель и задачи курсового проектирования

- •2. Требования к оформлению курсового проекта

- •3. Общие указания по курсовому проектированию

- •4. Пример выполнения курсовой работы в среде Multisim.

- •4.1. Расчет и синтез схем дсс.

- •4.2. Расчет и синтез счетных схем.

- •4.3. Синтез схемы делителя частоты

- •4.4. Синтез схемы гти.

- •Библиографический список

- •Проектирование цифрового устройства

- •Содержание

4.2. Расчет и синтез счетных схем.

Счетчики разрабатываемого ЦУ должны строиться по принципу синхронных счетных схем, позволяющих организовать переход счетчика в заданное состояние. Для синтеза таких схем обычно составляют таблицы переходов. На рис. 10 представлена сокращенная подобная таблица проектируемой счетной схемы младшего разряда.

Из таблицы видно, что состояния D-входов триггеров счетной схемы соответствуют последующим состояниям выходов. В этом случае при переходе СС в новое состояние на его выходах будут формироваться кодовые слова, соответствующие заданным символам на СИ.

Синтез функций D-входов выполняется так же, как и функций сегментов в ДСС. Следует учесть, что если для синтеза с помощью логического преобразователя используются 4 переменные A,B,C,D, то они должны соответствовать переменные Q3, Q2, Q1, Q0.

Рис. 10

В итоге получим FD0= Q’2 Q0+Q’3 Q1+Q3Q’1, FD1= Q2Q’1, FD2= Q’1,

FD3= Q’3 Q’0 + Q’3Q2Q’1.

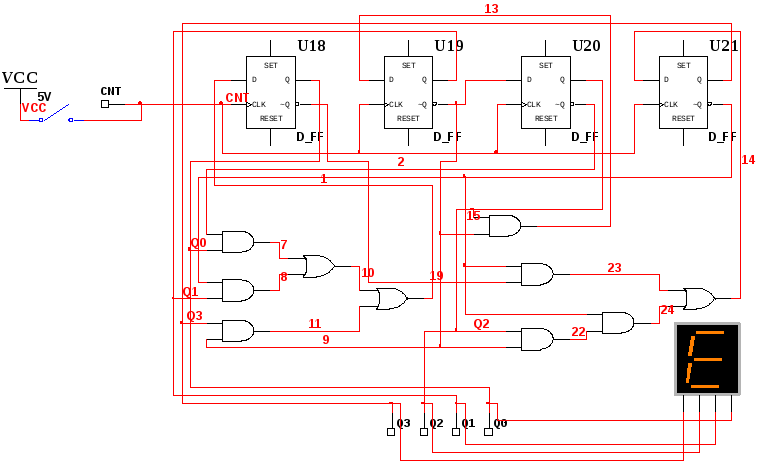

На рис.11 показана готовая счетная схема младшего разряда. На рисунке видно, что для реализации функций D-входов в комбинационной части схемы используются прямые, либо инверсные выходы триггеров.

Рис. 11

Для проверки правильности синтеза, работы и отладки схемы можно подключить ее С-вход к источнику VCC, а к выходам – семисегментный индикатор 16-тиричных слов.

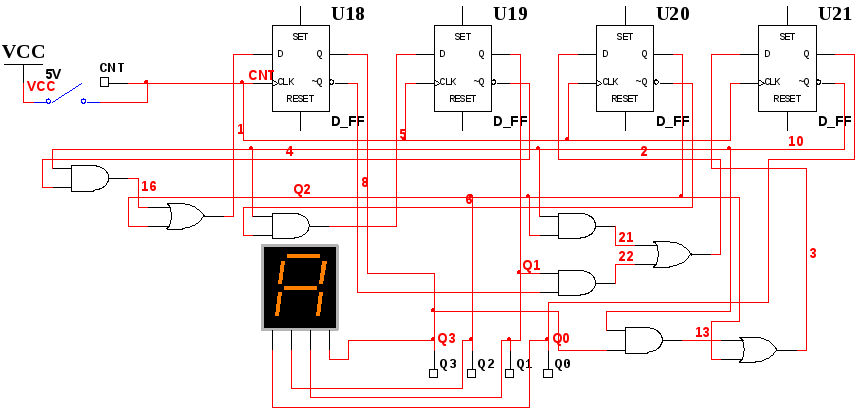

Синтез СС старшего разряда выполняется так же, как и младшего. При этом FD0= Q’3 Q’1+Q2, FD1= Q’3Q’2, FD2=Q’3 Q2 + Q1Q’0,

FD3= Q’3 Q0 + Q2. На рис.12 показана готовая счетная схема старшего разряда CC. Ее так же следует проверить на правильность синтеза и работы.

Рис.12

4.3. Синтез схемы делителя частоты

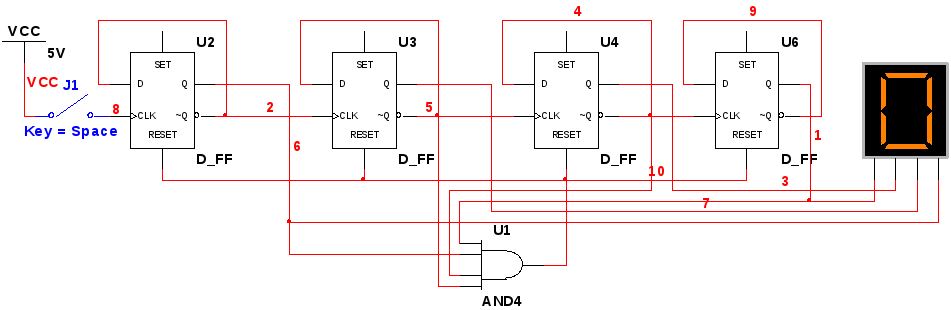

Делитель частоты строится на основе асинхронного двоичного счетчика). Пример схемы делителя частоты с Кд=9 показан на рис.13.

Число разрядов ДЧ можно определить по количеству двоичных разрядов в заданном значении Кд. Так как двоичный код числа 9=1001 состоит из 4-х разрядов, то схема ДЧ строится на 4-х триггерах. Модуль счета n-разрядной асинхронной схемы определяется выражением М=2n.

Рис.13

В проектируемом ДЧ модуль М=24=16, что больше Кд. Поэтому необходимо изменить счет схемы так, чтобы на каждые 9 входных импульсов формировался один выходной. Это можно осуществить с помощью дополнительной комбинационной схемы, которая должна формировать на каждый 9-й входной импульс сигнал сброса всех разрядов ДЧ в исходное нулевое состояние. Для этого можно использовать простую схему совпадения. На рис.13 такой схемой служит ЛЭ типа 4И. Его входы подключены к прямым или инверсным выходам соответствующих разрядов ДЧ в зависимости от состояния выходов. В нашем ДЧ входы схемы совпадения подключены к прямым выходам 0-го и 3-го разрядов, и к инверсным выходам 1-го и 2-го разрядов. В этом случае приход 9-го входного импульса ДЧ вызовет появление всех единиц на указанных выходах, в результате чего на выходе ЛЭ сформируется сигнал логической единицы. Так как выход ЛЭ подключен к R-входам сброса всех триггеров, то на 9-й импульс ДЧ установится в исходное состояние.

В схеме данного ДЧ используются D-триггеры с прямыми R-входами. Если использовать D-триггеры с инверсными R-входами, то нужно учесть, что сброс таких триггеров производится не 1, а 0. В таком случае вместо данного ЛЭ можно взять ЛЭ типа 4И-НЕ, или выход нашей схемы совпадения подключить через инвертор.

Соберите и исследуйте работу схемы делителя частоты по рис. 13. С помощью ключа подавайте входные импульсы и убедитесь, что на 9-й импульс схема устанавливается в нулевое состояние.