- •П.К. Ланге

- •1. Лабораторный практикум по изучению цифровых схем

- •1. Цель работы

- •2. Описание лабораторного макета

- •3. Порядок выполнения работы

- •1. Составить карту Карно.

- •2. Разработать комбинационную схему.

- •3. Собрать схему триггера.

- •6. Cодержание отчета

- •1. Цель работы

- •Типичная временная диаграмма сигналов, действующих на входах d-триггера, приведена на рис. 6, jk-триггера – на рис. 7.

- •Р и с. 15. Схема параллельного регистра

- •2. Описание лабораторного макета

- •3. Порядок выполнения работы

- •4. Содержание отчета

- •1. Цель работы

- •2. Описание лабораторного стенда

- •3. Порядок выполнения работы

- •4. Содержание отчета

- •1. Цель работы

- •. (1)

- •2. Описание лабораторного стенда

- •3. Порядок выполнения работы

- •4. Содержание отчета

- •2. Лабораторный практикум по изучению

- •1. Аппаратная часть микроЭвм

- •2. Математическое обеспечение микроЭвм

- •Распределение адресного пространства памяти

- •Распределение адресного пространства портов ввода-вывода

- •Распределение адресов-векторов прерываний

- •3. Включение микроЭвм

- •4. Ввод программы пользователя с клавиатуры

- •5. Просмотр содержимого памяти микроЭвм

- •6. Пуск программы пользователя

- •7. Отладочный режим

- •8. Режим тактирования

- •9. Режим шаг

- •10. Система команд и рекомендации по составлению программ

- •Система команд микропроцессора кр580ик80а

- •Десятичные числа, их двоичные и шестнадцатеричные эквиваленты

- •Действия команд микропроцессора кр580ик80а

- •Бланк листинга ассемблерной программы

- •Характеристики команд микропроцессора кр580ик80

- •1. Цель работы

- •2. Задания для домашней подготовки

- •3. Задания к лабораторной работе

- •4. Содержание отчета

- •1. Цель работы

- •2. Задания для домашней подготовки

- •3. Задания к лабораторной работе

- •4. Содержание отчета

- •1. Цель работы

- •2. Задания для домашней подготовки

- •Разрешить прерывания Возврат к прерваннойпрограмме

- •3. Задания к лабораторной работе

- •4. Содержание отчета

- •1. Цель работы

- •2. Задания для домашней подготовки

- •8. Подпрограмма muZисполнения мелодии.

- •Коды нот (в шестнадцатеричном формате)

- •3. Задания к лабораторной работе

- •4. Содержание отчета

- •Лабораторная работа мпт-4 “Работа с подпрограммами и стеком” 99

. (1)

При подстановке в выражение значений аргументов определяется значение функции, например, при X1=0, X2=1, X3=1, X4=1 это значение равно

f

(0,1,1,1) = (0+![]() )

(

)

(![]() +1)

+ 1·1·1= (0+0) (1+1) + 1·1 = 0·1+1= 0+1 = 1.

+1)

+ 1·1·1= (0+0) (1+1) + 1·1 = 0·1+1= 0+1 = 1.

Выражение для логической функции можно определить следующим образом, исходя из ее комбинационной таблицы. Для каждого набора переменных, на котором функция равна единице, записывается элементарное произведение всех аргументов, причем если аргумент в этом наборе принимает значение 0, то записывается его инверсия. Выражение для функции определяется логической суммой этих элементарных произведений. Например, функция, заданная в табл. 3, может быть представлена выражением

(2)

(2)

Если функция на всей совокупности наборов переменных принимает нулевое значение меньшее число раз, чем единичное (в столбце комбинационной таблицы число нулей меньше, чем число единиц), то для инверсии функции более компактным выражением будет выражение, составленное аналогичным образом из элементарных произведений аргументов для каждого набора переменных, на котором функция равна нулю. Например, функция, заданная табл. 4, может быть представлена выражением

![]() (3)

(3)

Таблица 3 Таблица 4

|

Номер набора |

Х1 |

Х2 |

Х3 |

Y |

|

Номер набора |

Х1 |

Х2 |

Х3 |

Y |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

2 |

0 |

1 |

0 |

1 |

|

2 |

0 |

1 |

0 |

1 |

|

3 |

0 |

1 |

1 |

0 |

|

3 |

0 |

1 |

1 |

1 |

|

4 |

1 |

0 |

0 |

0 |

|

4 |

1 |

0 |

0 |

0 |

|

5 |

1 |

0 |

1 |

1 |

|

5 |

1 |

0 |

1 |

1 |

|

6 |

1 |

1 |

0 |

0 |

|

6 |

1 |

1 |

0 |

0 |

|

7 |

1 |

1 |

1 |

0 |

|

7 |

1 |

1 |

1 |

1 |

Выражения (2) и (3) могут быть приведены к более компактной форме при использовании теорем алгебры логики. Реализуются они с помощью логических элементов И, ИЛИ, НЕ, обозначения которых на схемах приведены на рис. 1.

Распространение получили также элементы, реализующие комбинированные функции И–НЕ, ИЛИ–НЕ. При объединении входов любой из этих элементов реализует функцию НЕ. Комбинационная таблица для этих функций приведена в табл. 5.

Р и с. 1. Обозначение логических элементов

Таблица 5

|

Х1 |

Х2 |

|

| |||

|

0 |

0 |

1 |

1 | |||

|

0 |

1 |

1 |

0 | |||

|

1 |

0 |

1 |

0 | |||

|

1 |

1 |

0 |

0 | |||

Схема И называется также вентильной, поскольку, как это видно из табл. 1, она пропускает один из сигналов (например, X) на вход (Y = X1) при значении другого сигнала, равном 1, и не пропускает его (Y = 0) при значении другого сигнала, равном 0.

На основе описанных логических схем строятся основные модули цифровой схемотехники – дешифраторы, мультиплексоры, счетчики, регистры.

Дешифраторы

Дешифратор – это схема для преобразования позиционного двоичного кода в унитарный цифровой код. Он реализует таблицу преобразований, например, для трехразрядного двоичного кода (табл. 6).

Таблица 6

|

Х1 |

Х2 |

Х3 |

Y |

|

0 |

0 |

0 |

Y0 |

|

0 |

0 |

1 |

Y1 |

|

0 |

1 |

0 |

Y2 |

|

0 |

1 |

1 |

Y3 |

|

1 |

0 |

0 |

Y4 |

|

1 |

0 |

1 |

Y5 |

|

1 |

1 |

0 |

Y6 |

|

1 |

1 |

1 |

Y7 |

В этой таблице Yi – вывод, на котором действует единичный сигнал при соответствующем наборе переменных.

Как видно из табл. 6, дешифратор реализует функции

![]()

Схема такого дешифратора и его условное изображение представлены на рис. 2.

Р и с. 2. Схема дешифратора и его обозначение

Входы

![]() называют адресными входами, а сигналы,

которые на них поступают, адресными

сигналами, или адресами.

называют адресными входами, а сигналы,

которые на них поступают, адресными

сигналами, или адресами.

Дешифратор используется для реализации произвольной функции алгебры логики. Для этого необходимо использовать схему ИЛИ, входы которой надо соединить с теми выходами дешифратора, на которых действует единичный сигнал при подаче на входы адресов единичных значений логической функции. Например, комбинационная схема, реализующая функцию, заданную табл. 3, изображена на рис. 3. Дешифратор может быть использован также в качестве распределителя сигналов, поскольку при подаче на его входы последовательно увеличивающегося двоичного кода единичный выходной сигнал перемещается в направлении увеличения номера выхода.

Диаграммы сигналов в такой схеме изображены на рис. 4. Двоичный код обычно формируется двоичным счетчиком импульсов C, также изображенных на рис. 4.

Р и с. 3. Комбинационная схема на дешифраторе

Объединяя выходы распределителя с помощью схем ИЛИ, можно создать схему генераторов различных последовательностей сигналов. Одна из схем двухфазного генератора и диаграмма сигналов приведены на рис. 5.

Р и с. 4. Диаграмма сигналов распределителя

Р и с. 5. Схема двухфазного генератора на основе дешифратора и диаграммы сигналов

Мультиплексор

Мультиплексор –

это схема с одним выходом, информационными

и адресными входами. Он передает сигнал

на выход с того входа, номер которого

определяется адресом – двоичным кодом,

действующим на адресных входах. Условное

изображение мультиплексора 8![]() 1,

имеющего информационные входы D0...D7,

адресные входы

1,

имеющего информационные входы D0...D7,

адресные входы

![]() и два выхода – прямой Y и инверсный

и два выхода – прямой Y и инверсный

![]() ,

приведено на рис. 6.

,

приведено на рис. 6.

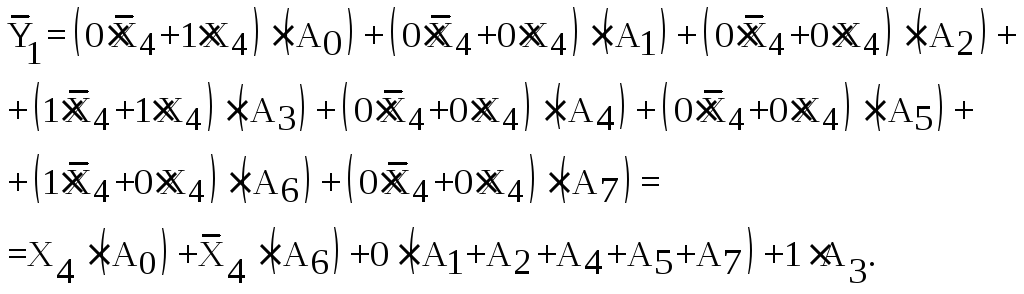

Мультиплексор реализует логическую функцию

(4)

(4)

Сравнение выражений

(4) и (2) показывает, что мультиплексор

можно использовать для реализации

логической функции, если входной сигнал

Di рассматривать

как конкретное значение Y на соответствующем

наборе переменных

![]() .

.

На рис. 7 представлена комбинационная схема, реализующая функцию, заданную в табл. 4.

Р

и с. 6. Мультиплексор Р

и с. 7. Комбинационная схема на

мультиплексоре

.

Для реализации функции от 4 переменных мультиплексор дополняется инвертором для получения инверсии четвертой переменной X4. Например, функция Y, описанная в табл. 7, определяется выражением

(5) ,

где Аi

– переменная, определяемая соответствующим

произведением

![]() :

:

Таблица 7

|

Номер набора |

Х4 |

Х3 |

Х2 |

Х1 |

Y |

Y1 |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

2 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

4 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

|

5 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

|

6 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

|

7 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

|

8 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

|

9 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

10 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

|

11 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

12 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

|

13 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

|

14 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

|

15 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

Можно заметить,

что i– номер набора![]() ,

при котором

,

при котором

![]() .

.

Число iопределяет и номер входа мультиплексора,

на который подается один из сигналов

0,1,![]() в соответствии с выражением (5).

в соответствии с выражением (5).

Схема, реализующая эту функцию, изображена на рис. 8, а.

Если функция

принимает нулевые значения меньшее

число раз, чем единичные, то удобнее

составить выражение для инверсии

функции, как это было сделано при

определении выражения (4), и, соответственно,

использовать инверсный выход

![]() мультиплексора. Функция

мультиплексора. Функция

![]() ,

заданная в правом столбце табл. 8 (отмечен

серым цветом), определяется выражением

,

заданная в правом столбце табл. 8 (отмечен

серым цветом), определяется выражением

Схема, реализующая эту функцию, изображена на рис. 8, б.

Р и с. 8, а. Комбинационная схема на мультиплексоре

Р и с. 8, б. Комбинационная схема на мультиплексоре с инверсным выходом

Триггерные схемы

Регистры памяти и счетчики строятся на основе триггеров. Триггер – это схема с двумя устойчивыми состояниями, кодируемыми цифрами 0 и 1. Обычно считают, что триггер находится в состоянии 1, если сигнал на его выходе Q имеет высокий уровень (единичный сигнал), и в состоянии 0, если сигнал на его выходе имеет низкий уровень (нулевой сигнал).

Триггер имеет информационный (D) и тактовый (С) входы. При поступлении на информационный вход логического сигнала (“0” или “1”) триггер устанавливается в соответствующее состояние и запоминает его, то есть в триггер записывается информация.

Информация может записываться в триггер только при наличии на тактовом входе единичного сигнала (тактового сигнала, или синхросигнала).

Кроме указанных

входов, триггер имеет установочные

входы R и S, которые позволяют устанавливать

триггер в состояние “0” и “1” путем

подачи на эти входы комбинаций сигналов

в соответствии с табл. 8. Как видно из

таблицы, при нулевых сигналах

![]() триггер не меняет своего состояния

триггер не меняет своего состояния

![]() .

.

Таблица 8

|

Rn |

Sn |

Qn+1 |

|

0 |

0 |

Qn |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

|

1 |

1 |

x |

При других комбинациях триггер устанавливается в состояние, соответствующее сигналу на входе S.

Комбинация сигналов

![]()

является запрещенной, при ней триггер устанавливается в неопределенное состояние. Триггер может работать в счетном режиме, когда он пересчитывает по модулю 2 импульсы, поступающие на его тактовый вход (счетный вход). Такие счетные триггеры являются основой различных счетчиков.

Счетчики

Счетчики

бывают суммирующие, вычитающие и

реверсивные, которые могут как суммировать

импульсы, так и вычитать. Они характеризуются

коэффициентом пересчета К

– максимальным количеством сосчитанных

импульсов. Коэффициент К

зависит от числа разрядов счетчика

(каждому разряду соответствует один

триггер). Для n-разрядного

счетчика максимальное его значение

определяется соотношением

![]()

Условное обозначение и диаграммы сигналов суммирующего 4-x разрядного двоичного счетчика представлены на рис. 9.

Можно убедиться, что в интервале времени после i-го входного импульса на выходах счетчика действует двоичный код, соответствующий числу i. Вход R счетчика используется для его сброса в нулевое состояние (очистки). При подаче на R вход логической единицы на выходах счетчика устанавливается нулевой код (0000).

Очевидно, что четырехразрядный счетчик имеет коэффициент пересчета К=24=16.

Р и с. 9. Суммирующий двоичный счетчик. Обозначение и диаграмма напряжений

При поступлении

на вход счетчика импульсов частотой f0

с выходов

![]() снимаются импульсы с частотами

снимаются импульсы с частотами![]() ,

,![]() ,

,![]() ,

,![]() (см. рис. 9).

(см. рис. 9).

Таким образом, счетчик может быть использован в качестве делителя частоты импульсов в 2, 4, 8 и 16 раз.

Регистры памяти

Регистры памяти

также строятся на основе триггеров и

служат для запоминания (записи) двоичного

кода. Регистр, предназначенный для

записи 4-разрядного кода, имеет 4

информационных входа

![]() ,

тактовый входc(синхровход) и четыре выхода

,

тактовый входc(синхровход) и четыре выхода![]() (рис. 10).

(рис. 10).

Р и с. 10. Запоминающий регистр и диаграммы сигналов

После поступления

тактового импульса с

(синхросигнала) регистр запоминает

двоичный код, действующий на входах

![]() непосредственно перед появлением

заднего фронта сихросигнала. Информационные

сигналы на выходах

непосредственно перед появлением

заднего фронта сихросигнала. Информационные

сигналы на выходах![]() регистра появляются в момент заднего

фронта синхросигнала.

регистра появляются в момент заднего

фронта синхросигнала.

Регистры сдвига,

кроме возможности записи кода, имеют

возможность сдвига записанного кода

при поступлении тактового импульса на

отдельный тактовый вход. При сдвиге

кода от младшего разряда к старшему

реализуется выражение

![]() .

В этом случае в младший разряд записывается

информация с отдельного (последовательного)

входа

.

В этом случае в младший разряд записывается

информация с отдельного (последовательного)

входа

![]() .

.

В качестве примера можно привести универсальный регистр сдвига К155ИР1, условное изображение которого приведено на рис. 11. Этот регистр имеет два синхровхода С1 и С2 . Вход V2 служит для управления режимом работы: при V2=1 регистр работает в режиме параллельной записи кода, действующего на входах D1…D4 при наличии синхроимпульса на c1. При этом вход V1 служит для записи с него информации в младший разряд регистра (Q1=V1). При подключении ко входу V1 выхода Q4 получается кольцевой регистр – код, записанный в него, под действием синхроимпульсов, подаваемых на вход c1, циркулирует, последовательно переписываясь с выхода Q4 на вход V1, а параллельный код, записанный в регистр, преобразуется в последовательный и может быть считан, например, с выхода Q4.

Р и с. 11. Универсальный регистр К155ИР1

На основе универсального регистра можно построить различные делители частоты. Для этого входные импульсы необходимо подать на объединенные входы c1,c2, на входV1подать логическую единицу, входV2соединить с одним из выходов регистра. Схемы делителей с различными коэффициентами деления частоты приведены на рис. 12.

Р и с. 12. Схемы делителей частоты на основе универсального регистра К155ИР1