- •П.К. Ланге

- •1. Лабораторный практикум по изучению цифровых схем

- •1. Цель работы

- •2. Описание лабораторного макета

- •3. Порядок выполнения работы

- •1. Составить карту Карно.

- •2. Разработать комбинационную схему.

- •3. Собрать схему триггера.

- •6. Cодержание отчета

- •1. Цель работы

- •Типичная временная диаграмма сигналов, действующих на входах d-триггера, приведена на рис. 6, jk-триггера – на рис. 7.

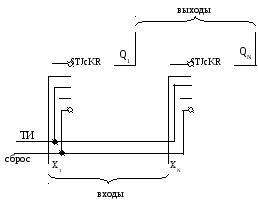

- •Р и с. 15. Схема параллельного регистра

- •2. Описание лабораторного макета

- •3. Порядок выполнения работы

- •4. Содержание отчета

- •1. Цель работы

- •2. Описание лабораторного стенда

- •3. Порядок выполнения работы

- •4. Содержание отчета

- •1. Цель работы

- •. (1)

- •2. Описание лабораторного стенда

- •3. Порядок выполнения работы

- •4. Содержание отчета

- •2. Лабораторный практикум по изучению

- •1. Аппаратная часть микроЭвм

- •2. Математическое обеспечение микроЭвм

- •Распределение адресного пространства памяти

- •Распределение адресного пространства портов ввода-вывода

- •Распределение адресов-векторов прерываний

- •3. Включение микроЭвм

- •4. Ввод программы пользователя с клавиатуры

- •5. Просмотр содержимого памяти микроЭвм

- •6. Пуск программы пользователя

- •7. Отладочный режим

- •8. Режим тактирования

- •9. Режим шаг

- •10. Система команд и рекомендации по составлению программ

- •Система команд микропроцессора кр580ик80а

- •Десятичные числа, их двоичные и шестнадцатеричные эквиваленты

- •Действия команд микропроцессора кр580ик80а

- •Бланк листинга ассемблерной программы

- •Характеристики команд микропроцессора кр580ик80

- •1. Цель работы

- •2. Задания для домашней подготовки

- •3. Задания к лабораторной работе

- •4. Содержание отчета

- •1. Цель работы

- •2. Задания для домашней подготовки

- •3. Задания к лабораторной работе

- •4. Содержание отчета

- •1. Цель работы

- •2. Задания для домашней подготовки

- •Разрешить прерывания Возврат к прерваннойпрограмме

- •3. Задания к лабораторной работе

- •4. Содержание отчета

- •1. Цель работы

- •2. Задания для домашней подготовки

- •8. Подпрограмма muZисполнения мелодии.

- •Коды нот (в шестнадцатеричном формате)

- •3. Задания к лабораторной работе

- •4. Содержание отчета

- •Лабораторная работа мпт-4 “Работа с подпрограммами и стеком” 99

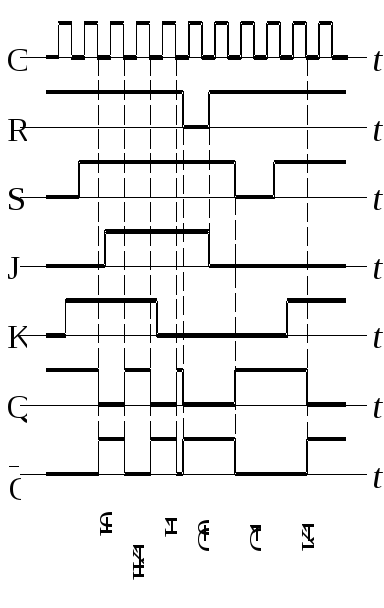

Типичная временная диаграмма сигналов, действующих на входах d-триггера, приведена на рис. 6, jk-триггера – на рис. 7.

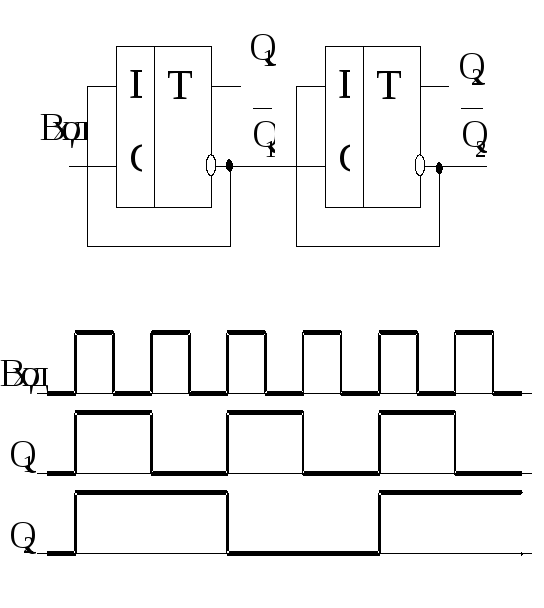

Описанные триггеры могут быть использованы в схемах счетных триггеров, имеющих один счетный вход С и пересчитывающих по модулю 2 счетные импульсы, поступающие на его вход.

Схемы счетных триггеров на основе D- и JK-триггеров представлены на рис. 8, диаграммы сигналов – на рис. 9.

На основе триггерных устройств строятся различные пересчетные и регистровые схемы.

Пересчетные схемы (счетчики) определяют сумму последовательного ряда импульсов (счетных импульсов) по модулю 2. Счетчики бывают суммирующие, вычитающие и реверсивные (которые могут как суммировать импульсы, так и вычитать).

Р и с. 7. Диаграммы сигналов JK-триггера

Р и с. 8. Схемы счетных триггеров

Р и с. 9. Диаграммы сигналов в схемах триггеров

Счетчики характеризуются коэффициентом пересчета К – максимальным числом сосчитанных импульсов. Коэффициент К зависит от числа разрядов счетчика (каждому разряду соответствует один триггер). Для n-разрядного счетчика максимальное значение К определяется соотношением Кmax=2n.

Схема асинхронного суммирующего четырехразрядного счетчика, выполненного на JK-триггерах, и диаграммы сигналов представлены на рис. 10. Легко убедиться, что в интервалах времени, следующих после входных импульсов 1, 2…, на выходах Q1…Q4 действует двоичный код, соответствующий числу поступивших импульсов.

Р и с. 10. Схема суммирующего счетчика на JKтриггерах

и диаграммы сигналов

Схема двухразрядного суммирующего счетчика, выполненного на D-триггерах, а также диаграммы сигналов представлены на рис. 11.

Схема двухразрядного вычитающего счетчика, выполненного на D-триггерах, и диаграммы сигналов представлены на рис. 12.

Р и с. 11. Схема суммирующего счетчика на D - триггерах и диаграммы сигналов

Двухразрядный счетчик имеет коэффициент пересчета 4, трехразрядный – 8, n-разрядный – 2n.

Часто требуются счетчики с произвольным коэффициентом пересчета, меньшим числа 2n. Для построения такого счетчика используют дополнительно межразрядные связи и вентильные схемы. В схемах JK-триггеров трехвходовые вентильные схемы встроены во входные цепи, такие триггеры имеют три входа J и три входа К.

Р и с. 12. Схема вычитающего счетчика на D триггерах и диаграммы сигналов

Некоторые схемы счетчиков (с коэффициентами пересчета К = 3, 5, 6) изображены на рис. 13.

Р и с. 13. Схемы счетчиков с разным значением К

Особое значение в цифровой схемотехнике имеют счетчики с коэффициентом пересчета, равным 10 (декадные счетчики). Одна из схем суммирующего декадного счетчика приведена на рис. 14. Работает она следующим образом. После поступления 9-го счетного импульса на выходах счетчика действует код 1001 (Q4=1,Q3=0,Q2=0,Q1=1), т.е. двоичный эквивалент цифры 9. При этом наJ,Kвходы схемыDD4 с выходаQ1поступает сигнал 1 (поэтому после поступления очередного 10-го импульса схемаDD4 инвертирует свое состояние, т.е. переходит в состояние 0); наJ,Kвходы схемыDD2 с выходаQ4поступает сигнал 0 (поэтому после поступления 10-го импульса схемаDD2 не меняет своего состояния 0). После поступления 10-го импульса схемаDD1 инвертирует свое состояние, т.е. переходит в состояние 0.

Р и с. 14. Схема суммирующего декадного счетчика

Следовательно, после поступления десятого импульса счетчик очищается (в него записывается код 0000).

Регистровые схемы (регистры) – схемы, предназначенные для записи и хранения цифровой информации, представленной двоичными кодами (словами). Регистры строятся на основе триггеров. Для записи каждого разряда кода используется один триггер. Регистры могут быть с последовательной и параллельной записями и со считыванием информации.

Регистры с параллельной записью информации представляют собой простой набор триггеров (рис. 15).

Перед записью кода, подаваемого на входы X1… XN, регистр очищают путем подачи на R входы триггеров сигнала низкого (нулевого) уровня. После этого по окончании очередного тактового импульса ТИ в регистр записывается код. Схема последовательного регистра имеет один вход, на который синхронно с тактовыми импульсами последовательно подается записываемый код (поразрядно, начиная с младшего разряда). Схема последовательного двухразрядного регистра, а также диаграммы сигналов представлены на рис. 16.