MPS_Metodichka

.pdf

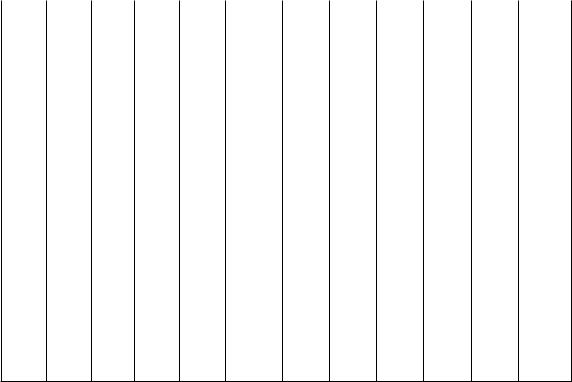

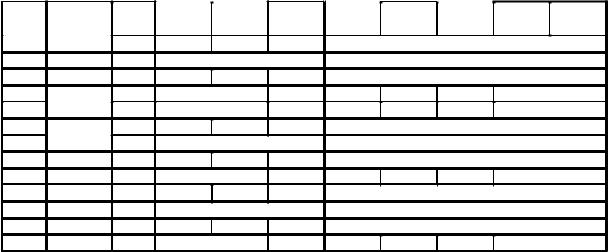

Таблица 2.12 Функции коммутаторов Ai, B, C, Ei, программируемых вентилей D и широко-ве- щательных линий F для одного (j-ого) ряда цифровых блоков в режиме FPGA

A0 A1 A2 A3 |

B |

C |

D |

E0 |

E1 |

E2 |

E3 |

F |

GIE[0] |

BCj |

BCj () |

C=A |

GOE[0] |

|

|

|

DBXj0 |

GIE[1] |

High |

SysClk*2 |

C=B |

|

GOE[1] |

|

|

DBXj1 |

GIE[2] |

Low |

VC1 |

C=-A |

|

|

GOE[2] |

|

DBXj2 |

GIE[3] |

CB0 |

VC2 |

C=-B |

|

|

|

GOE[3] |

DBXj3 |

GIE[4] |

CB1 |

VC3 |

C= |

GOE[4] |

|

|

|

None |

|

|

|

A&B |

|

|

|

|

|

GIE[5] |

CB2 |

CPU32 |

C=- |

|

GOE[5] |

|

|

BC(j-1) |

|

|

KHz |

(A&B) |

|

|

|

|

|

GIE[6] |

CB3 |

DBXj(i-1) |

C= |

|

|

GOE[6] |

|

BC(j+1) |

|

|

|

A&(-B) |

|

|

|

|

|

GIE[7] |

ROj[0] |

ROj[0] |

C= |

|

|

|

GOE[7] |

BC(j+2) |

|

|

|

(-A)&B |

|

|

|

|

|

GIO[0] |

ROj[1] |

ROj[1] |

C= |

GOO[0] |

|

|

|

|

|

|

|

AorB |

|

|

|

|

|

GIO[1] |

ROj[2] |

ROj[2] |

C= |

|

GOO[1] |

|

|

|

|

|

|

-(AorB) |

|

|

|

|

|

GIO[2] |

ROj[03 |

ROj[3] |

C= |

|

|

GOO[2] |

|

|

|

|

|

Aor(-B) |

|

|

|

|

|

GIO[3] |

RIj[0] |

RIj[0] |

C= |

|

|

|

GOO[3] |

|

|

|

|

(-A)orB |

|

|

|

|

|

GIO[4] |

RIj[1] |

RIj[1] |

C= |

GOO[4] |

|

|

|

|

|

|

|

AxorB |

|

|

|

|

|

GIO[5] |

RIj[2] |

RIj[2] |

C= |

|

GOO[5] |

|

|

|

|

|

|

-AxorB |

|

|

|

|

|

GIO[6] |

RIj[3] |

RIj[3] |

C=1 |

|

|

GOO[6] |

|

|

GIO[7] |

- |

Disable |

C=0 |

|

|

|

GOO[7] |

|

Примечания к таблице:

CBi - выход компаратора i-ой колонки аналоговых блоков; DBXj(i-1) - выход предыдущего цифрового блока текущего ряда;

BC(j-1),…, BC(j+2) - остальные широковещательные линии в массиве цифровых блоков.

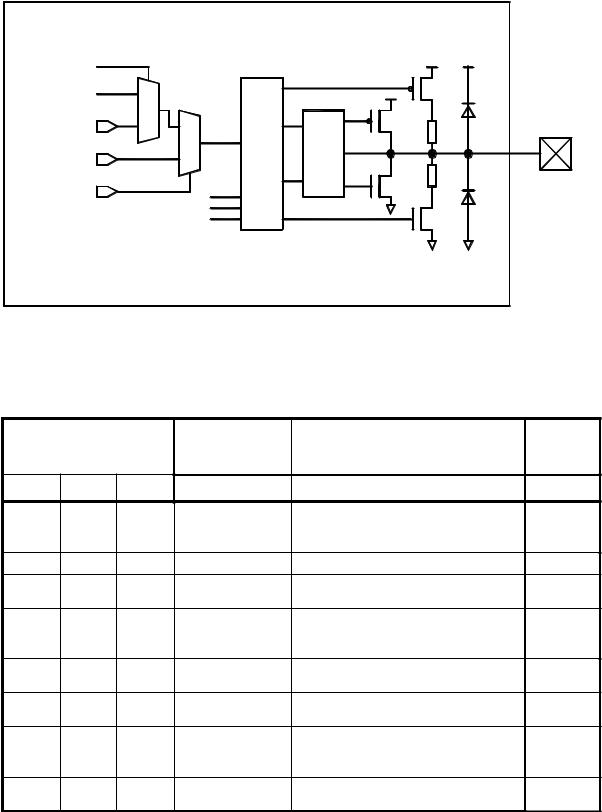

Входы-выходы портов, к которым могут подключаться линии GIE[x], GIO[x], GOE[x], GOO[x], обозначаются сокращенно как GPIO - входывыходы общего назначения. Конфигурация схемы подключения одного вывода (GPIO) порта изображена на рис.2.10. В таблице 2.13 приведены названия и характеристики режимов работы GPIO, устанавливаемые с помощью битов DM2-DM0, находящихся в трёх различных регистрах: PRTxDM2, PRTxDM1, PRTxDM0 соответственно. Чуть ниже таблицы приведены электрические схемы, иллюстрирующие соответствующие режимы работы GPIO.

Чтобы сконфигурировать GPIO на режим вывода с одной из линий системы глобальных межсоединений, необходимо установить в единицу соответствующий бит в подходящем регистре PRTxGS. При этом BYP устанавливается в 1, что отключает стандартный регистр порта PRTxDR от соответствующего вывода и подключает последний к нужной линии "глобальной шины вывода" (GlobalOutputBus), состоящей из GIE[x], GIO[x], GOE[x], GOO[x] и являющейся частью глобальной системы межсоединений (рис.2.4).

31

Выходной канал

BYP |

|

|

Запись PRTxDR |

2:1 |

|

Глобальная |

||

|

||

система вывода |

2:1 Äàí í û å |

|

Выход I2C |

|

|

Разрешающий |

|

|

вход I2C |

DM2 |

|

|

DM1 |

|

|

DM0 |

ЛОГИКА

|

|

Vpwr |

Vpwr |

|

|

Vpwr |

|

Управление |

|

5,6 K |

Вывод |

выхода |

|

||

|

|

||

типом |

|

PIN |

|

|

|

|

|

|

|

5,6 K |

|

Рис. 2.10. Схема управления режимом работы одного вывода порта.

Таблица 2.13

Режимы работы вывода порта и их схемы

|

Режимы |

|

Тип вывода |

Характеристика уровней |

Тип выво- |

|

|

|

|

|

|

выходного сигнала |

да по |

DM2 |

DM1 |

DM0 |

|

|

|

рис.2.10 |

|

|

|

|

|||

0 |

0 |

0 |

Резистивная на-Мощный высокий, последователь- |

0 |

||

|

|

|

грузка "вниз" |

но включенный резистор при низ- |

||

0 |

0 |

1 |

|

|

ком |

1 |

Мощный |

|

Мощные высокий и низкий |

||||

0 |

1 |

0 |

Высокий |

импе-Высокое входное сопротивление - |

2 |

|

0 |

1 |

1 |

данс |

|

для цифрового ввода |

|

Резистивная |

Последовательно включенный ре- |

3 |

||||

|

|

|

нагрузка |

|

зистор при высоком, мощный низ- |

|

1 |

0 |

0 |

"вверх" |

|

кий |

4 |

Источник |

высо-Медленный мощный высокий, от- |

|||||

1 |

0 |

1 |

кого |

|

ключенный низкий (большое R) |

5 |

Медленный |

Медленный мощный высокий, |

|||||

1 |

1 |

0 |

мощный выход |

медленный мощный низкий |

|

|

Высокий |

импе-Высокое входное сопротивление, |

6 |

||||

|

|

|

данс, аналого-цифровой ввод отключен (нулевая |

|||

1 |

1 |

1 |

вый ("Сброс") |

мощность) |

7 |

|

Источник низко-Медленный мощный низкий, от- |

||||||

|

|

|

го |

|

ключенный высокий (большое R) |

|

32

0. |

1. |

2. |

3. |

4. |

5. |

6. |

7. |

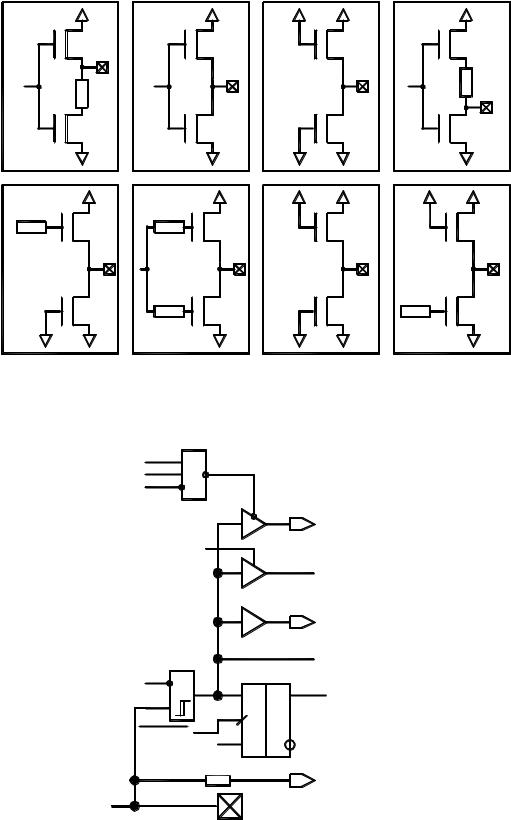

Рис. 2.11. Схемы выходных конфигураций для различных типов ввода-вывода

|

DM1BYP & |

|

Входной канал |

|

DM0 |

|

|

|

|

|

Глобальная |

|

|

|

система ввода |

Чтение PRTxDR |

|

Шина |

|

|

|

|

|

|

|

|

данных |

|

|

|

Вход I2C |

|

|

|

INBUF |

DM[2:0] = 110b |

& |

D T |

Фиксирование (при |

|

|||

|

|

прерывании) |

|

CELLRD |

C |

|

|

R |

|

||

|

RESET |

|

|

|

300 Ом |

|

Аналоговый |

|

|

|

|

К выходному |

ввод/вывод |

|

Pin |

||

каналу |

||

|

Рис. 2.12 Схема ввода информации через порт.

При сбросе PSoC все выводы GPIO автоматически подключаются к соответствующим выходам стандартных 8-разрядных регистров хранения портов PRTxDR (x - номер порта от 0 до 7), что даёт возможность исполь-

33

зовать их сразу после запуска в традиционном режиме - т.е. для хранения данных при выводе (по командам "MOV PRT[х], (источник байта)") или логических операций с чтением входов порта и записью в PRTxDR результата (типа "OR PRT[х], (источник кода)", "AND PRT[х], (источник кода)" и "XOR PRT[х], (источник кода)").

При вводе цифровой информации и вводе-выводе аналоговой для выводов порта используется схема рис.2.12.

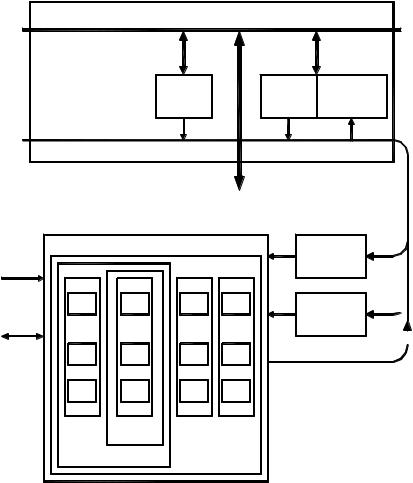

2.5 Аналоговая часть.

Структура аналоговой части PSoC для различных конфигураций приведена на рис.2.13.

Системная шина

ЯДРО PSoCтм |

Порт 0 Аналоговыедрайверы |

Порт 2 |

|

Массив аналоговых |

|

АНАЛОГОВАЯ |

||

|

блоков PSoC |

|

|

ПОДСИСТЕМА |

|

|

Кол-ка 0 |

Кол-ка 1 |

Кол-ка 2 Кол-ка 3 |

Аналоговый |

|

Цифровые |

|

|

|

|

опорный |

|

|

|

|

уровень |

|

часы от ядра |

СТ |

СТ |

СТ |

СТ |

Входной |

|

|||||

К цифровой |

|

|

|

|

аналоговый |

|

|

|

|

мультипл-р |

|

системе |

SC |

SC |

SC |

SC |

|

|

|

||||

|

SC |

SC |

SC |

SC |

|

1 колонка |

|

2 колонки |

4 колонки |

|

Глобальные аналоговые межсоединения

Глобальные аналоговые межсоединения

Рис. 2.13. Архитектура аналоговой части PSoC.

Каждая "аналоговая колонка" содержит один "непрерывный" конфигурируемый аналоговый блок (CT) и два конфигурируемых аналоговых блока на переключаемых конденсаторах (SC).

Аналоговая часть PSoC включает в себя выходные аналоговые усилители (аналоговые драйверы), входные аналоговые схемы и коммутаторы,

34

массив аналоговых конфигурируемых блоков (АКБ) и программируемую систему коммуникаций, обеспечивающих соединение различных устройств между собой.

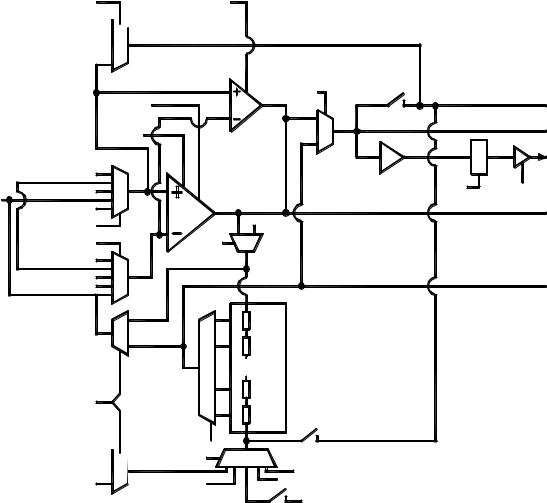

Основой "непрерывных" конфигурируемых аналоговых блоков (КАБов) служит схема, приведённая на рис.2.14. Схема построена на прецизионном малошумящем дифференциальном операционном усилителе A1. С помощью ряда аналоговых коммутаторов и набора прецизионных резисторов усилитель может включаться в различные конфигурации для получения необходимых коэффициентов усиления. Параллельно с усилителем включен микромощный компаратор А2, который может использоваться в так называемых "режимах сна с низким энергопотреблением" ("low power sleeping mode") для выполнения операций сравнения сигналов, когда основной усилитель (A1) выключен.

Управляющий |

LPCMPEN |

|

мультиплексор |

||

|

RefHi

RefLo

AGnd

|

|

|

|

Аналоговая |

|

|

|

|

|

шина |

|

|

|

CompCap |

|

Усиление |

ABUS |

|

PMuxOut |

|

|

||

|

|

PWR |

A2 |

триггер |

OUT |

|

|

|

|

CBUS |

|

|

|

|

|

|

|

Вход |

Входы блока |

|

|

|

|

|

|

|

|

|

|

порта |

ABUS |

|

|

Прозрачный, |

CBUS |

|

AGND |

A1 |

|

PHI1 или PHI2 |

Driver |

|

PMux |

Vdd |

|

GOUT |

|

FB |

|

|

|

|

|

NMux |

|

|

|

|

|

|

RTopMux |

|

|

|

|

|

Входы блока |

|

|

|

|

|

|

|

|

|

|

|

AGND |

|

|

|

LOUT |

|

RefHi, RefLo |

|

|

|

Усиление

EXGAIN

RTapMux

GIN

RBotMux

RBotMux

... |

... |

Резисторная матрица |

LIN |

AGND |

Vss SCBLK |

|

|

Соседний столбец |

||

|

|

|

|

|

|

INSAMP |

RBotMux |

Рис. 2.14. Схема "непрерывного" КАБ. Трапециями обозначены мультиплексоры

Управление конфигурациями "непрерывного" КАБ возможно как из левой части окна оболочки PSoC-Designer (с помощью таблицы установки параметров блоков), так и с помощью загрузки соответствующих кодов в регистры конфигурации "непрерывного" КАБ (табл.2.14).

35

Таблица 2.14

Регистры конфигурации "непрерывных" аналоговых блоков

Адрес |

Имя |

Число |

Бит 7 |

Бит 6 |

Бит 5 |

Бит 4 |

Бит 3 |

Бит 2 |

Бит 1 |

Бит 0 |

рег-ра регистра |

кол-к |

|

|

|

|

|

|

|

|

|

x,70h |

ACB00CR3 |

4,2 |

|

|

|

|

LPCMPEN |

CMOUT |

INSAMP |

EXGAIN |

x,71h |

ACB00CR0 |

4,2 |

|

RTapMux[3:0] |

|

Gain |

RTopMux |

RBotMux[1:0] |

||

x,72h |

ACB00CR1 |

4,2 |

AnalogBus |

CompBus |

|

NMux[2:0] |

|

|

PMux[2:0] |

|

x,73h |

ACB00CR2 |

4,2 |

CPhase |

CLatch |

CompCap |

TMUXEN |

TestMux[1:0] |

PWR[1:0] |

||

x,74h |

ACB01CR3 |

4,2,1 |

|

|

|

|

LPCMPEN |

CMOUT |

INSAMP |

EXGAIN |

x,75h |

ACB01CR0 |

4,2,1 |

|

RTapMux[3:0] |

|

Gain |

RTopMux |

RBotMux[1:0] |

||

x,76h |

ACB01CR1 |

4,2,1 |

AnalogBus |

CompBus |

|

NMux[2:0] |

|

|

PMux[2:0] |

|

x,77h |

ACB01CR2 |

4,2,1 |

CPhase |

CLatch |

CompCap |

TMUXEN |

TestMux[1:0] |

PWR[1:0] |

||

x,78h |

ACB02CR3 |

4 |

|

|

|

|

LPCMPEN |

CMOUT |

INSAMP |

EXGAIN |

x,79h |

ACB02CR0 |

4 |

|

RTapMux[3:0] |

|

Gain |

RTopMux |

RBotMux[1:0] |

||

x,7Ah |

ACB02CR1 |

4 |

AnalogBus |

CompBus |

|

NMux[2:0] |

|

|

PMux[2:0] |

|

x,7Bh |

ACB02CR2 |

4 |

CPhase |

CLatch |

CompCap |

TMUXEN |

TestMux[1:0] |

PWR[1:0] |

||

x,7Ch |

ACB03CR3 |

4 |

|

|

|

|

LPCMPEN |

CMOUT |

INSAMP |

EXGAIN |

x,7Dh |

ACB03CR0 |

4 |

|

RTapMux[3:0] |

|

Gain |

RTopMux |

RBotMux[1:0] |

||

x,7Eh |

ACB03CR1 |

4 |

AnalogBus |

CompBus |

|

NMux[2:0] |

|

|

PMux[2:0] |

|

x,7Fh |

ACB03CR2 |

4 |

CPhase |

CLatch |

CompCap |

TMUXEN |

TestMux[1:0] |

PWR[1:0] |

||

Особенностью схемы рис.2.14 является возможность получения на А1 |

||||||

положительных коэффициентов передач меньше единицы. |

||||||

Аналоговые конфигурируемые блоки на переключаемых конденсаторах |

||||||

реализованы в двух модификациях - тип С (рис.2.15) и тип D (рис.2.16). |

||||||

|

|

|

|

|

ф1 * AutoZero |

|

BQTAB |

|

|

CCap |

FCap |

|

|

|

|

|

(ф2 + !AutoZero) * |

|||

|

|

|

0,1,...,30,31 C |

16,32 C |

FSW1 |

|

C Inputs |

|

|

|

|

|

|

|

|

|

|

|

ф1 * FSW0 |

|

ACMux |

|

|

ACap |

ф2 + AutoZero |

|

|

A Inputs |

|

ф1 |

0,1,...,30,31 C |

|

|

|

|

|

|

|

|

|

|

RefHi |

|

|

|

ф1 * |

|

OUT |

|

|

|

|

|

||

RefLo |

|

ф2 |

|

!AutoZero |

|

|

AGnd |

|

|

|

|

|

AnalogBus * ф2В |

ARefMux |

|

|

|

Power |

|

ABUS |

ASign |

=1 |

|

|

|

||

|

|

|

|

|

||

Входы |

|

|

|

|

|

|

|

|

|

|

|

|

|

модуляции |

|

|

|

|

|

CBUS |

Mod Bit Control |

|

BCap |

(Компаратор) |

CBUS |

||

|

|

|

|

|

||

|

|

|

0,1,...,30,31 C |

|

|

|

|

|

ф2 |

|

ф2 |

ф1 Driver |

|

B Inputs |

|

|

|

|

|

|

|

|

|

ф1 |

|

|

|

BMuxSC

Рис. 2.15. КАБ на переключаемых конденсаторах (ПК) типа C. Блоки аналоговых мультиплексоров изображены в виде трапеций. Для обозначения логических операций использованы следующие символы: " " - логическое умножение; "+" - операция "ИЛИ", "!" - инверсия сигнала.

36

|

ф1 * AutoZero |

|

||

|

|

|

|

|

|

|

|

|

|

FCap |

(ф2 + !AutoZero) * CCap |

|||

16,32 C |

|

FSW1 |

0,1,...,30,31 C |

|

BQTAB

ф1 * FSW0

ф1 * FSW0

A Mux |

ACap |

ф2 + AutoZero |

|

|

|

ф1 0,1,...,30,31 C |

|

|

|

||

A Inputs |

|

|

|

||

|

|

|

|

|

|

RefHi |

|

ф1 * |

|

|

OUT |

|

|

|

|

||

RefLo |

ф2 |

!AutoZero |

|

|

|

AGnd |

|

|

|

AnalogBus * ф2В |

|

ARefMux |

|

|

|

|

|

ASign |

BCap |

Power |

|

ABUS |

|

|

ф2 + !BSW + |

|

|

|

|

|

ф2 + !BSW 0,1,...,30,31 C |

AutoZero |

|

|

|

B Inputs |

|

|

|

|

CBUS |

|

ф1 * |

ф1 * BSW * |

(Компаратор) |

|

|

|

BSW |

!AutoZero |

ф2 |

ф1 |

CBUS |

|

|

|

Driver |

||

BMuxSCD

Рис. 2.16. КАБ на ПК типа D. Аналоговые мультиплексоры изображены в виде трапеций, а логические операции кодируются следующими символами: " " - логическое умножение; "+" - операция "ИЛИ", "!" - инверсия сигнала.

Отличия в блоках типа C и D связаны с возможностью их конфигурирования в схемы фильтров на переключаемых конденсаторах, в которых требуется ёмкостная обратная связь между КАБами. Эта связь формируется на основе переключаемых конденсаторов CCap, входящих в КАБ типа C.

В табл.2.15 приведена структура регистров конфигурации для КАБов типа С.

|

|

|

|

|

|

|

|

Таблица 2.15 |

|

|

Структура регистров конфигурации для SC-блоков типа C |

||||||||

Адрес |

Имя |

Число |

Бит 7 |

Бит 6 |

Бит 5 |

Бит 4 |

Бит 3 Бит 2 |

Бит 1 |

Бит 0 |

рег-ра регистра кол-к |

|

|

|

|

|

|

|

||

x,80h |

ASC10CR0 |

4,2 |

FCap |

ClocPhase |

ASign |

|

ACap[4:0] |

|

|

x,81h |

ASC10CR1 |

4,2 |

|

ACMux[2:0] |

|

|

BCap[4:0] |

|

|

x,82h |

ASC10CR2 |

4,2 |

AnalogBus |

CompBus |

AutoZero |

|

CCap[4:0] |

|

|

x,83h |

ASC10CR3 |

4,2 |

ARefMux[1:0] |

FSW1 |

FSW0 |

BMuxSC[1:0] |

PWR[1:0] |

||

x,88h |

ASC12CR0 |

4 |

FCap |

ClocPhase |

ASign |

|

ACap[4:0] |

|

|

x,89h |

ASC12CR1 |

4 |

|

ACMux[2:0] |

|

|

BCap[4:0] |

|

|

x,8Ah |

ASC12CR2 |

4 |

AnalogBus |

CompBus |

AutoZero |

|

CCap[4:0] |

|

|

x,8Bh |

ASC12CR3 |

4 |

ARefMux[1:0] |

FSW1 |

FSW0 |

BMuxSC[1:0] |

PWR[1:0] |

||

x,94h |

ASC21CR0 |

4,2,1 |

FCap |

ClocPhase |

ASign |

|

ACap[4:0] |

|

|

x,95h |

ASC21CR1 |

4,2,1 |

|

ACMux[2:0] |

|

|

BCap[4:0] |

|

|

x,96h |

ASC21CR2 |

4,2,1 |

AnalogBus |

CompBus |

AutoZero |

|

CCap[4:0] |

|

|

x,97h |

ASC21CR3 |

4,2,1 |

ARefMux[1:0] |

FSW1 |

FSW0 |

BMuxSC[1:0] |

PWR[1:0] |

||

x,9Ch |

ASC23CR0 |

4 |

FCap |

ClocPhase |

ASign |

|

ACap[4:0] |

|

|

x,9Dh |

ASC23CR1 |

4 |

|

ACMux[2:0] |

|

|

BCap[4:0] |

|

|

x,9Eh |

ASC23CR2 |

4 |

AnalogBus |

CompBus |

AutoZero |

|

CCap[4:0] |

|

|

x,9Fh |

ASC23CR3 |

4 |

ARefMux[1:0] |

FSW1 |

FSW0 |

BMuxSC[1:0] |

PWR[1:0] |

||

|

|

|

|

|

|

|

|

37 |

|

Структура конфигурационных регистров для блоков на переключаемых

конденсаторах типа D приведена в табл.2.16.

Структура регистров конфигурации для SC-блоков типа DТаблица 2.16

Адрес |

Имя |

Число |

Бит 7 |

Бит 6 |

Бит 5 |

Бит 4 |

Бит 3 |

Бит 2 |

Бит 1 |

Бит 0 |

|

рег-ра регистра кол-к |

|

|

|

|

|

|

|

|

|

||

x,84h |

ASD11CR0 |

4,2,1 |

FCap |

ClocPhase |

ASign |

|

|

ACap[4:0] |

|

|

|

x,85h |

ASD11CR1 |

4,2,1 |

|

AMux[2:0] |

|

|

|

BCap[4:0] |

|

|

|

x,86h |

ASD11CR2 |

4,2,1 |

AnalogBus |

CompBus |

AutoZero |

|

|

CCap[4:0] |

|

|

|

x,87h |

ASD11CR3 |

4,2,1 |

ARefMux[1:0] |

FSW1 |

FSW0 |

BSW |

BMuxSD |

PWR[1:0] |

|

||

x,8Fh |

ASD13CR3 |

4 |

ARefMux[1:0] |

FSW1 |

FSW0 |

BSW |

BMuxSD |

PWR[1:0] |

|

||

x,90h |

ASD20CR0 |

4,2 |

FCap |

ClocPhase |

ASign |

|

|

ACap[4:0] |

|

|

|

x,91h |

ASD20CR1 |

4,2 |

|

AMux[2:0] |

|

|

|

BCap[4:0] |

|

|

|

x,92h |

ASD20CR2 |

4,2 |

AnalogBus |

CompBus |

AutoZero |

|

|

CCap[4:0] |

|

|

|

x,93h |

ASD20CR3 |

4,2 |

ARefMux[1:0] |

FSW1 |

FSW0 |

BSW |

BMuxSD |

PWR[1:0] |

|

||

x,98h |

ASD22CR0 |

4 |

FCap |

ClocPhase |

ASign |

|

|

ACap[4:0] |

|

|

|

x,99h |

ASD22CR1 |

4 |

|

AMux[2:0] |

|

|

|

BCap[4:0] |

|

|

|

x,9Ah |

ASD22CR2 |

4 |

AnalogBus |

CompBus |

AutoZero |

|

|

CCap[4:0] |

|

|

|

x,9Bh |

ASD22CR3 |

4 |

ARefMux[1:0] |

FSW1 |

FSW0 |

BSW |

BMuxSD |

PWR[1:0] |

|

||

Необходимо подчеркнуть, что знание структуры регистров конфигурации "непрерывных" блоков и блоков на переключаемых конденсаторах полезно лишь в тех случаях, когда разработчик, хорошо понимая принципы их функционирования, хочет создать собственные оригинальные конфигурации включения таких блоков, не входящие в библиотеку стандартных (библиотечных) модулей оболочки PSoC Designer. Во всех остальных случаях лучше использовать готовые модули из указанной библиотеки.

На начало 2006 года фирма-изготовитель PSoC анонсировала следующие типы аналоговых и аналого-цифровых модулей, доступных разработчикам, с обещанием в дальнейшем увеличить их перечень:

1). Дельта-сигма АЦП.

2). АЦП последовательного приближения.

3). Инкрементирующий АЦП.

4). ЦАП.

5). Программируемые усилители (с коэффициентами усиления как больше, так и меньше единицы).

6). Аналоговые компараторы.

7). Детекторы пересечения нуля.

8). Устройства выборки и хранения*.

9). Фильтры низкой частоты.

10). Полосовые фильтры.

11). Заграждающие полосовые фильтры (т.е. подавляющие сигналы в заданной полосе частот).

12). Амплитудные модуляторы.

13). Амплитудные демодуляторы.

14). Генераторы синусоидальных сигналов.

15). Выпрямители синусоидальных сигналов.

16). Детектирование превышения порога.

38

17). Ограничение по порогу.

18). Датчик температуры.

19). Выходной аудио-усилитель.

20). Двухтональный генератор для тонального вызова (набора) номера телефона.

21). ЧМ-модулятор (устройство для частотной модуляции). 22). Встроенный модем.

Следует отметить, что на самом деле п.8 (отмеченный звёздочкой) не реализован в библиотеке стандартных элементов оболочки PSoC Designer версии 4.2, хотя в процессе работы SC-блоков действительно имеют место фазы запоминания и хранения уровней сигналов. Благодаря этому реализация режима выборки и хранения становится в действительности возможной, но требует специального режима управления фазами работы SC-бло- ка. Подобного рода полезные конфигурации, повышающие функциональные возможности PSoC, будут рассмотрены отдельно.

Рабочий диапазон аналоговых сигналов PSoC – примерно от 0 до +Епит.. Возможна установка уровня «аналоговой земли», равной Епит./2.

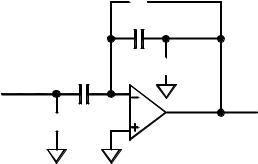

Для понимания основ работы SC-блоков рассмотрим схему рис.2.17.

Ф2 |

CA |

Uвх. |

|

|

Ф1 |

Ф1

CF Ф2

Ф1 |

U вых.

Рис. 2.17. Базовая схема операционного усилителя (ОУ) на переключаемых конденсаторах (ПК).

Вначале на схему поступает сигнал управления Ф1 ("фаза 1", в англоязычной версии часто обозначается как "PHI 1" - см., например, рис.2.14). Этот сигнал замыкает те ключи, рядом с которыми он записан. Получается следующая схема (рис.2.18):

|

|

CF |

Uвх. |

CA |

|

a |

U вых. |

|

|

|

Рис. 2.18. Конфигурация включения ОУ на ПК в фазе Ф1.

39

Нетрудно показать, что после окончания переходных процессов напряжение на выходе Uвых. схемы рис.2.18 будет равно:

Uвых. = Eсм.0,

где Eсм.0 - смещение нуля дифференциального операционного усилителя (ДОУ). Действительно, из основной формулы (2.1) работы ДОУ:

U |

вых. |

= K |

U |

(U + |

− U − |

+ E |

см.0 |

) |

, |

(2.1) |

|

|

вх |

вх |

|

|

где KU - коэффициент усиления ДОУ по напряжению, Uвх+ = 0 - напряже-

ние на неинвертирующем (заземлённом) входе усилителя, U вх− - напряжение на инвертирующем входе усилителя (т.е. фактически в точке a), следует, что:

|

|

Uвх+ − U вх− + Eсм.0 = |

Uвых |

|

|

|

|

|||

|

|

|

|

|

KU . |

|

|

|

|

|

С учётом того, что Uвх+ = 0 , и для идеального усилителя KU=∞, а напря- |

||||||||||

жение U |

вых. |

- величина ограниченная: |

U |

вых. |

[− E |

пит. |

;+ E |

пит. |

] , где Eпит - |

|

|

|

|

|

|

|

|||||

напряжение питания ДОУ, Uвх+ = 0 и Uвх− |

= Uвых. , получаем: |

|

|

|||||||

0 − U вых. + Eсм.0 ≈ 0 ,

то есть действительно: Uвых. ≈ Eсм0.

Напряжение Eсм.0 заряжает параллельно включенные между точкой a и землёй конденсаторы CA и CF, а также паразитную ёмкость входа самого ДОУ (для простоты на рис.2.18 не показанную). Фактически это приводит к запоминанию погрешности Eсм.0 на инвертирующем входе ДОУ, то есть в формуле (2.1) последовательно с внутренним источником погрешности +Eсм.0 как бы включается корректирующий источник -Eсм.0, (запомненное значение подаётся на инвертирующий вход ДОУ, т.е. со знаком "минус") вследствие чего суммарная погрешность из-за смещения нуля усилителя аннулируется. Эта процедура в ДОУ на ПК получила название "автонуление" ("autozeroing").

После окончания импульса Ф1 с небольшой задержкой начинается импульс (фаза) Ф2. При этом получается схема, приведённая на рис.2.19.

|

|

CF |

Uвх. |

CA |

|

a |

U вых. |

|

|

|

Рис. 2.19. Базовая схема на ПК в фазе Ф2.

40