KonspektOKPMRES

.pdf

|

L1 |

|

|

|

V1 |

10mH |

|

|

|

|

|

|

|

|

-1/1V |

|

|

V1 |

X1 |

|

|

|

||

|

C1 |

|

-1/1V |

|

|

10nF |

|

|

|

500 Hz |

R1 |

R2 |

|

X2 |

|

50 |

20k |

500 Hz |

|

|

|

|

|

|

|

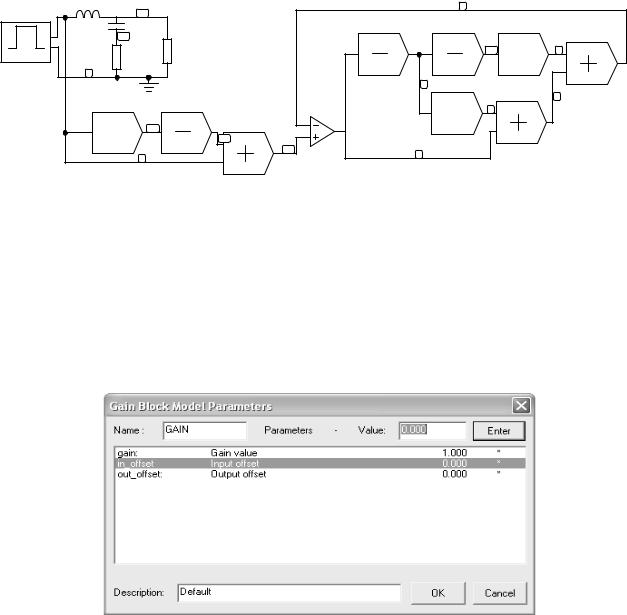

Рис. 13.5. |

|

Рис. 13.6. |

|

Вначале найдем передаточную функцию фильтра K(p). В общем случае, если звено представляется в виде схемы на рис. 13.6, то передаточная функция определится как K(p)=X2/(X1+X2).

В нашем случае X1=pL, а X2=X3*R2/(X3+R2), где X3=R1+1/(pC).

Поэтому

X2=(R2+pCR1R2)/[1+pC(R1+R2)]

и передаточная функция составит

X2 |

(R2+pCR1R2)/[1+pC(R1+R2)] |

|

|

|

|||

K(p)= |

= |

|

|

|

= |

|

|

|

|

|

|

||||

X1+X2 |

pL+(R2+pCR1R2)/[1+pC(R1+R2)] |

|

|

|

|||

R2+p(CR1R2) |

|

1+p*τ1 |

|

|

(13.3) |

||

= |

|

|

= |

|

|

, |

|

|

|

|

|

||||

R2+p(CR1R2+L)+p2LC(R1+R2) |

|

1+p*τ2+ p2 *τ32 |

|

|

|

||

где τ1=CR1=5*10-7=0.5u, τ2=CR1+L/R2=10-6=1u, τ32=LC(1+R1/R2)=1.002*10-10=100.2p.

Для контроля правильности преобразований следует обращать внимание на единицы измерения: слагаемые числителя и знаменателя – безразмерны.

Выполняя далее обратное преобразование Лапласа, получаем дифференциальное уравнение RLC-фильтра

τ32d2y(t)/dt2 + τ2dy(t)/dt + y(t) = τ1dx(t)/dt + x(t) |

(13.4) |

Исходя из свойств (13.2), можно убедиться, что ДУ (13.4) описывает ФНЧ (a3 = 0 и b3 ≠ 0) второго порядка.

71

В случае, когда в K(p) степень числителя равна степени знаменателя (РФ, ФВЧ) для улучшения сходимости выражение (13.4) необходимо представить как функцию разности z(t)=x(t)-y[x(t)]:

τ32d2(x-y)/dt2+τ2d(x-y)/dt2+ax-by=0 (13.3)

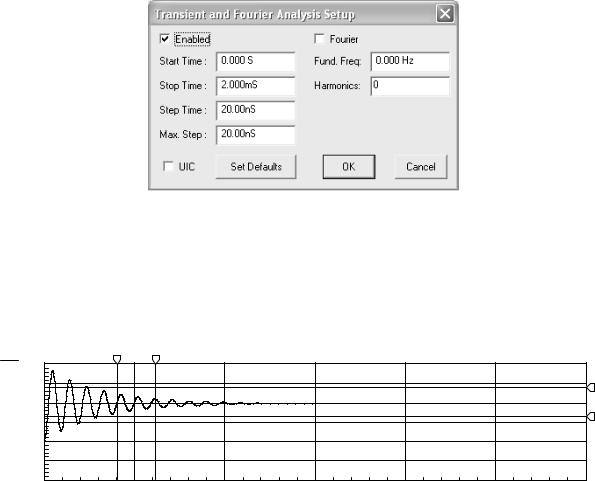

Для решения уравнения (13.4) в пакете Circuit Maker вводим следующую схему.

|

10m |

|

|

|

|

6 |

|

|

|

-1/1V |

14 |

|

|

|

|

|

|

|

|

10n |

|

|

|

|

|

|

|

|

|

|

|

|

DDT |

|

DDT |

|

TAU32 |

SUM |

|

|

15 |

|

|

d |

|

d |

|

|

|

500 Hz |

50 |

|

20k |

|

10 |

gain |

8 |

||

|

dt |

|

dt |

||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

TAU2 |

|

|

|

|

|

|

|

|

|

|

SUM |

|

|

|

TAU1 |

|

DDT |

|

|

|

|

7 |

|

|

|

IDEAL |

|

gain |

9 |

|

|

||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||

|

gain |

13 |

d |

SUM |

|

|

|

|

|

|

|

dt |

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

11 |

|

|

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 13.7. |

|

|

|

|

|

Вначале из базы данных по пути Function Block -> Misc. -> Gain устанавливаем блок по умолчанию. Затем последовательно каждый блок редактируем: двойное нажатие и в окне Edit/Select Model нажимаем кнопку Edit. Открывается новое окно (рис. 13.8), в котором указывается имя нового блока и величина усиления путем нажатия кнопки Enter.

Рис. 13.8.

Значение усиления нужно вводить как можно точнее. После редактирования нужно назначить необходимый блок GAIN в схеме.

72

Далее устанавливаем тип моделирования. В данном случае – временную характеристику.

Запускаем моделирование. Если появляется сообщение “Step too small”, то в установках Simulation -> Analyses Setup -> Analog Options задаем большее число шагов поиска решения: ITL4 - max, transient analyses time point iterations - вместо 40 ставим 100…500.

Если моделирование прошло успешно, то сравниваем результаты прямого расчета переходной характеристики фильтра с решением дифференциального уравнения (клавиша Shift для одновременного вывода нескольких графиков).

Далее повышаем точность вычисления путем уменьшения шага интегрирования:

Рис. 13.9.

При этом время счета существенно увеличивается. В результате можно добиться практически полного совпадения переходных характеристик

Xa: |

411.1u |

Xb: |

268.9u |

a-b: |

142.2u freq: 7.031k |

Yc: |

1.800 |

Yd: |

300.0m |

c-d: |

1.500 |

ba

A3

B

2

c

1

d

0

-1

-2

-3

0 |

333u |

667u |

1m |

1.33m |

1.67m |

2m |

|

|

Ref=Ground |

X=333u/Div Y=voltage |

|

|

|

Рис. 13.10.

Для некоторых схем в лабораторной работе №5 совпадение наступает со второго полупериода, что связано с выбором начальных условий в CM. Вместе с файлом *.ckt моделирования функцио-

73

нальной схемы нужно предоставить файл GAIN.MOD, который расположен в папке Models.

Контрольные вопросы

1.Дайте определение функциональной схемы.

2.Что такое дифференциальное уравнение и какое решение оно дает?

3.Получите дифференциальное уравнение для интегрирующего звена.

4.Опишите методику решения дифуравнения с помощью ОУ.

5.Нарисуйте функциональную схему определения переходной характеристики RC-звена на основе решения дифуравнения.

74

14. Моделирование цифровых схем. Часть 1

Перед тем, как процессор сгорит, в его памяти проносятся все операции, которые он совершал в своей жизни

14.1. Преимущества и недостатки цифровых схем по сравнению с аналоговыми

Для аналогового сигнала характерна непрерывность, соответствие некоторой физической величине. Здесь схема моделируется так, как если бы это был реальный макет.

|

|

|

Усил. |

|

|

|

|

|

|

МКФ |

|

|

|

Фильтр |

|

|

|

|

|

|

|

|

|

|

(Анал. |

|

|

|

|

|

|

|

|

|

|

Усил. |

|

Гр. |

|

|

|

|

|

|

обраб.) |

|

|

||

|

|

|

Магни- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

тофон |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 14.1.

Достоинства аналоговых схем:

•Простота – мало элементов, невысокая стоимость

•Высокое быстродействие – все элементы работают одновременно Недостатки аналоговых схем

•Низкая помехозащищенность: наводки и тепловые шумы

•Низкая точность и стабильность выполнения операций

•Низкая надежность хранения информации

Для цифрового сигнала характерны дискретность по времени и уровню, а также определенный способ организации (кодирования) данных. Моделирование осуществляется на уровне логики с задержками отсчетов.

МКФ |

|

Усил |

|

АЦП |

|

Цифр. |

|

ЦАП |

|

Усил |

|

Гр. |

|

|

|

|

|

|

Функ. |

|

|

|

|

|

|

|

|

|

|

HD,CD |

|

|

|

|

|

|

|

|

|

|

|

|

|

преобр |

|

|

|

|

|

|

|

|

|

|

|

Flash |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 14.2.

Достоинства цифровой обработки:

•Высокая помехозащищенность

•Высокая точность преобразования

75

•Эффективность хранения данных

•Программируемость

•Предсказуемость и технологичность Недостатки цифровых методов:

•Низкое быстродействие

•Сложность

•Высокая стоимость

14.2.Системные параметры цифровых схем

1.Метод представления данных. Цифровые данные могут представляться в параллельном или последовательном коде. Парал-

лельный код передается по n линиям (разрядам). Общее количество состояний равно 2n. Последовательный код передается по одной линии, но с тактовой частотой в 2n раз больше. Данные могут быть представлены как с фиксированной, так и с плавающей точкой.

2.Выбор разрядности. Определяется как большее из двух значений по таким параметрам:

•динамический диапазон – отношение максимального уровня к минимальному уровню передаваемых сигналов. Представляется обычно в децибелах. Здесь разрядность вычисляется по правилу 6 дБ динамического диапазона на один разряд.

•допустимая ошибка вычислений, которая составляет 1/2n.

3.Выбор тактовой частоты или частоты дискретизации. Определяется для параллельного кода теоремой Котельникова, согласно которой информация о передаваемом аналоговом сигнале не будет потеряна, если частота дискретизации fд при переходе к дискретному сигналу превышает удвоенную верхнюю частоту 2Fв передаваемого сигнала. Это объясняется тем, что при дискретизации спектр сигнала становится периодическим и если fд<2Fв, то границы спектров будут суммироваться и разделить их при переходе к аналоговому сигналу будет невозможно, т.е. неизбежно возникнут ошибки. На практике обычно частоту дискретизации берут как fд=3…5Fв для снижения требований к ФНЧ на выходе цифроаналогового преобразователя.

76

14.3.Особенности моделирования цифровых схем

вCircuit Maker

Моделирование цифровых схем в CM производится по тактам в виде логических операций и задержек сигналов, кратных числу тактов.

Установка режима цифрового моделирования производится нажатием 12-й кнопки слева из панели инструментов: изображение транзистора на кнопке переключается в изображение логического элемента И.

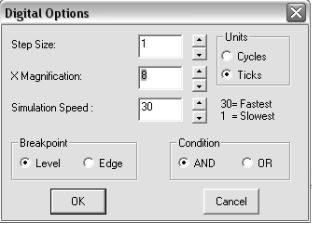

Моделирование возможно в автоматическом режиме и по шагам. Параметры режима цифрового моделирования задаются в опции Simulation (√ Digital Mode – снять флажок Analog) -> Digital Options. Открывается окно установок (рис. 14.3).

Рис.14.3. Окно Digital Options

Здесь задается размер шага Step Size, который определяет цифровую задержку. Units – единицы шага моделирования: либо по тактам Ticks (подробно, но долго), либо по циклам Cycles=10*Ticks (грубо, но быстро). X Magnification – масштаб цифрового осциллографа (по умолчанию 8 тиков). Скорость моделирования – Simulation Speed. Условие прерывания моделирования: AND – все логические действия схемы должны выполниться прежде, чем моделирование прекратится, OR – моделирование прекращается по первому требованию.

Чтобы активизировать цифровой осциллограф, необходимо нажать кнопку с осциллограммами на панели инструментов. Если нажать также кнопку с инвертором на панели инструментов, то линии

77

с высоким и низким уровнем будут отображаться, соответственно, красным и синим цветом.

14.4. Цифровая базовая логика NOT, AND, OR, XOR и

D-триггер

1) Инвертор – схема НЕ (NOT).

Формирует на выходе логическое значение, противоположное входному сигналу. Электрическая схема и таблица истинности представлены на рис. 14.4.

|

|

|

|

|

X |

Y |

x |

|

|

|

y |

1 |

0 |

|

|

|||||

|

|

|

|

|

0 |

1 |

Рис. 14.4. Схема НЕ

2) Логическое умножение – схема И (AND)

Выходной сигнал y=x1*x2 равен единице, только когда оба входных сигнала равны единице.

|

|

|

|

|

|

X1 |

X2 |

Y |

|

x1 |

|

|

|

|

|

0 |

0 |

0 |

|

|

|

|

|

|

|||||

|

|

|

y |

0 |

1 |

0 |

|||

x2 |

|

|

|

|

|||||

|

|

|

|

||||||

|

|

|

|

|

|

|

|||

1 |

0 |

0 |

|||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

1 |

1 |

1 |

|

Рис. 14.5. Схема И

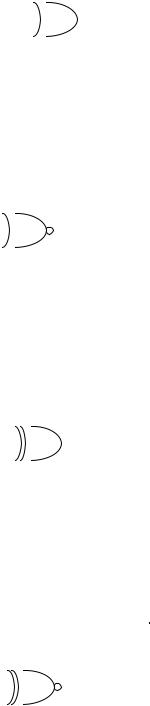

3) Логическое умножение с отрицанием – схема И-НЕ (NAND) Отличается от схемы И дополнительным инвертированием выходного сигнала. Инвертирование обозначается кружком на выходе

схемы.

|

|

|

|

|

|

X1 |

X2 |

Y |

|

x1 |

|

|

|

|

|

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

||

y |

0 |

1 |

1 |

||||||

|

|

|

|

||||||

x2 |

|

|

|

|

|||||

|

|

|

|

||||||

|

|

|

|

|

1 |

0 |

1 |

||

|

|

|

|

|

|

||||

|

|

|

|

|

|

1 |

1 |

0 |

Рис. 14.6. Схема И-НЕ

78

4) Логическое сложение – схема ИЛИ (OR)

Выходной сигнал y=x1+x2 равен единице, если хотя бы один из входных сигналов равен единице. Является схемой И для нулевых уровней входных сигналов.

|

|

|

|

|

|

|

X1 |

X2 |

Y |

x1 |

|

|

|

|

|

|

0 |

0 |

0 |

|

|

|

|

|

|

||||

|

|

|

y |

0 |

1 |

1 |

|||

|

|||||||||

x2 |

|

|

|

|

|

||||

|

|

|

|

|

|||||

|

|

|

|

1 |

0 |

1 |

|||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

1 |

1 |

1 |

Рис. 14.7. Схема ИЛИ |

|

|

|||||||

5) Логическое умножение с отрицанием – схема ИЛИ-НЕ (NOR) Добавлено инвертирование к схеме ИЛИ.

x1 |

|

|

|

|

|

|

X1 |

X2 |

Y |

|

|

|

|

|

|

|

|

|

|

||

y |

0 |

0 |

1 |

|||||||

|

|

|

|

|

||||||

x2 |

|

|

|

|

|

|||||

|

|

|

|

|

||||||

|

|

|

|

0 |

1 |

0 |

||||

|

||||||||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

1 |

0 |

0 |

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

Рис. 14.8. Схема ИЛИ-НЕ

6)Суммирование по модулю 2 – схема исключающее ИЛИ (XOR)

x1 |

|

|

|

|

|

X1 |

X2 |

Y |

|

|

|

|

|

|

|||||

|

|

|

y |

0 |

0 |

0 |

|||

x2 |

|

|

|

|

|||||

|

|

|

|

||||||

|

|

|

|

|

|

|

|||

0 |

1 |

1 |

|||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

1 |

0 |

1 |

|

|

|

|

|

|

|

1 |

1 |

0 |

|

Рис. 14.9. Схема исключающее ИЛИ

7) Исключающее ИЛИ с отрицанием (XNOR)

|

|

|

|

|

|

|

X1 |

X2 |

Y |

|

|

|

|

|

|

|

0 |

0 |

1 |

x1 |

|

|

|

|

|

y |

0 |

1 |

0 |

|

|

|

|||||||

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

x2 |

|

|

1 |

0 |

0 |

||||

|

|

|

|

|

|

||||

|

|

|

|

|

|||||

|

|

|

|

||||||

|

|

|

|

|

|

|

1 |

1 |

1 |

Рис. 14.10. Схема исключающее ИЛИ-НЕ

79

8) D-триггер – элемент с двумя устойчивыми состояниями, т.е. ячейка памяти в 1 бит.

S

DQ

_

CP Q

R

Рис. 4.11. D-триггер

Кроме выводов питания микросхема содержит также информационный вход D (Data), счетный вход CP, входы установки в единицу S (Set) и в ноль R (Reset) на выходе Q. Выход Q всегда противоположен по значению Q. Запись данных в триггер со входа D производится в момент положительного фронта тактового импульса на выводе CP. Если выход Q соединить с D, то получим делитель частоты на 2 на выходе Q по отношению ко входу CP.

Контрольные вопросы

1.Раскройте преимущества и недостатки цифровых систем.

2.Как определить разрядность и тактовую частоту цифровых схем?

3.Каковы особенности моделирования цифровых устройств с CM?

4.Как задать цифровой режим работы?

5.Опишите действия цифровой логики NOT, OR, AND.

6.Что такое D-триггер и как он функционирует?

80