- •5 Логические (цифровые) устройства 106

- •5.1 Комбинационные логические элементы 106

- •5.2 Последовательностные устройства 130

- •5 Логические (цифровые) устройства

- •5.1 Комбинационные логические элементы

- •5.1.1 Основные определения алгебры логики

- •5.1.2 Представление логических функций

- •5.1.3 Законы (правила преобразования) алгебры логики

- •5.1.4 Способы минимизации логических функций

- •5.1.5 Основные параметры и характеристики цис

- •5.1.6 Основные серии цифровых интегральных схем

- •5.1.7 Схемотехника логических элементов на диодах

- •5.1.8 Схемотехника ттл логики

- •5.10 Ттл логический элемент или-не

- •5.1.9 Схемотехника кмоп логических элементов

- •5.1.10 Сумматоры

- •5.1.11 Дешифраторы

- •5.1.12 Мультиплексоры

- •5.2 Последовательностные устройства

- •5.2.1 Rs-триггер

- •Синтез rs-триггера на элементах или-не

- •5.2.2 Счетный т-триггер

- •5.2.4 Универсальный jk-триггер

- •5.2.5 Счетчики сигналов

- •5.2.6 Регистры

Синтез rs-триггера на элементах или-не

RS–триггер имеет два управляющих входа S (set) и R (reset), с помощью которых выполняются установки триггера в то или иное состояние.

Синтезируем триггер с двумя установочными входами: R – вход установке на выходе Q нулевого состояния; S – вход установки на выходе Q единичного состояния. Пусть установка осуществляется единичными уровнями входов, то есть входы прямые. Построим граф переходов.

Рис. 5.19 Граф переходов для RS-триггера

В графе переходов не включена входная комбинация 11, которая считается запрещенной. По графу переходов можно составить таблицу переходов (функционирования).

|

n |

n+1 | ||

|

Qn |

R |

S |

Qn+1 |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

~ |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

~ |

Рис. 5.20 Таблица переходов RS-триггера

В таблице переходов запрещенной комбинации входов поставлено неопределенное состояние триггера, которое потом уточним из условия простоты реализации схемы триггера.

По таблице функционирования составим карту Карно, минимизируем ее и построим логическую схему триггера. Минимизацию карты Карно будем вести по нулевым контурам, для получения формулы в виде КНФ, которая легче преобразуется к виду, удобному реализацией элементами ИЛИ-НЕ. Для увеличения размера нулевого контура включим в него клетки с неопределенным состоянием триггера.

Рис. 5.21 Карта Карно для получения КНФ

Получим уравнение в виде КНФ и преобразуем его

![]() .

(5.12)

.

(5.12)

По уравнению составим схемы в элементном базисе ИЛИ-НЕ

Рис. 5.22 Схемная реализация RS-триггера

С учетом конкретной реализации можно составить упрощенную таблицу переходов

|

n |

n+1 | ||

|

Qn |

R |

S |

Qn+1 |

|

Х |

1 |

Х |

0 |

|

Х |

0 |

1 |

1 |

|

Х |

0 |

0 |

Qn |

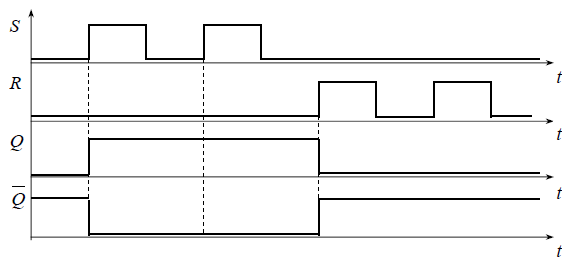

Рис. 5.23 Временные диаграммы работы RS-триггера

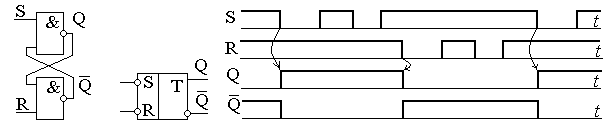

Схемотехнически RS-триггер может быть реализован на элементах 2И-НЕ (рис. 5.24,а) с использованием перекрестных положительных обратных связей. В триггере на элементах 2И-НЕ изменение состояния происходит при низких уровнях сигналов S и R .

Рис. 5.24 RS-триггер на элементах И-НЕ: а) – принципиальная схема;

б) – условное обозначение; в) – временная диаграмма.

В синхронных RS-триггерах могут быть использованы различные способы синхронизации. На рис. 5.25, а и б показана схемотехническая реализация и условное обозначение RS-триггера с синхронизацией по высокому уровню. На рис. 5.25, в приведены диаграммы работы такого триггера. Изменение состояний происходит только при высоких уровнях сигнала синхронизации С.

а) б) в)

Рис. 5.25 Синхронизируемый RS-триггер

5.2.2 Счетный т-триггер

Т-триггер иначе называют счетным и применяются для построения счетчиков и делителей частоты. Такой триггер имеет один тактовый вход и его выходное состояние меняется каждый раз по заднему фронту (перепад «1»-«0») счетного импульса Т. На рис. 5.26,а приведена двухтактная схема счетного триггера, которая часто применяется в интегральной схемотехнике.

Принцип работы триггера состоит в том, что по переднему фронту счетного импульса первых синхронизируемый RS-триггер переписывает состояние второго RS-триггера с инверсией, то есть изменяет состояние на противоположное. По заднему фронту счетного импульса второй RS-триггер переписывает состояние первого триггера один к одному. Обозначение Т-триггера и диаграммы работы приведены на рис. 5.26.

а) б) в)

Рис. 5.26 Т-триггер: а) – принципиальная схема;

б) – условное обозначение; в) – временная диаграмма.

5.2.3 D-триггер (триггер задержки)

а) б) в)

Рис. 5.27 D-триггер: а) – принципиальная схема;

б) – условное обозначение; в) – временная диаграмма.

D – информационный вход, С – вход синхронизации. D-триггер записывает, по переднему фронту импульса синхронизации, информация с D входа в первый синхронизируемый RS-триггер. По заднему фронту импульса синхронизации информация переписывается во второй триггер и появляется на выходе. В синхронизируемых схемах информация может использоваться только в следующем такте.