- •Логічна організація однокристалевих мікроконтролерів сімейства кр1816ве51.

- •P37 – rd – вихід сигналу зчитування із зовнішньої пам'яті даних;

- •3 Архітектура мікроконтроллера Збільшена структурна схема мк показана на рис.2, а модель для програміста на рис.3.

- •Режим 1 роботи т/с

- •Режим 2 роботи т/с

- •Режим 3 роботи т/с

- •Блок послідовного інтерфейсу переривань

- •4 Системи команд

- •5 Приклади програмування

- •5.3.2 Обчислення квадратного корня

Зміст

Логічна організація однокристалевих мікроконтролерів сімейства КР1816ВЕ51....................1

Архітектура мікроконтроллера......................................................................................................3

Таймери/лічильник. Регістри TMOD i TCON...............................................................................7

Блок послідовного інтерфейсу переривань...................................................................................9

Призначення розрядів регістра SCON..........................................................................................10

Системи команд..............................................................................................................................12

Приклади програмування...............................................................................................................21

Контроль часу при роботі з зовнішніми пристроями .................................................................33

Список уживаних скорочень.........................................................................................................36

Логічна організація однокристалевих мікроконтролерів сімейства кр1816ве51.

1. Загальна характеристика сімейства мікроконтролерів

В даному розділі в якості базової розглядається мікросхема КР1816ВЕ51. Організація й система команд цієї мікросхеми аналогічні мікросхемам ВЕ31, ВЕ751 цієї ж серії, а також мікросхемам ВЕ31 і ВЕ51 серії КР1830. Відмінність мікросхем складається в організації внутрішньої (резидентної) пам'яті програм (ВПП) і величині току споживання (табл.2.1).

Таблиця 1

|

МК |

Об'єм ВПП, байт |

Тип ВПП |

Ток споживання, mA |

|

КР1816ВЕ31 |

Немає |

Немає |

150 |

|

КР1816ВЕ51 |

4К |

ПЗП |

150 |

|

КР1816ВЕ751 |

4К |

ППЗП |

220 |

|

КР1830ВЕ31 |

Немає |

Немає |

18 |

|

КР1830ВЕ51 |

4К |

ПЗП |

18 |

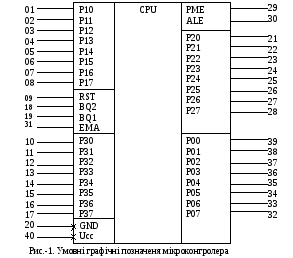

Умовні графічні позначення й позначення виходів мікроконтролера

Умовне графічне позначення мікросхеми показано на рис. 2.1.

МК конструктивно розташований у корпусі з 40 зовнішніми виходами.

Нижче наводяться символічні імена виходів (сигналів).

GND – загальний;

Ucc – напруга живлення +5В;

BQ1 – вхід для підключення зовнішнього джерела синхронізації (для серії КР1830) або кварцевого резонатора;

BQ2 -- вхід для підключення зовнішнього джерела синхронізації (для серії КР1816) або кварцового резонатора;

RST – вхід сигналу загального переходу у висхідне становище.

EMA – вхід дозволу зовнішньої пам'яті; вхід для подачі імпульсів при програмуванні ППЗУ.

RME – дозвіл читання зовнішньої пам'яті програм;

ALE – строб адреса зовнішньої пам'яті

P0 – 8-розрядний двонаправлений порт уводу-виводу;

P1, P2, P3 – 8-розрядні квазідвонаправлені порта вводу-виводу;

Кожна лінія порта Р3 має альтернативну функцію:

P30 – RxD – вхід послідовного порту;

P31 – TxD – вихід послідовного порту;

P32 – INT0 – вхід 0 сигналу запросу переривання від зовнішнього джерела;

P33 – INT1 – вхід 1 сигналу запросу переривання від зовнішнього джерела;

P34 – T0 – вхід лічильника зовнішніх подій Т/С 0;

P35 – T1 – вхід лічильника зовнішніх подій Т/С 1;

P36 – WR – вихід сигналу запису у зовнішню пам'ять даних;

P37 – rd – вихід сигналу зчитування із зовнішньої пам'яті даних;

По електричним параметрам всі сигнали електрично сумісні із сигналом мікросхем, виконаним по технології ТТЛ.

3 Архітектура мікроконтроллера Збільшена структурна схема мк показана на рис.2, а модель для програміста на рис.3.

Виходи сигналів керування

та синхронізації

…

…

МК містить резидентну пам'ять програм (РПП), резидентну пам'ять даних (РПД), пристрій керування та синхронізації, яке містить лічильник команд (РС) і регістр команд, арифметично-логічний блок, в склад якого входить акумулятор А, регіст-розширювач В та інші регістри. МК містить також блок таймерів/лічильників, блок послідовного інтерфейсу й переривань і регістр слова стану програми (PSW). Обмін даними виконується через порти Р0, Р1, Р2, Р3, а також універсальний асинхронний прийомопередатчик (УАПП).

Пам'ять програм і пам'ять даних у мікроЕОМ розділені. Максимальний адресний простір пам'яті програм складає 64Кбайт (рис.4). Пам'ять програм розділяється на резидентну (находиться всередині мікросхеми) і зовнішню, для реалізації якої потрібні додаткові мікросхеми пам'яті. РПП являє собою ПЗП, місткістю 4Кбайт (адреси від 0 до 0FFFh). РПП може бути відключена шляхом подачі рівня на вхід ЕМА. Зауважимо, що в МК 1816ВЕ31 і 1830ВЕ31 внутрішня пам'ять програм відсутня. Адреси 0, 3, 0Bh, 13h, 1Dh i 23h мають спеціальне призначення. З адреси 0 починає виконуватись програма по системному збросу. Інші із указаних комірок призначені для зберігання початкових команд програм обслуговування переривань від зовнішніх сигналів, від таймерів/лічильників та від послідовного порту.

При звертанні до зовнішньої пам'яті програм старший байт адреси передається через порт Р2. Видача молодшого байта адреси і передача байта даних виконується через порт Р0 у режимі внутрішнього мультиплексування.

Адресація операндів у пам'яті програм – безпосередня або косвенна базова індексна. В першому випадку з пам'яті програми вибирається константа, явно задана в команді. Наприклад, при виконанні конструкції MOV R2,#15 у регістр пересилається константа (0Fh). У другому випадку в якості індексного регістру використовується акумулятор, а в якості базового – регістр-покажчик даних DPTR або лічильник команд РС. Зчитування операндів виконується командами MOVC.

-

7F

7E

7D

7С

7В

7А

79

78

77

76

75

74

73

72

71

70

6F

6E

6D

6C

6B

6A

69

68

67

66

65

64

63

62

61

60

5F

5E

5D

5C

5B

5A

59

58

57

56

55

54

53

52

51

50

4F

4E

4D

4C

4B

4A

49

48

47

46

45

44

43

42

41

40

3F

3E

3D

3C

3B

3A

39

38

37

36

35

34

33

32

31

30

2F

2E

2D

2C

2B

2A

29

28

27

26

25

24

23

22

21

20

1F

1E

1D

1C

1B

1A

19

18

17

16

15

14

13

12

11

10

0F

0E

0D

0C

0B

0A

09

08

07

06

05

04

03

02

01

00

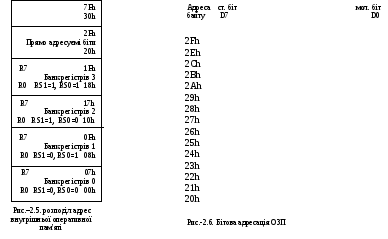

Пам'ять даних як і пам'ять програм розподіляється на внутрішню (резидентну) і зовнішню(ЗПД). Резидентна пам'ять даних складається з двох областей – 128 байт ОЗП з адресами 0-7Fh і регістрів спеціальних функцій (адреси 80--0FFh). ОЗП містить 4 банка регістрів загального призначення (рис.5). Вибір банка 0-3 визначається значенням двох біт PSW (RS1, RS0). Команди програми можуть звертатись до регістрів будь-якого банка по іменам R7-R0, тобто з використанням прямої регістрової адресації. Це дозволяє зекономити пам'ять програм, так як команди, що працюють із регістрами коротші інших аналогічних команд.

Наступні 16 байт ОЗП утворюють область комірок, в яких можлива побітова адресація (рис. 6). До ячейок даної області зручно звертатись за допомогою спеціальних команд роботи з бітами, використовуючи при цьому пряму адресацію. До кожного біта на мові асемблера можна звертатись двома способами. Наприклад, встановити, визначивши молодший байт області (рис.6)

як Pr EQU 20h, встановити старший біт цього байта можна за допомогою команди SETB Pr.7. Аналогічний результат отримується якщо безпосередньо визначити потрібний біт:

BitZ EQU 7

SETB BitZ.

Доступ до всіх байтів ОЗП Можливий за допомогою косвенної регістрової або прямої адресації. В першому випадку в якості покажчиків використовуються регістри R0, R1 вибраного банка регістрів. Приклад

MOV @R1, 23h ілюструю обидва види адресації. Тут виконується пересилка вмісту комірки за адресою 23h в комірку, адреса, котрої записана в регістрі R1.

Область регістрів спеціальних функцій містить акумулятор АСС, регістр-розширювач акумулятора В, покажчик стека SP, слово стану програми PSW, DPTR, замки портів, регістри таймерів/лічильників, буфер прийомопередатчика і регістри керування. Ці регістри допускають лише пряму адресацію. Одинадцять байт цієї області допускають як байтову, так побітову адресацію. Адреси регістрів спеціальних функцій наведено на рис.3, причому регістри, адреси яких помічено знаком (*), допускають адресацію окремих бітів. На рис.3 наведено приклад адресації біт регістра TCON.

Зовнішня пам'ять даних реалізується за допомогою додаткових мікросхем пам'яті і може мати ємність до 64Кбайт з адресами 0 – FFFFh. Адресні простори внутрішньої й зовнішньої пам'яті даних не пересікаються, так як доступ до зовнішньої пам'яті виконується за допомогою спеціальних команд MOVX. Звертання до зовнішньої пам'яті виконується лише з використанням косвенної адресації по регістрам R0, R1 ( команди MOVX A,@Ri i

MOVX @Ri,A) або по регістру-покажчику даних ( команди MOVX A,@DPTR i MOVX @DPTR,A). В першому випадку буде формуватись 8-розрядна адреса, у другому – 16-розрядна. Видача адреси й передача байта даних виконується аналогічно зовнішній пам'яті програм через порти Р0 та Р2.

Акумулятор А є 8-розрядним регістром, який використовується в якості отримувача або джерела операнда. Крім того, акумулятор входить в область регістрів спеціальних функцій з прямою адресацією і позначається як АСС. Наприклад, встановити 3-й біт акумулятора можна командою SETB ACC.3.

Регістр В використовується при операціях множення та ділення. Для інших операцій може розглядатись як додатковий регістр.

Регістр стану програми PSW використовується для зберігання інформації про стан АЛП при виконанні програми. Список розрядів регістра наведено на рис.3. Біт переносу С установлюється апаратно, якщо в старшому розряді результату виникає перенос або зайом. Біт АС установлюється апаратно при появі аналогічної умови в біті 3 результату. Біт переповнення OV фіксує арифметичне переповнення при операціях над цілими числами зі знаком. Біт Р є доповненням умісту акумулятора по парності. Усі біти окрім Р доступні програмно по запису та зчитуванню (останній можна лише зчитувати).

Покажчик стека SP може адресувати будь-яку область РПД і використовується для зберігання адреси комірки стеку, до якої було останнє звернення. В висхідному положенні в SP завантажується код 7.

Формат регістра керування потужністю PCON визначається серією МК. Для серії 1816 регістр має лише один біт SMOD, керуючий швидкістю передачі послідовного порта. Якщо вказаний біт встановлено, то швидкість подвоюється.

Для серії 1830 регістр PCON додатково містить 4 біта (рис.4). Біти GF1, GF0 користувач може використовувати на власний розсуд. Установка біта IDL (PCON.0) призводить до переводу МК в режим холостого ходу, коли блокуються функціональні вузли арифметично-логічного блока й вузли, пов'язані з вибіркою команд, що зменшує енергоспоживання. При цьому зберігаються стани регістрів спеціальних функцій і РПД. Режим холостого ходу закінчується при активації будь-якого дозволеного переривання або при апаратному переході в початкове положення по входу RST.

При встановленні біта PD (PCON.1) МК переходить в режим мікроживлення. Задаючий генератор виключається, що призводить до закінчення роботи всіх вузлів МК. Зберігається лише вміст РПД. Виходом з такого режиму є апаратний перехід у початкове положення.

Таймери/лічильник. Регістри TMOD i TCON

Два 16-розрядних таймери/лічильника (Т/С0 та Т/С1) використовуються для отримання програмно керованих короткочасних затримок і підрахунку зовнішніх подій. Кожен із них складається з двох 8-розрядних регістрів (старшого Tнi та молодшого TLi). При роботі в якості таймера вміст Т/С інкрементується в кожному машинному циклі (з частотою fг/12, де fг – частота задаючого генератора, так як машинний цикл складається з 12-ти періодів чистоти синхронізації). При роботі в якості лічильника вміст Т/С інкрементується при переході з 1 в 0 зовнішнього сигнала, що подається на вхід Т1 (Т0). Максимальна частота зовнішнього вхідного сигнала складає fг/24.

Для керування режимами роботи Т/С і для організації взаємодії таймерів з системою переривання використовуються два регістри спеціальних функцій TMOD i TCON. Формати цих регістрів наведено на рис. 3.

Розряди С/Т регістра режимів таймера TMOD визначає роботу в якості таймера (С/Т=0) або лічильника (С/Т=1). Біти М1, М0 визначають режим роботи Т/С (режими 0-3). Розряди GATE дозволяють керувати таймером/лічильником від зовнішнього сигналу (INT1 для Т/С1 і INT0 для Т/С0). Таке керування дозволяється при GATE=1.

Призначення розрядів регістру керування/статусу таймера TCON:

TF (TCON.7), TF0 (TCON.5) – прапорці, що встановлюються програмно,а також апаратурно при переповненні таймерів 1 та 0. Якщо переривання від відповідного Т/С дозволено, установка прапорця викличе переривання. Прапорці можуть скидається програмно, а також апаратно при передачі керування програмі обробки відповідного переривання:

TR1(TCON.6), TR0(TCON.4) – біти включення таймерів 1 та 0. Установлюються та скидаються програмно.

Решта 4 біта регістра TCON використовуються для керування перериваннями від зовнішніх сигналів INT1 i INT0:

IT(TCON.2), IT0(TCON.0) – біти, що визначають вид переривання по входам INT1 i INT0. Якщо ІТ=0, то дозволено переривання по низькому рівню сигнала. При ІТ=1 переривання по зрізу сигнала (перехід з 1 в 0). Встановлюється й скидається програмно;

IE1(TCON.3), IE0(TCON.1) –Прапорці запросу зовнішніх перериваннь.встановлюються апаратно по рівню (зрізу) зовнішніх сигналів або програмно. Скидаються апаратно при обслуговуванні переривання, котре було викликано фронтом сигналу. При перериванні по рівню скид прапорця ІЕ має виконувати програма обслуговування переривання, діючи на джерело переривання для зняття їм запросу.

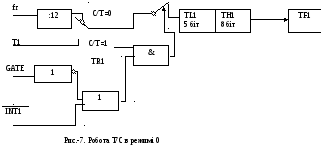

Режим 0 роботи Т/С

Визначається установкою бітів М1=0, М0=0 регістру TMOD. Логіка роботи на прикладі Т/С1 у режимі 0 показана на рис.7. Т/С являє собою 13-розрядний лічильник (послідовно з'єднані 5-розрядний TL1 та 8-розрядний TH1). В залежності від призначення розряду С/Т1 регістра TMOD на вхід лічильника поступають зовнішні сигнали зі входу Т1 (лічильник) або сигнал fг/12 (таймер). Відлік починається при установці біта TR регістра TCON. При необхідності керування рахуванням із зовні встановлюють біт GATE регістра TMOD.

Тоді відлік дозволено при значенні вхідного сигналу INT1=1 і заборонений при INT0=0. При переповненні Т/С установлюється прапорець TF1.