- •Микропроцессорные системы

- •Аппаратные средства поддержки реального и календарного времени в микропроцессорных и микроконтроллерных системах (таймеры и процессоры событий).

- •Организация подсистем прерываний в микропроцессорных и микроконтроллерных системах.

- •Основные функции инструментальных пакетов проектирования промышленных систем автоматизации и управления (на примерах инструментального пакета step7 или любого иного).

- •Открытые магистрально модульные системы. Основные требования к открытым системам реального времени. Стандарты мэк 61131.

- •Сегментация памяти в реальном и защищенном режимах микропроцессоров архитектуры ia-32.

- •Обмен данными в режиме пдп микропроцессорных и микроконтроллерных системах. Организация подсистем пдп.

- •Для микроконтроллеров к1816ве51 или st7, stm8, stm32 поясните и продемонстрируйте примерами программирование режимов работы таймеров/счетчиков.

- •Поясните модульный принцип построения микроконтроллеров, компоненты процессорного ядра, состав и характеристики модулей. Примеры архитектур реальных микроконтроллеров.

- •Архитектура микропроцессоров Intel p6 и р7. Конвейеризация вычислительных процессов, использование кэш-памяти программ и данных, предсказание ветвлений и спекулятивное выполнение.

- •Организация вода – вывода данных в микропроцессорных системах.

- •Для микроконтроллеров к1816ве51 или st7, stm8, stm32 поясните и продемонстрируйте примерами адресацию данных и команд, адресацию стека, выполнение косвенных переходов в программе.

- •Основные требования к открытым системам реального времени. Стандарты мэк 61131. Языки программирования плк. Стандарты мэк 61131.3.

- •Программируемые логические контроллеры (плк). Принципы работы плк сканирующего типа. Рабочие циклы и время реакции плк.

- •Организация подсистем прерываний в мп системах на микроконтроллерах платформы х86, Pentium.

- •Микропроцессоры платформы х86, Pentium: управление виртуальной памятью, средства защиты памяти.

- •Средства и методы разработки программного обеспечения и его отладки микроконтроллерных систем. Интегрированные среды проектирования.

- •Для микроконтроллеров к1816ве51 или st7, stm8, stm32 поясните и продемонстрируйте примерами ввод и вывод данных в параллельном и последовательном кодах.

- •Способы обмена данными в микропроцессорных системах. Пояснение выполните на примерах структурных схем и фрагментах программ обмена.

- •Какие способы обмена данными применяются в микропроцессорных системах. Поясните на примерах структурных схем и фрагментах программ обмена.

- •Основные функции инструментальных пакетов проектирования промышленных систем автоматизации и управления (на примерах инструментального пакета step7 или любого иного).

- •Системное и прикладное программное обеспечение магистрально-модульных систем.

- •Аппаратные средства поддержки реального и календарного времени в микропроцессорных и микроконтроллерных системах (таймеры и процессоры событий).

- •Ввод/ вывод информации в последовательных кодах: проблемы, примеры использования программируемых аппаратных средств, надежность и долговечность.

Микропроцессоры платформы х86, Pentium: управление виртуальной памятью, средства защиты памяти.

Виртуа́льная па́мять (англ.Virtual memory) — технология управления памятью ЭВМ, разработанная для многозадачных операционных систем. При использовании данной технологии для каждой программы используются независимые схемы адресации памяти, отображающиеся тем или иным способом нафизические адресав памяти ЭВМ. Позволяет увеличить эффективность использования памяти несколькими одновременно работающими программами, организовав множество независимыхадресных пространств(англ.), и обеспечитьзащиту памятимежду различными приложениями. Также позволяет программисту использовать больше памяти, чем установлено в компьютере, за счет откачки неиспользуемыхстраницна вторичное хранилище

При использовании виртуальной памяти упрощается программирование, так как программисту больше не нужно учитывать ограниченность памяти или согласовывать использование памяти с другими приложениями. Для программы выглядит доступным и непрерывным все допустимое адресное пространство, вне зависимости от наличия в ЭВМ соответствующего объёма ОЗУ.

Применение механизма виртуальной памяти позволяет:

упростить адресацию памяти клиентским программным обеспечением;

рационально управлять оперативной памятью компьютера (хранить в ней только активно используемые области памяти);

изолировать процессы друг от друга (процесс полагает, что монопольно владеет всей памятью).

Страничная память — способ организации виртуальной памяти, при котором единицей отображения виртуальных адресов на физические является регион постоянного размера (т. н. страница). Типичный размер 4096 байт, для некоторых архитектур до 128 КБ.

Страничная организация памяти обеспечивается только в защищенном режиме. Для ее реализации необходимо с помощью команды LMSW или MOV CR0 установить в регистре CR0 значение бита страничной адресации PG=1. При этом сегменты делятся на отдельные страницы емкостью 4 Кбайт или 4 Мбайт, размещаемые в различных позициях адресного пространства ОЗУ. Страницы могут группироваться в разделы. Размещение разделов и страниц в ОЗУ производится диспетчером памяти, входящим в состав операционной системы. Диспетчер задает базовые адреса разделов и страниц, которые хранятся в памяти в виде адресных таблиц. При использовании страничной организации блоки трансляции адреса, входящие в состав процессора, преобразуют адрес, сформированный MIU (при выборке операнда) или блоком выборки-декодирования (при выборке команды), в реальный физический адрес байта или слова. В процессе этого преобразования, который называется страничной трансляцией адреса, блок трансляции обращается к хранящимся в ОЗУ адресным таблицам. Чтобы уменьшить число таких обращений и повысить производительность процессора, базовые адреса 32 страниц памяти команд и данных, к которым выполнялись последние обращения, записываются во внутренние буферы трансляции адреса (TLB). При обращении к этим страницам их базовые адреса считываются из буфера, поэтому формирование физического адреса происходит существенно быстрее.

Страничная трансляция позволяет расширить объем адресуемой памяти до 64 Гбайт, используя 36-разрядную шину адреса. Такая возможность реализуется, если установить в регистре управления CR4 значение бита РАЕ=1. При этом в адресных таблицах задаются 36-разрядные базовые адреса разделов и страниц, а размер страниц может составлять 4 Кбайт или 2 Мбайт.

СРЕДТСВА ЗАЩИТЫ ПАМЯТИ

Процессоры Р6 имеют специальные средства, обеспечивающие в защищенном режиме защиту от случайного (непредусмотренного решаемой задачей) обращения к сегментам и страницам, хранящимся в памяти. Система защиты предусматривает различные виды контроля, которые реализуются процессором:

• контроль доступа к сегментам и страницам, который обеспечивается описанной ниже системой привилегий;

• контроль использования сегментов и страниц, который вводит ряд ограничений на возможные виды обращения к ним: запрещение записи в сегменты данных (страницы), разрешенные только для чтения, запрещение чтения сегментов программ (страниц), разрешенных только для выполнения, запрещение обращения к незагруженным (отсутствующим) сегментам и страницам и ряд других;

•ограничение набора выполняемых команд в зависимости от уровня привилегий выполняемой программы (выделение привилегированных команд).

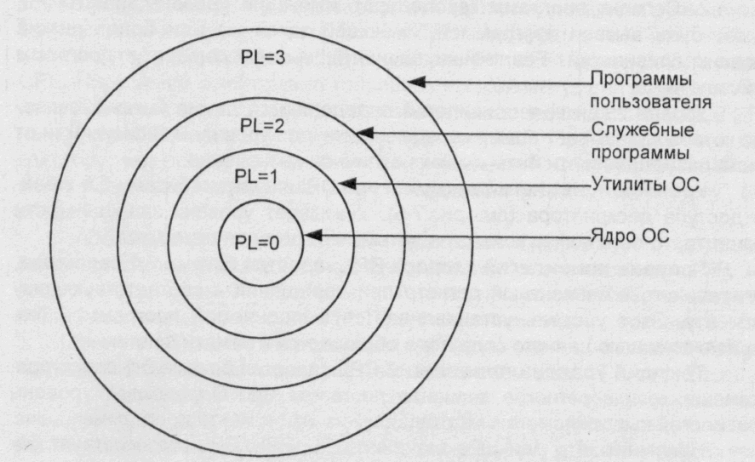

Для защиты информации, хранящейся в сегментах памяти, используется система привилегий, которая регулирует доступ к тому или иному сегменту в зависимости от уровня его защищенности и от степени важности (привилегированности) запроса. В процессорах Р6, так же как в более ранних моделях 80286, 80386, 80486, Реntium установлены четыре уровня привилегий РL (privilege level), которые задаются номерами от 0 до 3. Наиболее привилегированным является уровень с меньшим номером. Степень защищенности сегмента так же имеет четыре уровня, которые схематически представляются в виде вложенных колец защиты (рис. 16.1).

Рис. 16.1. Уровни привилегий и защиты

Соответствующие уровни защищенности иллюстрируются на примере сегментов программ. Наименее защищенными (привилегированными) являются прикладные программы пользователя, для которых выделяется уровень с номером РL=3. Уровни с номерами РL=0, 1, 2 отводятся для системных программ (супервизора), которые можно разделить на три уровня в зависимости от требований к их защищенности. Наиболее защищенная часть — ядро операционной системы (ОС) имеет уровень РL=0. В ядро входит часть ОС, обеспечивающая инициализацию работы, управление доступом к памяти, защиту и ряд других жизненно важных функций, нарушение которых полностью выводит систему из строя. Основная часть программ ОС (утилиты) должна иметь уровень РL=1. К уровню РL=2 обычно относят ряд служебных программ ОС, например, драйверы внешних устройств, системы управления базами данных, специализированные подсистемы программирования и другие.

Для программ с различными уровнями привилегий организованы отдельные стеки. Таким образом, в системе, использующей все четыре уровня привилегий, функционируют четыре различных стека, каждый из которых обслуживает только программы соответствующего уровня. При передаче управления программе другого уровня производится переключение стеков.

В соответствии с уровнями привилегий и защищенности установлены следующие правила доступа для сегментов программ и данных.

1. Данные из сегмента, имеющего уровень защиты РL могут быть выбраны программой, имеющей такой же или более высокий уровень привилегий.

2. Сегмент программ (процедура), имеющий уровень защиты РL может быть вызван программой, имеющей такой же или более низкий уровень привилегий. Различные варианты вызова сегментов программ описаны ниже.

Уровни защиты и привилегий определяются двумя битами, значение которых указывает номер кольца защиты или уровня. В зависимости от места размещения эти биты имеют различное назначение.

Уровень привилегий дескриптора DPL. задается битами 5,6 в байте доступа дескриптора. Указывает уровень защищенности сегмента, то есть номер кольца защиты, к которому он относится.

Уровень привилегий запроса RPL задается битами 0,1 селектора, загружаемого в сегментный регистр. Этот уровень устанавливается выполняемой программой, которая с помощью данного селектора обращается к памяти системы.

Текущий уровень привилегий CPL задается битами 0,1 селектора, размещенного в регистре сегмента программ СS. Определяет уровень привилегий выполняемого в настоящий момент сегмента программы.

Чтобы избежать частых нарушений хода выполнения программы из-за несоблюдения правил доступа к сегментам, в набор команд процессора введены специальные команды, используемые для проверки различных условий доступа. Команда LAR осуществляет загрузку в регистр байта доступа сегмента, выбираемого с помощью селектора, который содержится в адресуемой ячейке памяти или регистре. После этой операции процессор может произвести побитный анализ содержимого байта доступа, определяя возможности обращения к данному сегменту.