- •Микропроцессорные системы

- •Аппаратные средства поддержки реального и календарного времени в микропроцессорных и микроконтроллерных системах (таймеры и процессоры событий).

- •Организация подсистем прерываний в микропроцессорных и микроконтроллерных системах.

- •Основные функции инструментальных пакетов проектирования промышленных систем автоматизации и управления (на примерах инструментального пакета step7 или любого иного).

- •Открытые магистрально модульные системы. Основные требования к открытым системам реального времени. Стандарты мэк 61131.

- •Сегментация памяти в реальном и защищенном режимах микропроцессоров архитектуры ia-32.

- •Обмен данными в режиме пдп микропроцессорных и микроконтроллерных системах. Организация подсистем пдп.

- •Для микроконтроллеров к1816ве51 или st7, stm8, stm32 поясните и продемонстрируйте примерами программирование режимов работы таймеров/счетчиков.

- •Поясните модульный принцип построения микроконтроллеров, компоненты процессорного ядра, состав и характеристики модулей. Примеры архитектур реальных микроконтроллеров.

- •Архитектура микропроцессоров Intel p6 и р7. Конвейеризация вычислительных процессов, использование кэш-памяти программ и данных, предсказание ветвлений и спекулятивное выполнение.

- •Организация вода – вывода данных в микропроцессорных системах.

- •Для микроконтроллеров к1816ве51 или st7, stm8, stm32 поясните и продемонстрируйте примерами адресацию данных и команд, адресацию стека, выполнение косвенных переходов в программе.

- •Основные требования к открытым системам реального времени. Стандарты мэк 61131. Языки программирования плк. Стандарты мэк 61131.3.

- •Программируемые логические контроллеры (плк). Принципы работы плк сканирующего типа. Рабочие циклы и время реакции плк.

- •Организация подсистем прерываний в мп системах на микроконтроллерах платформы х86, Pentium.

- •Микропроцессоры платформы х86, Pentium: управление виртуальной памятью, средства защиты памяти.

- •Средства и методы разработки программного обеспечения и его отладки микроконтроллерных систем. Интегрированные среды проектирования.

- •Для микроконтроллеров к1816ве51 или st7, stm8, stm32 поясните и продемонстрируйте примерами ввод и вывод данных в параллельном и последовательном кодах.

- •Способы обмена данными в микропроцессорных системах. Пояснение выполните на примерах структурных схем и фрагментах программ обмена.

- •Какие способы обмена данными применяются в микропроцессорных системах. Поясните на примерах структурных схем и фрагментах программ обмена.

- •Основные функции инструментальных пакетов проектирования промышленных систем автоматизации и управления (на примерах инструментального пакета step7 или любого иного).

- •Системное и прикладное программное обеспечение магистрально-модульных систем.

- •Аппаратные средства поддержки реального и календарного времени в микропроцессорных и микроконтроллерных системах (таймеры и процессоры событий).

- •Ввод/ вывод информации в последовательных кодах: проблемы, примеры использования программируемых аппаратных средств, надежность и долговечность.

Сегментация памяти в реальном и защищенном режимах микропроцессоров архитектуры ia-32.

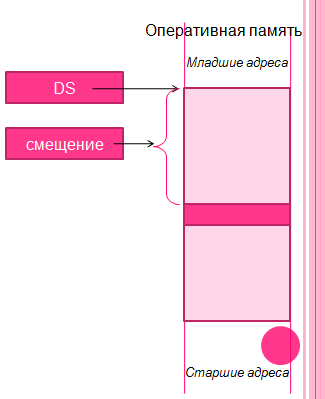

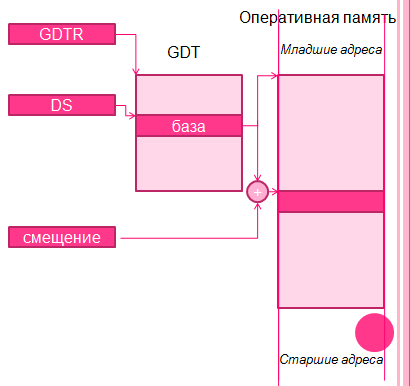

Сегментация — механизм адресации, обеспечивающий существование нескольких независимых адресных пространств как в пределах одной задачи, так и в системе в целом для защиты задач от взаимного влияния. В основе механизма сегментации лежит понятие сегмента, который представляет собой независимый поддерживаемый на аппаратном уровне блок памяти. Для процессоров Intel, начиная с i8086, принят особый подход к управлению памятью. Каждая программа в общем случае может состоять из любого количества сегментов, но непосредственный доступ она имеет только к трем основным сегментам (кода, данных и стека), а также к дополнительным сегментам данных числом от одного до трех. Программа заранее не знает, по каким физическим адресам будут размещены ее сегменты. Этим занимается операционная система. Операционная система размещает сегменты программы в оперативной памяти по определенным физическим адресам, после чего помещает значения этих адресов в определенные места. Куда именно, зависит от режима работы процессора. Так, в реальном режиме эти адреса заносятся непосредственно в соответствующие сегментные регистры, а в защищенном режиме они попадают в элементы специальной системной таблицы дескрипторов. Внутри сегмента программа обращается к адресам относительно начала сегмента линейно, то есть начиная с 0 и заканчивая адресом, равным размеру сегмента. Этот относительный адрес, или смещение, который процессор использует для доступа к данным внутри сегмента, называется эффективным. Отличия моделей сегментированной организации памяти в различных режимах хорошо прослеживаются на схеме (рис. 1.3). Различают три основных модели:

сегментированная модель памяти реального режима;

сегментированная модель памяти защищенного режима;

сплошная модель памяти защищенного режима.

Сегментация памяти обеспечивается при любом режиме работы процессора. Сегментация реализуется путем разбиения адресного пространства на отдельные блоки — сегменты, доступ к которым производится в соответствии с определенными правилами. Сегментированная память представляет собой набор блоков, характеризуемых определенными атрибутами — такими, как расположение, размер, тип (стек, программа, данные), характеристика защиты. В системе на основе процессора Р6 каждой задаче доступны до 8192 сегментов величиной до 4 Гбайт каждый. Таким образом обеспечивается возможность использования до 64 Тбайт виртуальной памяти. Для обращения к ячейке сегментированной памяти используется составной (логический) адрес, который состоит из селектора, задающего базовый адрес сегмента (начало), и относительного адреса ячейки (байта, слова) в сегменте. Арифметическое сложение базового и относительного адреса дает физический (линейный) адрес байта или слова (одинарного, двойного или счетверенного). Правила определения базового адреса сегмента зависят от режима работы микропроцессора — реальный или защищенный.

Сегментная организация памяти в реальном режиме

Вся память делится на сегменты

Адреса сегментов хранятся в сегментных регистрах, деленные на 16

Виртуальный адрес ячейки представляет собой комбинацию сегмент:смещение

Физический адрес ячейки вычисляется как сегмент*16+смещение

Сегментная организация памяти в защищенном режиме

Используются 32-х разрядные адреса начал сегментов (базы) и смещения

Для хранения баз сегментов используются таблицы дескрипторов сегментов

Выбор дескриптора осуществляется по его номеру (селектору) хранящемуся в сегментном регистре

Линейный адрес формируется как база+смещение