umm_7154

.pdfили принцип обоймы, при котором данные считываются в порядке, обратном порядку записи, то память носит название стековой.

В адресной памяти для доступа к данным используются адреса ячеек. Адресные запоминающие устройства делятся на оперативные (ОЗУ), или память с произвольным доступом (RAM – Random Access Memory) и постоянные (ПЗУ), или память только для чтения (ROM – Read Only Memory).

Данные считываются и записываются в ОЗУ во время выполнения программы, но при выключении питания память очищается, а данные утрачиваются. В ПЗУ данные сохраняются после выключения питания, но запись в такую память имеет ряд ограничений.

ОЗУ делятся на статические (SRAM – Static RAM) и динамические (DRAM – Dynamic RAM).

Программирование ПЗУ выполняется в процессе производства, либо пользователем. ПЗУ с возможностью многократного перепрограммирования пользователем носят название репрограммируемых. Наибольшее распространение имеют следующие виды ПЗУ:

–масочные (MROM – Mask ROM);

–репрограммируемые с ультрафиолетовым стиранием (РПЗУ-УС) или EPROM (Erasable Programmable ROM);

–однократно программируемые, или OTP (One-Time Programmable);

–репрограммируемые с электрическим стиранием (РПЗУ-ЭС), или EEPROM (Electrically Erasable Programmable ROM);

–Flash-память.

2.11. Статические ОЗУ

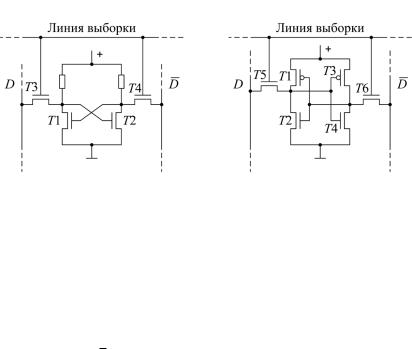

Статические ОЗУ имеют высокую стоимость из-за низкой степени интеграции элементов. Запоминающими элементами статической памяти служат триггеры, которые можно реализовать по любой схемотехнологии (ТТЛ, n-МОП, КМОП и др.). Современные статические запоминающие устройства выполнены по n-МОП (рис. 2.17, а) и КМОП (рис. 2.17, б) технологиям.

Для снижения потребляемой мощности запоминающие элементы SRAM работают в режиме микротоков, чем обусловлена малая мощность выходных сигналов. Эта особенность требует применения чувствительных усилителей (Sense Amplifier).

31

а |

б |

Рис. 2.17. Устройство ячеек статической памяти: а – n-МОП технология; б – КМОП технология

Запоминающий элемент n-МОП (рис. 2.17, а) состоит из RS- триггера на транзисторах T1, T2 и ключей выборки T3, T4. Транзисторы триггера в стоковых цепях имеют высокоомные поликремниевые резисторы, что придает схеме режим микротоков. Доступ к элементам осуществляется путем выставления высокого потенциала на линию выборки. Данные передаются по лини-

ям данных (D, D ).

Запоминающий элемент КМОП (рисунок 2.17, б) также представляет собой RS-триггер, но собранный на четырех транзисторах T1, T2, T3, Т4 и ключах выборки T5, T6.

По плотности интеграции КМОП элементы уступают n-МОП. Недостаток n-МОП заключается в повышенном, по сравнению с КМОП, энергопотреблении в результате наличия статического тока в схеме триггера.

Запоминающие элементы объединяются в строки и столбцы, образуя массив памяти. Длина строки, как правило, превышает разрядность шины данных, массив управляется двумя дешифраторами адреса: дешифратором строк (Row Decoder) и дешифратором столбцов (Column Decoder). Такая организация массива позволяет упростить схему адресации. Например, для адресации 1K слов потребовался бы дешифратор с 1024 выходами или два дешифратора по 32 выхода у каждого.

Устройство 4-разрядной SRAM памяти показано на рис. 2.18.

32

Рис. 2.18. Устройство 4-разрядной SRAM

Шина адреса разделена на две части. Часть проводов шины адреса подается на дешифратор строк, другая на дешифратор столбцов. После выставления адреса выполняется обращение к запоминающим элементам, на линию выборки подается высокий потенциал, который открывает ключи во всей строке. При чтении выходы триггеров подключаются к столбцовым линиям чтения-записи, чувствительные усилители через эти линии считывают состояние триггера.

Чувствительные усилители представляют собой усилители с дифференциальным входом. В основном чувствительные усилители строятся на основе триггеров (например так, как показано на рис. 2.19).

33

Рис. 2.19. Схема чувствительного усилителя

При выборке запоминающего элемента на линиях чтения-за- писи устанавливаются сохраненные значения, на затворах транзисторов T1, T2 и T3, T4 появляется разница потенциалов. Но питание триггера отключено (транзистор T 7 заперт), поэтому триггер не функционирует. При подаче сигнала чтения транзистор T 7 открывается, подавая питание на триггер, а T5 и T6 закрываются, отключая триггер от запоминающего элемента. Триггер переходит в одно из стабильных состояний, определяемое созданной разницей потенциалов. Соответствующий логический уровень передается на выход запоминающего устройства.

При записи к линиям столбцов подключаются дифференциальные выходы схемы записи (рис. 2.20), транзисторы в цепях записи более мощные, чем транзисторы RS-триггера запоминающего элемента, что приводит к перезаписи данных в ячейке.

Когда операция чтения или записи закончена на линии выборки устанавливается низкий потенциал, ключи выборки отключают запоминающий элемент от всех других схем запоминающего устройства.

34

Рис. 2.20. Схема записи SRAM

2.12.Динамические ОЗУ

В1968 году Роберт Деннард получил патент на изобретение динамической памяти, а первые микросхемы DRAM выпущены

в1973 году.

Вдинамических запоминающих устройствах данные хранятся в виде зарядов емкостей МОП-структур. Запоминающий элемент DRAM значительно проще статического, что позволяет разместить на кристалле намного больше запоминающих элементов (в 4–5 раз).

Каждая ячейка DRAM (рис. 2.21) состоит из одного МОП транзистора и конденсатора, позволяет хранить один бит данных в виде заряда.

Рис. 2.21. Ячейка динамической памяти

Наличие заряда на конденсаторе соответствует логической единице, отсутствие – логическому нулю.

35

Использование конденсатора как элемента памяти имеет ряд недостатков. Для получения быстродействующего запоминающего устройства с большим количеством ячеек и низким энергопотреблением приходится уменьшать емкость конденсаторов. При чтении данных конденсатор разряжается. Кроме того, разряд конденсатора происходит даже тогда, когда он отключен от внешних цепей транзистором. Поэтому для предотвращения потери данных, заряд на конденсаторе должен периодически восстанавливаться схемой регенерации.

Рассмотрим устройство DRAM (рис. 2.22, а) и процесс доступа к ячейкам памяти.

а |

б |

Рис. 2.22. Устройство динамической памяти:

а – структурная схема; б – схема выравнивания и перезарядки

36

Особенность динамических запоминающих устройств заключается в мультиплексировании шины адреса. Адрес делится на две части – адрес строки и адрес столбца матрицы запоминающих элементов. Эти адреса подаются на одни и те же адресные выводы поочередно. Мультиплексирование адресов позволяет уменьшить число выводов микросхемы на половину разрядности адреса.

Массив динамической памяти разделен на две части. Между ними размещены чувствительные усилители так, что каждый столбец оказывается состоящим из двух секций, подключенных

кразным плечам усилителя. Емкость линии, соединяющей запоминающие элементы в каждой половине столбца, многократно превышает емкость конденсатора запоминающего элемента. Перед считыванием, схемой выравнивания напряжений и перезарядки (СВП), производится перезарядка линий столбцов до уровня половины напряжения питания (рис. 2.22, б). При считывании СВП отключается транзисторами T1, T2 и T3. Если запоминающий элемент, хранящий логическую единицу, подключается к линии столбца, то часть заряда стекает на эту линию. Напряжение на соответствующей линии повышается и на входах чувствительного усилителя (ЧУ) фиксируется разность потенциалов. Если запоминающий элемент хранит ноль, то его подключение к линии столбцов вызовет уменьшение напряжения на линии, что будет зафиксировано чувствительным усилителем.

Считывание состояния запоминающего элемента разрушает записанные данные. Поэтому после установки чувствительных усилителей, они выполняют перезаряд запоминающего конденсатора, устанавливая на линиях столбцов соответствующие логические уровни.

Запись в динамическую память также выполняется чувствительными усилителями, только их состояние устанавливается значениями на шине данных.

Доступ к ячейкам динамической памяти выполняется в два этапа. Первый этап включает выбор строки и считывание состояния ячеек в ней. На втором этапе выполняется выбор слова данных, которое переписывается на выход запоминающего устройства.

После подачи адреса на входы запоминающего устройства и стабилизации сигнала устанавливается низкий уровень сигнала RAS (Row Address Strobe) дешифратор выбора строк подает высокий потенциал на затворы всех транзисторов, подключенных

ксоответствующей линии, что приводит к их открытию. На всех

37

остальных линиях при этом устанавливается низкий потенциал и все подключенные к ним транзисторы находятся в закрытом состоянии. Каждая выбранная ячейка подключается к чувствительным усилителям, которые устроены аналогично рассмотренным ранее (рис. 2.19), но выполняют две задачи. Во-первых, считывают информацию с ячеек и передают на выходы запоминающего устройства, во-вторых, служат для записи данных в ячейку. Продолжительность этого этапа занимает большую часть времени адресации динамической памяти. Время, необходимое на выбор строки, определяется продолжительностью открытия транзисторов (зарядом емкости затворов) и длительностью считывания состояния конденсаторов.

На втором этапе подается низкий уровень сигнала CAS (Column Address Strobe) и данные выбранных столбцов с выходов усилителей переписываются на выходы запоминающего устройства.

Важной особенностью динамической памяти, как было указано выше, является необходимость регенерации заряда конденсатора. Кроме восстановления заряда при каждом обращении к ячейке, для компенсации разряда конденсатора токами утечки выполняется периодическая регенерация.

2.13. Масочные ПЗУ

Масочные ПЗУ являются самым дешевым типом памяти, используются для хранения видео игр и данных, не требующих изменений для электронных устройств, таких как шрифты для лазерных принтеров, словари в текстовых процессорах и звуковые данные в электронных музыкальных инструментах.

Программируются масочные ПЗУ на завершающих этапах изготовления интегральной микросхемы. Этот тип запоминающих устройств энергонезависим, т. е. при отключении питания данные не теряются.

В масочных ПЗУ, изготовленных по МОП технологии, элементами памяти являются транзисторы, размещенные на пересечениях строк и столбцов массива памяти (рис. 2.23).

Программирование осуществляется либо по способу формирования перемычек, когда транзистор подключается к столбцу (рис. 2.23, a), либо по способу формирования МОП-транзисто- ров с низким и высоким порогом отпирания (рис. 2.23, б). В микросхемах, изготавливаемых по второму способу, все транзи-

38

сторы соединены с линиями столбцов и строк, но имеют разную толщину подзатворного диэлектрика и, следовательно, разное пороговое напряжение: более низкое у транзисторов с тонким слоем диэлектрика, что соответствует логическому 0, и более высокое у транзисторов с толстым слоем, что соответствует логической 1.

Рис. 2.23. Устройство масочного ПЗУ:

а – программируемого перемычками; б – программируемого формированием транзисторов с разными порогами отпирания

При выставлении адреса на входах запоминающего устройства дешифратор устанавливает высокий логический уровень на требуемой строке. Транзисторы с толстым слоем диэлектрика остаются закрытыми, а на соответствующих выходах запоминающего устройства появляются логические 1. Транзисторы с тонким слоем диэлектрика открываются и на соответствующих выходах появляются логические 0.

Программирование формированием перемычек является наиболее простым и быстрым, состоит из одного завершающего изготовление этапа. Однако размер ячеек будет больше, а степень интеграции элементов ниже, чем при программировании формированием транзисторов.

39

2.14. Элементы энергонезависимой памяти

Основной запоминающий элемент ПЗУ с возможностью перепрограммирования пользователем – транзистор особой конструкции. Концепция такого транзистора впервые предложена Саймоном Мин Зи и Дейвоном Кангом в 1967 году, а первая реализация энергонезависимой памяти на их основе запатентована в 1971 году.

Элемент энергонезависимой памяти представляет собой МОПтранзистор, модифицированный таким образом, чтобы в подзатворном диэлектрике мог храниться электрический заряд. Энергонезависимые элементы делятся на два класса: транзисторы с плавающим затвором (рис. 2.24, а) и транзисторы с двухслойным диэлектриком (рис. 2.24, б).

а |

б |

Рис. 2.24. Энергонезависимые элементы памяти:

а– транзистор с плавающим затвором;

б– транзистор с двухслойным диэлектриком

Транзистор с плавающим затвором может не иметь управляющего затвора.

Заряд хранится либо в плавающем затворе, либо на границе между слоями диэлектрика. Этот заряд, изменяя пороговое напряжение МОП-транзистора, переводит прибор в состояние с высоким порогом включения (рис. 2.25).

При отсутствии заряда в плавающем затворе запоминающий элемент работает как обычный МОП-транзистор. Когда плавающий затвор содержит заряд, для открытия транзистора требуется напряжение, превышающее управляющее. Поэтому транзистор остается закрыт.

40