umm_7154

.pdf

ется битами PS2, PS1, PS0. Управляющие биты PSA, T0CS, T0SE, PS2, PS1, PS0 находятся в регистре OPTION_REG.

3.21. Таймер TMR1

Периферийный модуль TMR1 (рис 3.14) представляет собой 16-разрядный регистр, состоящий из двух 8-разрядных регистров TMR1H и TMR1L.

Рис. 3.14. Структурная схема таймера TMR1

Управление работой TMR1 осуществляется битами регистра T1CON. Включение таймера выполняется установкой бита TM- R1ON. После включения TMR1 значение спаренного регистра инкрементируется (увеличивается на 1) от h’0000’ до h’FFFF’. При переполнении TMR1 флаг TMR1IF в регистре PIR1 устанавливается в 1. Само прерывание можно разрешить или запретить битом TMR1IE в регистре PIE1. Частота тактовых импульсов, управляющих таймером, может быть уменьшена в 2, 4 или 8 раз делителем T1CKPS1:T1CKPS0. Состоянием бита TMR1CS выбирается источник тактовых импульсов. Если TMR1CS = 0, то модуль работает от тактовых импульсов микроконтроллера и увеличивается на 1 в каждом машинном цикле. При работе от внешнего источника импульсов приращение таймера происходит по каждому переднему фронту сигнала на входе T1OSI (если T1OSCEN = 1) или T1OSO (если T1OSCEN = 0). Бит T1OSCEN управляет тактовым генератором TMR1. Внешний тактовый сигнал может быть синхронизи-

81

рован с внутренним тактовым сигналом микроконтроллера, если бит T1SYNC сброшен.

3.22. Таймер TMR2

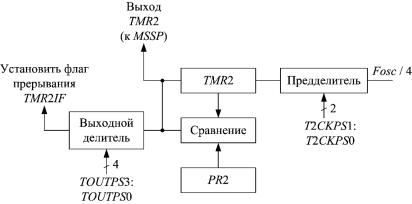

Таймер TMR2 представляет собой 8-разрядный регистр с 2-раз- рядным предделителем, 4-разрядным выходным делителем и 8-разрядным регистром периода PR2 (рис. 3.15).

Рис. 3.15. Структурная схема таймера TMR2

Настройка TMR2 выполняется битами регистра T2CON. Таймер имеет единственный источник тактового сигнала – внутренний тактовый сигнал микроконтроллера (Fosc / 4). Частота тактового сигнала может быть уменьшена предделителем в зависимости от состояния битов T2CKPS0 и T2CKPS1. Для отключения предделителя указанные биты следует обнулить. По каждому импульсу от предделителя содержимое таймера TMR2 увеличивается на 1 от 0 до значения, записанного в PR2. При достижении значения PR2 схема сравнения формирует выходной сигнал, который передается выходному делителю и модулю MSSP для управления скоростью передачи данных. Коэффициент деления выходного делителя настраивается битами TOUTPS0, TOUTPS1, TOUTPS2 и TOUTPS3. Запуск работы таймера выполняется установкой в 1 бита TMR2ON.

Схема работает следующим образом. Перед включением таймера необходимо записать в регистр периода PR2 число импуль-

82

сов, которые будет отсчитывать таймер в каждом цикле. После включения таймера установкой в «1» бита TMR2ON импульсы внутреннего тактового генератора частотой FOSC / 4 проходят через предделитель и поступают на вход регистра-счетчика TMR2. При достижении равенства содержимого регистра периода PR2 и счетчика TMR2 на выходе схемы сравнения вырабатывается сигнал EQ, который обнуляет таймер. Процесс счета начинается заново. Через выходной делитель импульсы EQ поступают на выход таймера и взводят флаг прерывания TMR2IF в регистре PIR1. При этом вызывается прерывание, если оно разрешено установкой в «1» битов GIE и T0IE регистра INTCON и бита TMR2IE в регистре PIE1. Длительность временного интервала T, формируемого таймером, определяется по формуле T = K1·P·K2, где K1 – коэффициент деления предделителя, P– число, записанное в регистр периода PR2, K2 – коэффициент деления выходного делителя.

Сторожевой таймер WDT используется для сброса микроконтроллера в случае программного сбоя. Сторожевой таймер должен обнуляться программно командой CLRWDT. При зависании микроконтроллера, либо невозможности выполнения команды обнуления сторожевого таймера, после его переполнения осуществляется сброс микроконтроллера. Тактирование WDT выполняется отдельным встроенным RC-генератором. Время переполнения сторожевого таймера составляет примерно 18 мс с отключенным делителем.

3.23. Последовательная передача данных

Для организации обмена информацией между микроконтроллерами или элементами микропроцессорных систем с целью сокращения проводов обмен часто организуется в последовательном коде. В этом случае необходимо преобразовывать параллельный код, с которым оперирует процессор, в последовательный при передаче, и соответственно, последовательный код в параллельный при приеме. Такие преобразования выполняются модулями последовательной передачи, основу которых составляют регистры сдвига.

Для правильного приема данных приемник должен определят моменты времени, в которые следует воспринимать очередной бит данных (т. е. требуется синхронизация процессов в передатчике и приемнике). Для этого передатчик и приемник связывают спе-

83

циальной линией синхронизации, либо синхронизируют приемник передаваемым сигналом.

Существуют асинхронные и синхронные протоколы последовательного обмена. При асинхронном обмене символы передаются поодиночке по мере их готовности. Начало и конец передачи выделяются специальными сигналами (стартовые и стоповые биты). Интервал между передаваемыми символами может быть различным, хотя интервалы между битами в одном символе фиксированы. При синхронной передаче символы следуют один за другим слитно. В синхронных протоколах между пересылаемыми символами нет стартовых и стоповых бит. Все биты передаются непрерывным потоком, что увеличивает скорость передачи.

Все устройства, участвующие в синхронном обмене, делятся на ведущие и ведомые. Ведущие устройства формируют сигнал синхронизации, а ведомые получают синхросигнал от ведущих.

Скорость передачи оценивается числом передаваемых в секунду битов. Стандартные значения скорости равны 300, 1200, 2400, 4800, 9600, 14400, 19200, 33600, 56000 бит/с.

Микроконтроллер PIC16F873A имеет два модуля последовательной передачи данных: модуль универсального синхронноасинхронного приемо-передатчика (УСАПП, USART – Universal Synchronous Asynchronous Receiver Transmitter) и модуль ведущего синхронного последовательного порта (MSSP – Master Synchronous Serial Port).

3.24. Модуль универсального синхронно-асинхронного приемо-передатчика

Модуль универсального синхронно-асинхронного приемо-пе- редатчика используется преимущественно для организации обмена последовательными данными между микропроцессорными системами. С помощью USART может быть организован информационный обмен микроконтроллера и персонального компьютера. Модуль USART может работать в синхронном или асинхронном режимах. В настоящей работе преимущественно рассматривается работа USART в асинхронном режиме.

В состав модуля USART входят три основных компонента: генератор тактовых импульсов обмена, блок передачи (передатчик) данных и блок приема (приемник) данных. Блок передачи и блок приема работают независимо. Для формирования сигналов син-

84

хронизации используется генератор тактовых импульсов обмена BRG (Baud Rate Generator). Период генерируемых сигналов определяется значением в регистре SPBRG. В асинхронном режиме на скорость обмена влияет также бит BRGH. Если BRGH = 1, модуль работает в высокоскоростном режиме. В табл. 3.1 показана настройка регистра SPBRG и бита BRGH регистра TXSTA в зависимости от требуемой скорости передачи.

|

|

|

|

|

|

Таблица 3.1 |

|

|

Выбор скорости обмена USART в асинхронном режиме |

||||||

|

|

|

|

|

|

||

Fosc = 16 МГц, BRGH = 0 |

Fosc = 16 МГц, BRGH = 1 |

||||||

Скорость |

Ошибка, % |

Значение |

Скорость |

Ошибка, % |

Значение |

||

обмена |

|

|

SPBRG |

обмена |

|

|

SPBRG |

|

|

|

(десятич.) |

|

|

|

(десятич.) |

2400 |

|

0,17 |

103 |

2400 |

- |

|

- |

9600 |

|

0,16 |

25 |

9600 |

0,16 |

|

103 |

19200 |

|

0,16 |

12 |

19200 |

0,16 |

|

51 |

57600 |

|

8,51 |

2 |

57600 |

2,13 |

|

16 |

Реальная скорость передачи в асинхронном высокоскоростном режиме определяется выражением

Vпер = |

Fosc |

, |

(3.1) |

16(X +1) |

где Fosc – тактовая частота микроконтроллера, X – значение, записанное в регистр SPBRG.

Таким образом, значение, которое требуется записать в SPBRG для работы USART на заданной скорости, может быть получено из (3.1).

При асинхронном обмене группа битов (кадр) имеет следующий формат: в отсутствии передачи линия находится под высоким потенциалом, начало передачи отмечается нулевым старт-би- том, за ним следует 8 информационных бит (младшим разрядом вперед), затем идет необязательный бит контроля (бит четности) и заканчивается передача 1; 1,5 или 2 стоп-битами.

Приемник и передатчик работают независимо друг от друга, но используют один и тот же формат данных и одинаковую скорость обмена. Бит четности аппаратно не поддерживается, но мо-

85

жет быть реализован программно, применяя 9-разрядный формат данных. Настойка передатчика выполняется с помощью битов регистра TXSTA, а приемник настраивается битами в регистре RCSTA. Выбор асинхронного режима выполняется сбросом в 0 бита SYNC в регистре TXSTA.

Основой передатчика USART служит сдвиговый регистр TSR, получающий данные из регистра TXREG (рис. 3.16).

Рис. 3.16. Структурная схема передатчика USART

Данные в TXREG загружаются программно, причем сразу после загрузки данных в TXREG бит TXIF автоматически сбросится в 0. Содержимое TXREG переписывается в TSR в последнем машинном такте цикла BRG, при условии, что выполнена передача стопового бита предыдущего символа. После этого устанавливается в 1 флаг TXIF, который не может сбрасываться в 0 программно. Таким образом, бит TXIF показывает занятость или свободность регистра TXREG. Завершение передачи можно определить по состоянию бита TRMT из регистра TXSTA, который управляется аппаратно, аналогично биту TXIF.

Для разрешения работы модуля USART следует установить бит SPEN в 1. Включение передатчика выполняется установкой в 1 бита TXEN. Оба бита находятся в регистре TXSTA.

86

Для работы в режиме 9 разрядной передачи используются биты TX9 и TX9D. Установка первого в 1 разрешает передавать 9 разряд, а второй должен содержать само значение 9 бита.

Настройка передатчика USART и передача символа выполняются следующей программой:

bsf STATUS, RP0 |

;1 |

bcf STATUS, RP1 |

;2 |

bcf TRISC, 6 |

;3 |

bsf TXSTA, BRGH |

;4 |

movlw d’51’ |

;5 |

movwf SPBRG |

;6 |

bcf TXSTA, SYNC |

;7 |

bcf STATUS, RP0 |

;8 |

bcf STATUS, RP1 |

;9 |

bsf RCSTA, SPEN |

;10 |

bsf STATUS, RP0 |

;11 |

bcf STATUS, RP1 |

;12 |

bsf TXSTA, TXEN |

;13 |

bcf STATUS, RP0 |

;14 |

bcf STATUS, RP1 |

;15 |

movlw h’33’ |

;16 |

movwf TXREG |

;17 |

Сначала активируется первый банк данных (строки 1 и 2) для обеспечения возможности доступа к регистрам TRISC, TXSTA и SPBRG. Сбросом бита 6 в регистре TRISC настраивается направление передачи – на вывод данных (строка 3). Настройка скорости передачи 19200 бод/с (табл. 3.1) выполняется установкой бита BRGH в регистре TXSTA и записью числа 51 в регистр SPBRG (строки 5 и 6). Сброс бита SYNC переводит передатчик в асинхронный режим обмена (строка 7). Далее активируется нулевой банк для доступа к регистру RCSTA (строки 8 и 9). Установкой бита SPEN включается модуль USART (строка 10), а установкой бита TXEN включается передатчик (строка 13). После загрузки числа 33 в регистр TXREG (строки 16 и 17) выполняется его передача.

На вход приемника USART данные подаются через ножку RC7 микроконтроллера (рис. 3.17).

87

Рис. 3.17. Структурная схема приемника USART

Через буфер ввода принимаемый сигнал поступает на мажоритарный детектор, который три раза за такт передачи захватывает входной сигнал, чтобы определить присутствие высокого или низкого уровня на входе. Сдвиговый регистр RSR преобразует принимаемый последовательный код в параллельный. После получения стопового бита данные переписываются в регистр RCREG, откуда доступны для считывания. После записи в RCREG выставляется флаг прерывания RCIF. Прерывание возникнет, если установлен в 1 бит RCIE. Флаг RCIF аппаратно сбрасывается при чтении регистра RCREG.

Регистр RCREG имеет двойную буферизацию, т. е. представляет собой двухуровневый буфер FIFO. Если FIFO заполнен и обнаружен стоповый бит третьего байта, устанавливается бит OERR (Overload Error – ошибка переполнения) в регистре RCSTA. Принятый в RSR символ будет потерян. Для извлечения двух символов из FIFO необходимо дважды считать содержимое регистра RCREG, а бит OERR очистить сбросом бита CREN в регистре RCSTA. Если не обнаруживается стоповый бит, будет установлен бит FERR (Frame Error – ошибка кадра).

Девятиразрядный прием включается установкой бита RX9 в 1. Бит 9 сохраняется приемником в бит RX9D регистра RCSTA.

Настройка приемника USART выполняется следующей программой:

88

bcf STATUS, RP0 |

;1 |

bsf STATUS, RP1 |

;2 |

bsf TRISC, 7 |

;3 |

bsf TXSTA, BRGH |

;4 |

movlw d’51’ |

;5 |

movwf SPBRG |

;6 |

bcf TXSTA, SYNC |

;7 |

bcf STATUS, RP0 |

;8 |

bcf STATUS, RP1 |

;9 |

bsf RCSTA, SPEN |

;10 |

bsf RCSTA, CREN |

;11 |

Для доступа к регистрам TRISC, TXSTA и SPBRG активируется первый банк данных (строки 1 и 2). Выполняется настройка направления передачи на ввод данных (строка 3). Устанавливается значение скорости передачи в 19200 бод/с (строки 4 – 6). Выбор асинхронного режима обмена (строка 7). Для доступа к битам регистра RCSTA активируется нулевой банк памяти данных (строки 8 и 9). Бит SPEN включает модуль USART (строка 10), бит CREN включает приемник (строка 11).

3.25.Модуль ведущего синхронного последовательного порта

Модуль MSSP может работать в одном из двух режимов:

–последовательный интерфейс для связи интегральных микросхем (I2C, Inter-Integrated Circuit);

–последовательный периферийный интерфейс (SPI, Serial Peripheral Interface).

Стандарт I2C реализован как двухпроводный последовательный интерфейс, разработанный компанией «Philips Corp.». К одной шине I 2C могут подключаться устройства с различными скоростями доступа. При обмене данными одно устройство является ведущим и формирует сигналы синхронизации. Другое устройство – ведомое, может начать передачу данных только по команде от ведущего. Протокол I 2C использует две сигнальные линии, по одной из которых передается сигнал синхронизации, а по другой передаются или принимаются данные.

Интерфейс SPI связывает два устройства, одно из которых является ведущим, а другое – ведомым. К ведущему устройству мо-

89

жет быть подключено несколько ведомых, в этом случае ведущий должен выбирать ведомого, подавая сигнал выбора. Таким образом, интерфейс SPI использует до 4 сигнальных линий:

–сигнал, передаваемый по линии SCK, представляет собой последовательность синхронизирующих импульсов, генерируемых ведущим;

–по линии SDO (Serial Data Out) выполняется передача данных от ведущего к ведомому;

–по линии SDI (Serial Data In) данные передаются от ведомого к ведущему;

–по линии SS (Slave Select) передается сигнал выбора конкретного ведомого устройства.

Рассмотрим работу модуля MSSP в режиме последовательного периферийного интерфейса SPI (рис. 3.18).

Основой модуля MSSP является регистр сдвига SSPSR (SSP Shift Register), который используется как для приема, так и для передачи данных. Тактовый сигнал для сдвига SSPSR, формируемый ведущим устройством, представляет собой тактовый сигнал микроконтроллера с уменьшенной в 4, 16 или 64 раза частотой, либо сигнал

свыхода TMR2 с уменьшенной в два раза частотой.

Для передачи данных выполняется запись в регистр SSPBUF, из которого данные автоматически перегружаются в SSPSR и побитно выдаются на вывод RC5 (SDO) микроконтроллера. Одновременно с этим данные побитно считываются с вывода RC4 (SDI). Считанные 8 бит данные переписываются в SSPBUF, откуда доступы программно. Сразу после того как данные переписываются в SSPBUF, устанавливается в 1 флаг BF (Buffer Full) регистра SSPSTAT. После чтения данных из SSPBUF флаг BF автоматически сбрасывается в 0.

Вывод RA5 (SS) используется для разрешения передачи ведомому устройству, в случае когда к одному ведущему подключено несколько ведомых. Через вывод RC3 (SCK) передается тактовая частота от ведущего к ведомому. Любой неиспользуемый вывод модуля MSSP можно выключить. Например, если в режиме ведущего выполняется только передача данных, то выводы RC4 (SDI) и RA5 (SS) могут использоваться как цифровые выводы. Для этого следует сбросить соответствующие биты направления передачи (TRISС4 и TRISA5).

90