- •Введение.

- •Цели и задачи дисциплины.

- •Связь с другими дисциплинами и необходимый уровень подготовки.

- •Кодирование логической и двоичной информации электрическими сигналами.

- •Характеристики электрических сигналов.

- •Простейшие логические операции и их схемотехническая реализация (диодные схемы).

- •Ттл элемент, работа схемы, основные характеристики.

- •Разновидности логических элементов и серии интегральных микросхем.

- •Соединения логических элементов и радиокомпонентов.

- •Схемотехника функциональных устройств.

- •Схемотехника последовательностных устройств.

- •Триггеры.

- •Счётчики.

- •Двоичные счетчики.

- •Недвоичные счетчики.

- •Регистры.

- •Параллельные регистры.

- •Последовательные (сдвиговые) регистры.

- •Комбинационные устройства.

- •Дешифраторы.

- •Линейный дешифратор.

- •Матричный дешифратор.

- •Пирамидальный дешифратор.

- •Дешифраторы интегрального исполнения.

- •Мультиплексор и демультиплексор.

- •Мультиплексоры интегрального исполнения.

- •Сумматоры.

- •Одноразрядные комбинационные сумматоры.

- •Многоразрядные сумматоры.

- •Последовательный многоразрядный сумматор.

- •Параллельный многоразрядный сумматор.

- •Ускоренный перенос.

- •Арифметико-логическое устройство.

- •Устройства памяти.

- •Статические элементы оперативных запоминающих устройств.

- •Запоминающий элемент на биполярных транзисторах.

- •Запоминающий элемент на полевых транзисторах.

- •Динамический запоминающий элемент оперативных запоминающих устройств.

- •Запоминающие элементы пзу.

- •Организация бис зу.

- •Построение запоминающих устройств эвм.

- •Программируемые логические матрицы.

- •Формирователи.

- •Определение интервала времени по заданным уровням сигналов в цепях первого порядка.

- •Формирователи периодических сигналов.

- •Несимметричный мультивибратор на логических элементах.

- •Формирователь фронтов (спадов) — триггер Шмитта.

- •Формирователи импульсов.

- •Формирователь на интегрирующей rc цепи.

- •Одновибратор с дифференцирующей rc цепью.

- •Одновибраторы интегрального исполнения.

- •Интерфейсные устройства.

- •Буферные устройства.

- •Передача сигналов по линиям связи.

- •Несимметричные линии связи.

- •Согласование линий связи.

- •Симметричные линии связи.

- •Цифро-аналоговые и аналого-цифровые преобразователи.

- •Цифро-аналоговые преобразователи (цап).

- •Цифро-аналоговый преобразователь на суммировании токов.

- •Цифро-аналоговый преобразователь на матрице r-2r.

- •Аналого-цифровые преобразователи (ацп).

- •Параллельный ацп.

- •Ацп последовательного приближения (последовательные ацп).

- •Ацп двойного интегрирования.

- •Системы индикации.

- •Индикация состояния логического элемента.

- •Индикация состояния шин.

-

Последовательный многоразрядный сумматор.

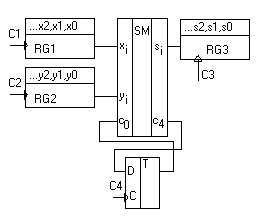

Рис.69. Последовательный сумматор.

Последовательный сумматор предусматривает использование одного сумматора ОС-3 не зависимо от количества разрядов слагаемых. Структурная схема многоразрядного последовательного сумматора приведена на рис. 69. Схема состоит из двух сдвиговых регистров RG1 и RG2, предназначенных для хранения и сдвига операндов, последовательного регистра RG3 для записи и хранения суммы, одноразрядного сумматора ОС-3, устройства задержки переноса, и качестве которого лучше всего применить триггер. При выполнении разрядного суммирования сформированный перенос будет записываться в этот триггер, а использован перенос будет при выполнении суммирования в следующем старшем разряде.

Обычно регистры RG1 и RG2 -- сдвиговые

регистры с параллельным занесением,

RG3 -- сдвиговый регистр с параллельным

чтением. При поступлении младших разрядов

операндов x0,y0 на входы сумматора

начинается формирование суммы и переноса,

которое заканчивается по истечении

времени

![]() .

После этого можно подавать управляющие

сигналы С3 и С4 для записи разрядной

суммы в регистр суммы RG3 и переноса в

триггер задержки, который будет хранить

перенос до прихода следующего разряда

операндов. По истечении времени

необходимого для записи в регистр можно

подавать сигналы С1 и С2 для сдвига

операндов, т.е. для подачи на входы

сумматора следующего разряда операндов.

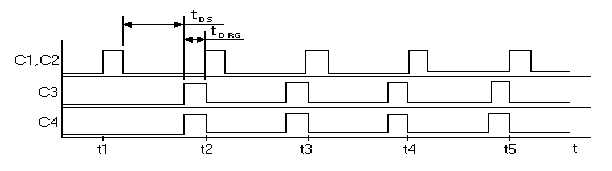

Работа последовательного сумматора

иллюстрируется временной диаграммой,

приведенной на рисунке 70. На временной

диаграмме показаны соотношения во

времени подачи управляющих сигналов

С1, С2, С3, С4, а также интервалы времени

необходимые на: выполнение операции в

одноразрядном сумматоре --

.

После этого можно подавать управляющие

сигналы С3 и С4 для записи разрядной

суммы в регистр суммы RG3 и переноса в

триггер задержки, который будет хранить

перенос до прихода следующего разряда

операндов. По истечении времени

необходимого для записи в регистр можно

подавать сигналы С1 и С2 для сдвига

операндов, т.е. для подачи на входы

сумматора следующего разряда операндов.

Работа последовательного сумматора

иллюстрируется временной диаграммой,

приведенной на рисунке 70. На временной

диаграмме показаны соотношения во

времени подачи управляющих сигналов

С1, С2, С3, С4, а также интервалы времени

необходимые на: выполнение операции в

одноразрядном сумматоре --

![]() ,

запись информации в регистр --

,

запись информации в регистр --

![]() .

.

Рис. 70. Временная диаграмма работы последовательного сумматора.

На интервале t1-t2 выполняется суммирование

нулевых разрядов операндов, t2-t3 -- первых

разрядов, t3-t4 -- вторых разрядов, t4-t5 --

третьих разрядов операндов. Таким

образом, быстродействие последовательного

сумматора определяется временными

параметрами выбранных микросхем (![]() )

и количеством разрядов операндов.

Поэтому быстродействие последовательного

многоразрядного сумматора мало и он не

находит применения в современной

вычислительной технике.

)

и количеством разрядов операндов.

Поэтому быстродействие последовательного

многоразрядного сумматора мало и он не

находит применения в современной

вычислительной технике.

-

Параллельный многоразрядный сумматор.

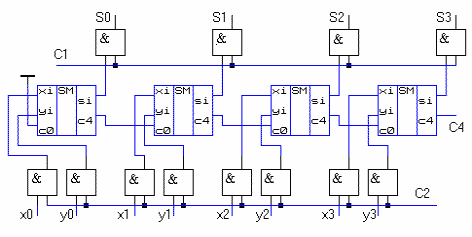

Для повышения быстродействия при выполнении операций суммирования широко применяют параллельный сумматор. Отличительной особенностью такого сумматора является количество используемых схем ОС-3, которое равно количеству разрядов операндов с учетом знака и анализа переполнения.

На рис. 71 изображена структурная схема параллельного четырёхразрядного сумматора. Схема состоит из четырех схем ОС-3 и двенадцати элементов 2И, используемых в качестве ключей. Ключи подачи операндов на входы сумматора управляются сигналом С2 (активный высоким уровнем), а ключи выдачи результата -- С1. Как только С2=1 на входы сумматора подаются операнды, и начинается процесс суммирования. Все разряды слагаемых одновременно поступают на входы сумматоров и одновременно во всех разрядах начинается формирование суммы и переноса.

Перенос последовательно подсуммируется к разрядам результата, т.е. получаем, что разрядные суммы формируются одновременно, а перенос осуществляется последовательно. Время, затрачиваемое на получение суммы многоразрядных операндов, определяется соотношением

![]() ,

,

где:

![]() --

среднее время задержки сигнала,

--

среднее время задержки сигнала,

![]() --

время формирования сигнала переноса

схемой ОС-3, n -- количество разрядов

операндов.

--

время формирования сигнала переноса

схемой ОС-3, n -- количество разрядов

операндов.

Рис.71. Параллельный сумматор.

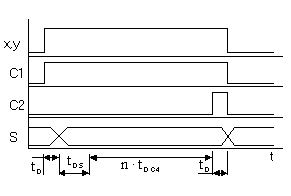

Рассмотренные особенности работы параллельного сумматора отображены на временной диаграмме рис. 72. Принятые обозначения: x,y -- шина входных операндов, s -- шина суммы, С1,С2 -- управляющие сигналы, С4 -- перенос в следующий старший разряд.

Операнды должны быть установлены до начала суммирования и они не должны менять своего значения до получения суммы. От момента подачи сигнала С1 плюс один интервал задержки начинается формирование суммы и переносов.

Рис. 72. Временная диаграмма работы параллельного сумматора.

На формирование поразрядной суммы

затрачивается время

![]() .

В самом плохой ситуации, когда перенос

возникает в младшем разряде и проходит

до старшего разряда, на формирование

переноса С4 затрачивается время

.

В самом плохой ситуации, когда перенос

возникает в младшем разряде и проходит

до старшего разряда, на формирование

переноса С4 затрачивается время

![]() .

.

После формирования окончательной суммы, с учетом всех переносов, можно подавать сигнал С2 -- выдачи результата на шину суммы. Как видно из временной диаграммы значительная часть времени работы сумматора затрачивается на формирование переносов.

Лекция 24.