- •Архитектура и режимы работы микропроцессора к1810вм86

- •Выбор основных узлов для построения мпс

- •3.1 Буферные регистры и шинные формирователи

- •3.2 Программируемый таймер к1810ви54

- •3.3 Разработка блока ацп

- •3.4 Разработка контроллера прямого доступа к памяти

- •3.5 Организация прерываний в мп к1810вм86

- •3.6 Разработка подсистемы ввода/вывода

- •3.7 Генератор тактовых импульсов

- •3.8 Разработка принципиальной схемы микро-эвм

- •5. Буферные регистры и шинные формирователи

3.1 Буферные регистры и шинные формирователи

При разработке функциональной схемы модуля центрального процессора возникает потребность в демультиплексировании шины адреса/данных, буферизации адреса и шин данных. Демультиплексирование осуществляется с помощью двух БИС К580ИР82, которые выполняют функции защелки адреса и буфера шины адреса. Буферизация шин данных создается с помощью двунаправленных шинных формирователей К580ВА86, усиливающих сигналы шины данных.

Буферные регистры К580ИР82 состоят из восьми информационных триггеров (Т) с выходными схемами (SW) с тремя состояниями, общими сигналами записи информации STB и управления выходными схемами ОЕ. К выходным схемам буферных регистров подключены прямые выходы информационных триггеров.

Рисунок 11 – Функциональная схема К580ИР82

Рисунок 12 – Условно-графическое обозначение К580ИР82

D17-D10 – линии входных данных;

D07-D00 – линии выходных данных;

STB – стробирующий сигнал;

![]() –

разрешение выдачи данных.

–

разрешение выдачи данных.

При сигнале высокого уровня

на входе STB

состояние входных линий D17-D10

передается на выходные линии D07-D00.

Запоминание (защелкивание) в

информационных триггерах осуществляется

при переходе сигнала STB

от высокого уровня к низкому (по срезу

сигнала STB).

Сигнал

![]() управляет выходными буферами: при

управляет выходными буферами: при

![]() =0

буфер отпирается, при

=0

буфер отпирается, при

![]() =1

он устанавливается в

z-состояние.

Сигнал

=1

он устанавливается в

z-состояние.

Сигнал

![]() не влияет ни на состояния информационных

триггеров, ни на функцию записи.

не влияет ни на состояния информационных

триггеров, ни на функцию записи.

Восьмиразрядные шинные формирователи КР580ВА86 применяют как буферные устройства шины данных в микропроцессорных системах. Большая выходная мощность и простота управления позволяют использовать их для построения двунаправленных согласующих буферов межмодульной связи либо как простые усилительные каскады. Полная конструктивная совместимость с БР ИР82/83 допускает взаимозаменяемость при однонаправленной передаче.

Формирователь состоит из

восьми одинаковых функциональных блоков

с общими сигналами управления

Т и ОЕ. Функциональные блоки состоят из

двух усилителей-формирователей с

z-состояниями

на выходах, схема  включения

ко

включения

ко торых

обеспечивает разнонаправленную передачу.

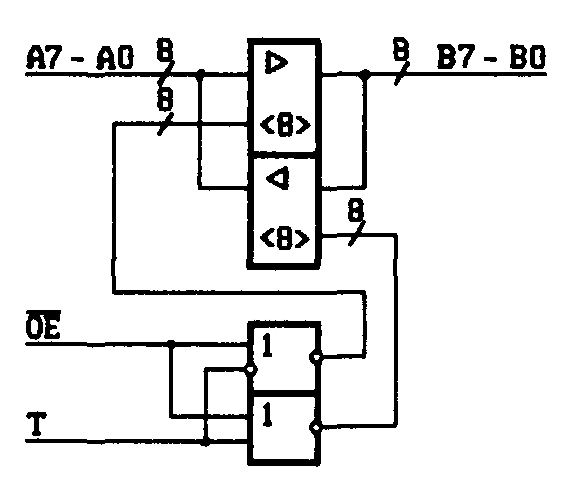

Формирователь ВА86 (рисунок 13, 14) не

инвертирует данные.

торых

обеспечивает разнонаправленную передачу.

Формирователь ВА86 (рисунок 13, 14) не

инвертирует данные.

Рисунок 13 – Функциональная схема К580ВА86

Рисунок 14 – Условно-графическое обозначение К580ВА86

А7-А0 – вход/выход линий данных. В зависимости от состояния входа Т они могут быть входными, если на Т – сигнал высокого уровня, и выходными, если на Т – сигнал низкого уровня.

В7-В0 – вход/выход линий данных. Они являются входными, если на Т – сигнал низкого уровня, и выходными, если на Т – сигнал высокого уровня.

Т – входной сигнал управления направлением передачи. При Т=0 осуществляется передача от В к А (режим В→А), при Т=1 – от А к В. Сигнал Т выбирает верхний или нижний усилитель-формирователь, разрешая соответствующую передачу.

Основные

достоинства шинных формирователей:

большой выходной ток при малом входном

токе и отсутствие шума на выходе при

переключениях.

Основные

достоинства шинных формирователей:

большой выходной ток при малом входном

токе и отсутствие шума на выходе при

переключениях.

3.2 Программируемый таймер к1810ви54

Программируемый таймер (ПТ) К1810ВИ54 предназначен для генерации времязадающих функций, программно-управляемых временных задержек с возможностью программного контроля их выполнения. Программируемые таймеры применяются в МПС, выполненных на базе МПК БИС К580, К1810, К1821, используемых в задачах управления и измерения в реальном масштабе времени с тактовой частотой до 8 МГц. Конструктивно эти ПТ совместимы с ПТ типа К580ВИ53, отличаются от них повышенным быстродействием и расширенными функциональными возможностями.

Рисунок 15 – Структура схема ПТ К1810ВИ54

Программируемый таймер К1810ВИ54 включает три независимых канала, каждый из которых может быть запрограммирован на работу в одном из шести режимов для двоичного или двоично-десятичного счета. Структурная схема ПТ показана на рисунке 15, его условное графическое обозначение – на рисунке 16.

Рисунок

16 – Условно-графическое обозначение

ПТ К1810ВИ54

Рисунок

16 – Условно-графическое обозначение

ПТ К1810ВИ54

Таблица 4 – Назначение выводов ПТ К1810ВИ54

|

Обозначение вывода |

Назначение |

|

|

Сигнал управляет входным буфером BD.

При

|

|

|

Сигнал

|

|

|

Сигнал

|

|

А0, А1 – адресные входы |

По ним осуществляется адресация к одному из каналов: А0=А1=00 – адрес канала 0; А0=А1=01 – адрес канала 1; А0=А1=10 – адрес канала 2; А0=А1=11 – признак загрузки управляющего слова или команд. |

|

CLK2–CLK0 – входы тактовых сигналов для управления счетчиком/таймером |

Срез сигнала на входе CLK приводит к уменьшению содержимого счетчика/таймера СЕ на единицу. |

|

GATA2–GATA0 – входы разрешения счета. |

При GATA=l разрешается выполнение функций; для некоторых режимов работы разрешается поступление тактовых сигналов на вход счетчика/таймера, для других (импульсный генератор и генератор меандра) открывается выходной буфер OUT. |

|

OUT2–OUT0 – выходы счетчика/таймера. |

|