- •Двоичный полусумматор. Представляет собой объединение двух бинарных (двухоперандных) двоичных логических функций: сумма по модулю два - s и разряд переноса при двоичном сложении - c.

- •В данной схеме бит переноса из старшего разряда сумматора становится старшим разрядом суммы.

- •23. Организация персонального компьютера и назначение основных функциональных блоков.

- •Структурная схема персонального компьютера

- •24. Факторы повышения производительности персонального компьютера. Быстродействие, производительность, тактовая частота. Единицами измерения быстродействия служат:

- •Видеоадаптеры условно делятся на шесть логических блоков:

- •41.Параметры разрешения монитора и видеоадаптера пк. Видеоконтроллер должен обеспечить естественное

- •Основные параметры видеокарты:

1.Системы счисления - способ представления чисел с помощью определенного набора (алфавита) символов, называемых цифрами и имеющих определенное количественное значение. Число цифр называется основанием системы счисления и определяет её название.

(256)10=2*102+5*101+6*100

102 , 101 , 100 – коэффициенты – определяют вес этого числа;

Номер позиции справа налево называют разрядом (нулевой (единиц), первый (десятков), )

Двоичная с.с.:

(1101,101)2=1*23+1*22+0*21+1*20+1*2-1+0*2-2+1*2-3;

Восьмеричная с.с.:

(71,6)8=7*81+1*80 + 6*8-1=(57,75)10;

Перевод целых чисел из 10 в 2 (8,16):надо последовательно делить на 2 (8,16);

Перевод дробных чисел из 10 в 2 (8,16): используется метод последовательного умножения на 2 (8,16), записывается ответ в виде целых частей чисел, полученных при умножении, начиная слева после запятой ( снизу вверх)

2. Числа с фиксированной запятой. Первые ЭВМ были машинами с фиксированной запятой, причем запятая фиксировалась перед старшим разрядом. В настоящее время, форму ЧФЗ, как правило, применяют для представления целых чисел (запятая фиксируется после младшего разряда). По сложившейся традиции, нумерация разрядов в разрядной сетке машин общего назначения (ЕС-ЭВМ) ведется слева направо, а в малых ЭВМ, микро-ЭВМ и микропроцессорах - справа налево. Поскольку фиксация точки слева от СЗР в настоящее время практически не используется, рассмотрим только формат представления целых чисел (рис. 2.7.)

Следует иметь ввиду, что в ЕС-ЭВМ целые числа могут быть представлены как в формате слова (32 разряда), так и в формате полуслова (16 разрядов). Используют два варианта представления целых чисел - со знаком и без знака. В последнем случае все разряды служат для представления модуля числа. В ЕС-ЭВМ реализуются оба этих варианта в формате слова и полуслова. В мини- и микро-ЭВМ разрядность слова меньше (СМ-4, Электроника-60, СМ-1300 слова длиной 16 бит), но формат представления целых чисел аналогичен рассмотренному (рис. 2.8.), за исключением того, что нумерация разрядов осуществляется в другую сторону.

Следует иметь ввиду, что в мини- и микро-ЭВМ целые числа могут быть представлены как в формате слова (16 или 8 бит), так и в формате двойного слова (32 или 16 бит). В микро-ЭВМ целые числа часто представляют без знака в формате слова (8 бит) или двойного слова. В современных ЭВМ, как правило, слова содержат целое число байт, кратное степени двойки (1,2,4 . . . байта). Рассмотрим диапазон представления чисел с фиксированной запятой (только целых чисел, т.е. точка фиксирована справа от МЗР). Если в разрядной сетке N разрядов, то под модуль числа отводится N-1 разряд (число со знаком). Самое большое по модулю число, записанное в такой сетке, имеет вид:

Следовательно, |X|max = 2N-1 -1 или 0 |X| 2N-1 - 1.

При записи отрицательных чисел в дополнительном коде наибольшее по модулю отрицательное число - это -2N-1. Но модуль этого числа при такой же разрядной сетке (N бит) получить уже нельзя. Поэтому диапазон представления десятичных чисел N-разрядным двоичным числом определяется следующим выражением: -2N-1X 2N-1-1

N |

8 |

16 |

32 |

Xmax |

127 |

32767 |

109 |

Xmin |

-128 |

-32768 |

-109 |

При решении расчетных задач на ЭВМ с фиксированной точкой, для предотвращения переполнения разрядной сетки при подготовке задач к решению на ЭВМ приходится вводить масштабные коэффициенты, которые не позволяют числам, участвующим в решении, и результатам превышать по модулю максимальное машинное число. В настоящее время представление чисел с фиксированной запятой используется как основное и единственное лишь в сравнительно небольших по своим вычислительным возможностям машинах. Подобные ЭВМ применяют в системах передачи данных, для управления технологическими процессами, для обработки измерительной информации в реальном масштабе времени, для построения кодирующих и декодирующих устройств в каналах связи. В ЭВМ общего назначения основным является представление чисел с плавающей запятой.

3. Числа с плавающей запятой. Представление чисел в виде ЧПЗ позволяет избавиться от операции масштабирования при вычислениях, поскольку диапазон представляемых чисел существенно расширяется по сравнению с ЧФЗ. Однако, в большинстве ЭВМ общего назначения, для целых чисел сохраняется возможность представления в виде ЧФЗ. Операции с ЧФЗ всегда выполняются за меньшее время, чем операции с ЧПЗ. В частности, к операциям с целыми числами сводятся операции над кодами адресов (операции индексной арифметики).

Представление чисел с плавающей запятой в общем случае имеет вид:

X = SP*q; |q|<1,

где q - мантисса (правильная дробь со знаком),

p - порядок (целое число со знаком),

S - основание,

SP - характеристика.

В ЭВМ q и p представлены в системе счисления с основанием S в соответствующей двоичной кодировке. Знак числа совпадает со знаком мантиссы. Порядок может быть как положительным так и отрицательным и определяет положение точки в числе X. Арифметические действия над ЧПЗ требуют, помимо действий с мантиссами, определенные операции над порядками (сравнение, вычитание и др.). Для упрощения операций над p их сводят к действиям над целыми положительными числами, применяя представление ЧПЗ со смещенным порядком.

В этом случае к порядку p прибавляют целое число R=2k, где k - число двоичных разрядов, используемых для представления модуля порядка. Смещенный порядок PСМ=P+R всегда больше или равен нулю. Для его представления требуется такое же количество двоичных разрядов, как и для представления знака и модуля p.

При фиксированном числе разрядов мантиссы любая величина представляется в ЭВМ нормализованным числом с наибольшей возможной точностью. Число называется нормализованным, если мантисса q удовлетворяет условию: 1>|q|1/S, т.е. старший разряд мантиссы в S-ричной системе счисления отличен от нуля, иначе число ненормализованно. Так, например, в десятичной системе счисления число 0.00726*10-3 - ненормализовано, а число 0.726*10-5 - нормализовано.

В процессе вычислений числа могут оказаться ненормализованными. Обычно ЭВМ автоматически нормализует такие числа, выполняя ряд действий. На рис. 2.9. представлен обобщенный формат представления ЧПЗ в микро- и мини - ЭВМ.

Рис. 2.9. Формат представления ЧПЗ в мини- и микро-ЭВМ

Пусть r старших разрядов S - ричной мантиссы равны нулю. Тогда нормализация состоит из:

- сдвиг мантиссы на r разрядов влево;

- уменьшение PСМ на r единиц;

- в r младших разрядов мантиссы записываются 0.

При этом число не изменяется, а условия нормализации выполняются.

4.

Двоичная арифметика, арифметические

операции над числами в ЭВМ с плавающей

запятой.

Требуется

вычислить Z=XY,

при условии, что |X||Y|.

Формальное выражение для выполнения

этой операции можно записать следующим

образом:

Алгоритм

выполнения операции состоит в следующем:1.

Производится выравнивание порядков.

Порядок меньшего по модулю числа

принимается равным порядку большего,

а мантисса меньшего числа сдвигается

вправо на число S-ричных разрядов, равное

разности (Px-Py),

т.е. происходит денормализация.2.

Производится сложение (вычитание)

мантисс, в результате чего получается

мантисса суммы (разности).3. Порядок

результата равен порядку большего

числа.4. Полученный результат

нормализуется.

Требуется вычислить

Алгоритм

выполнения операции состоит в следующем:1.

Производится выравнивание порядков.

Порядок меньшего по модулю числа

принимается равным порядку большего,

а мантисса меньшего числа сдвигается

вправо на число S-ричных разрядов, равное

разности (Px-Py),

т.е. происходит денормализация.2.

Производится сложение (вычитание)

мантисс, в результате чего получается

мантисса суммы (разности).3. Порядок

результата равен порядку большего

числа.4. Полученный результат

нормализуется.

Требуется вычислить

.

Формальное выражение для выполнения

этой операции можно записать следующим

образом:

.

Формальное выражение для выполнения

этой операции можно записать следующим

образом:

Z=X*Y=qxSPx*qySPy= qxqyS(Px+Py)=qzSPz Алгоритм выполнения операции состоит в следующем:1. Мантиссы сомножителей перемножаются;2. Порядки сомножителей складываются;3. Произведение нормализуется;4. Произведению присваивается знак, в соответствии с алгоритмом, приведенным для ЧФЗ, а именно:

В данном случае имеется в виду способ умножения, предполагающий отделение от сомножителей их знаковых разрядов и раздельное выполнение действий над знаками и модулями чисел. Однако на практике в современных ЭВМ используют алгоритмы, не требующие раздельных операций над знаками и модулями, например алгоритм Бута. Рассмотрим простейший раздельный алгоритм перемножения ЧПЗ. Умножение ЧПЗ сводится к следующим операциям:- алгебраическое суммирование порядков - это операции над целыми числами или ЧФЗ с фиксацией точки справа от МЗР;- перемножение мантисс - это операции над правильными дробями или над ЧФЗ с фиксацией точки слева от СЗР;- определение знака произведения. Операции над целыми числами были рассмотрены ранее. Теперь рассмотрим только перемножение правильных дробей. Вручную дроби можно перемножать столбиком. Подсчет знаков в дробной части такой же, как и при перемножении десятичных дробей. В ЭВМ для перемножения мантисс (как и для целых чисел), возможны два варианта перемножения: "старшими разрядами вперед" и "младшими разрядами вперед". Если требуется сохранить все разряды, то в устройстве, формирующем произведение, число разрядов должно равняться сумме числа разрядов множителя и множимого. Однако часто в произведении требуется сохранить то же количество разрядов, что и в множимом. Это приводит к потере младших разрядов. Рассмотрим пример перемножения двух чисел "младшими разрядами вперед" для случая, когда разрядная сетка результата соответствует разрядной сетке сомножителей.

5.

Кодирование двоичных чисел в ЭВМ с

учетом знака. Прямой код

Это

обычный двоичный код, рассмотренный в

разделе двоичной системы счисления.

Если двоичное число является положительным,

то бит знака равен 0, если двоичное число

- отрицательное, то бит знака равен 1.

Цифровые разряды прямого кода содержат

модуль представляемого числа, что

обеспечивает наглядность представления

чисел в прямом коде (ПК).

Сложение в прямом коде чисел, имеющих одинаковые знаки, достаточно просто: числа складываются, и сумме присваивается знак слагаемых. Значительно более сложным является алгебраическое сложение в прямом коде чисел с разными знаками. В этом случае приходится определять большее по модулю число, производить вычитание модулей и присваивать разности знак большего по модулю числа. Такую операцию значительно проще выполнять, используя обратный и дополнительный коды. Обратный код В обратном коде (ОК), также как и в прямом коде, для обозначения знака положительного числа используется бит, равный нулю, и знака отрицательного - единице. Обратный код отрицательного двоичного числа формируется дополнением модуля исходного числа нулями до самого старшего разряда модуля, а затем поразрядной заменой всех нулей числа на единицу и всех единиц на нули. В знаковом разряде обратного кода у положительных чисел будет 0, а у отрицательных - 1.

В общем случае ОК является дополнением модуля исходного числа до наибольшего числа без знака, помещенного в разрядную сетку. Алгоритм формирования ОК очень прост, при этом ОК позволяет унифицировать операции сложения и вычитания в АЛУ, которые в прямом коде выполняются по-разному. Однако работа с ОК вызывает ряд трудностей. В частности, возникают два нуля: +0 и -0, т.е. в прямом коде (в котором представлены положительные числа) имеет место (+0) = 000...0, а в обратном коде (в котором представлены отрицательные числа): (-0) = 111...1. Кроме того, в операциях сложения и вычитания требуется дополнительная операция по прибавлению бита переноса в младший разряд суммы. Рассмотрим правила алгебраического сложения в ОК (поскольку А-В=А+(-В)). Алгоритм сложения в ОК включает в себя: сложение кодов, включая знаковый разряд;прибавление переноса к МЗР (младшему значащему разряду) суммы. Указанные трудности привели к тому, что в современных ЭВМ абсолютное большинство операций выполняется в дополнительном коде. Дополнительный код Дополнительный код (ДК) строится следующим образом. Сначала формируется обратный код (ОК), а затем к младшему разряду (МЗР) добавляют 1. При выполнении арифметических операций положительные числа представляются в прямом коде (ПК), а отрицательные числа - в ДК, причем обратный перевод ДК в ПК осуществляется аналогичными операциями в той же последовательности.

Использование ДК для представления отрицательных чисел устраняет двусмысленное представление нулевого результата (возникновение двух нулей: +0 и -0), так как -0 исчезает. В общем случае использованием ДК для записи отрицательных чисел можно перекрыть диапазон десятичных чисел от –2k-1 до +2k-1-1, где k - число используемых двоичных разрядов, включая знаковый. Так, с помощью одного байта можно представить десятичные числа от -128 до +127, либо только положительные числа от 0 до 255 (здесь под положительными числами понимаются числа без знака). В табл.1 приведены 4-разрядные двоичные числа от 0000 до 1111 и десятичные числа в случае представления их со знаком и без знака. Из этой таблицы следует, что в формате 4-разрядного двоичного числа могут быть представлены десятичные числа со знаком в диапазоне от -8 до +7 или десятичные числа без знака в диапазоне от 0 до +15. Оба этих способа представления чисел (со знаком и без знака) широко используются в ЭВМ.

6. Представление информации в ЭВМ физическими сигналами. Нули и единицы нужно кодировать, т.е. представлять физическими сигналами. Сигнала должна быть хорошо различны: 1) Напряжения высокого и низкого уровней; 2) Наличие или отсутствие электрического импульса; 3) противоположные по знаку значение магнитной индукции

1 способ- потенциальный способ представления информации

2 – импульсный способ.

Передача многоразрядной двоичной информации – существует 3 способа; последовательный (регистр хранит информацию о многоразрядном числе); параллельный (для передачи п-разрядного числа, все разряды передаются по п-шинам одновременно); смешанный.

7.Логические элементы ЭВМ. Схемы, реализующие логические функции, называются логическими элементами. Основные логические элементы имеют, как правило, один выход (Y) и несколько входов, число которых равно числу аргументов(X1, X2,…Xn)

Основными алгебраическими функциями являются:

НЕ - реализует логическую операцию отрицания (инверсия) Y=X

X1 |

X2 |

Y |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

![]()

X1 |

X2 |

Y |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

Y=X1*X2 или Y= X1 X2

![]()

X1 |

X2 |

Y |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

![]()

X1 |

X2 |

Y |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

![]()

X1 |

X2 |

Y |

0 |

0 |

01 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

![]()

X1 |

X2 |

Y |

0 |

0 |

11 |

1 |

0 |

01 |

0 |

1 |

01 |

1 |

1 |

10 |

Исключающее и - реализует ф-цию равнозначности.

8.Комбинационная схема. Нахождение для схемы булевой функции.Комбинационная схема – схема, выполняющая соответствующие функции алгебры логики, представление информации. Результат преобразований входных переменных зависит только от комбинации входных логических переменных, которые присутствуют в данный момент времени. Функцию алгебры логики любой сложности можно реализовать с помощью логических элементов; НЕ, ИЛИ, И (основной базис).

Примеры комбинационных схем узлов ЭВМ: дешифратор – узел, предназначенный для распознавания кодовых комбинаций, кодов команд, кодов адресов ячеек; мультиплексор – узел, предназначенный для передачи информации с нескольких устройств в одну выходную цепь.

Правила нахождения аналитического вида логической функции используют правила перехода от табличного задания к аналитическому. Это правило основано на образовании и получении СДНФ (совершенной дизъюнктивной нормальной формы). Это логическое выражение, в которое входят наборы элементарных конъюнкций одинакового ранга, связанных дизъюнкцией. Ранг – это число аргументов (переменных), составляющих элементарную конъюнкцию.

Х |

У |

0 |

1 |

1 |

0 |

2) По каждому набору двоичных переменных, при котором функция принимает значение 1, составляют элементарные конъюнкции (минтермы)

3) В элемент строки конъюнкции записывают неинвертированными переменные, заданные 1 в таблице истинности, а переменные заданные 0 - инвертированными.

4) Элементарные конъюнкции (минтермы), соединяются знаком дизъюнкции (или).

Законы булевой алгебры:

- распределительный закон

X1(Х2+Х3)=X1*Х2+X1*Х3

X1+X2*Х3=(X1+X2)(X1+Х3);

- правило повторения

Х*Х=Х, Х+Х=Х;

- правило отрицания

Х*Х’=0, Х+Х’=1;

-теорема де Моргана

(X1+X2)’=X1’*X2’,

(X1*Х3)’=X1’+Х2’;

- тождества

Х*1=Х, Х+0=Х,

Х*0=0, Х+1=1.

9. Асинхронный RS-триггер и его применение. Триггер – типовое устройство ЭВМ, которое позволяет хранить единицу двоичной информации(0,1).

Простейшим триггером является асинхронный RS -триггер, вариант схемы которого изображен на рис.1.2.

На рис.2.2 представлено условное изображение RS- триггера.

Этот триггер устанавливается в состоянии 1 (Q=1) информационными сигналами S=1; R=0 и в состоянии О (Q=0) сигналами S=0, R=1. Комбинация сигналов R=S=1 является запрещенной, т.к. состояние триггера не определено. Триггер является асинхронным, т.к. переход из одного состояния в другое происходит в темпе поступления входных информационных сигналов R, S. Таблица 1 отражает процесс перехода триггера из одного устойчивого состояния в другое. В ней содержатся значения текущих информационных сигналов Rt, St, Qt, а так же значение последующего выходного сигнала Qt+1 после момента прихода информационных сигналов R и S.

St |

Rt |

Qt. |

Qt+1. |

0 |

1 |

о |

о |

0 |

1 |

1 |

о |

1 |

0 |

о |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

о |

о |

0 |

0 |

1 |

1 |

1 |

1 |

|

не определено |

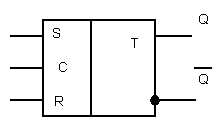

10. Синхронный RS- триггер и его применение. В отличие от асинхронного этот триггер на каждом информационном входе имеет дополнительные схемы совпадения, первые входы которых объединены и на них подаются синхронизирующие сигналы (рис. 3.2). Вторые входы схем совпадения являются информационными.

Наличие

схем совпадения приводит к тому, что

триггер будет срабатывать от сигналов

R

и S только при наличие синхросигнала.

Условное изображение данного триггера

показано на Рис. 4.2

11. Триггер со счетным входом (Т-триггер) и его применение. Триггер Т-типа (от англ. tumble- опрокидываться), или счетный триггер. Этот триггер имеет один информационный вход и переходит в противоположное состояние в результате воздействия на его вход каждого очередного сигнала. На рис.5.2 представлена схема двухтактного асинхронного Т - триггера. На рис.6.2 - его условное изображение.

Т-триггер выполнен на основе двух последовательно соединенных синхронных

RS-триггеров

.При Т=0 сигнал на выходе инвертора равен

1 и триггер Т-2 устанавливается в состояние

равное состоянию триггера Т-1, так как.

сигнапы с выходов Q-1

и Q-1

воздействуют на входы S

и R

триггера Т-2.

Рис.5.2

Рис.5.2

При

Т = 1 сигнал на выходе инвертора равен 0

и состояние триггера Т - 2 не изменяется,

так как сигналы с выходов Q-1,

Q-1

не проходят в Т-2. В то же время Т-1

установится в состояние противоположное

Т-2, так как Q-2

поступает на S

и Q-2

на R

входы триггера Т-1

При

Т = 1 сигнал на выходе инвертора равен 0

и состояние триггера Т - 2 не изменяется,

так как сигналы с выходов Q-1,

Q-1

не проходят в Т-2. В то же время Т-1

установится в состояние противоположное

Т-2, так как Q-2

поступает на S

и Q-2

на R

входы триггера Т-1

Рис. 6.2

Таким образом, на выходах Q-2 ,Q-2, сигналы изменяются на противоположные по окончании каждого очередного импульса Т, что соответствует диаграмме рис. 7.2.

Рис.7.2

Рис.7.2

12-13. Регистры. Устройство называемое регистром служит для хранения чисел в двоичном коде. С помощью регистров выполняются такие действия над числами, как передача их из одного устройства в другое, арифметический и логический сдвиг в сторону младших или старших разрядов, преобразование кода из последовательного в параллельный и наоборот и т.д. Функциональная схема регистра параллельного типа на RS-триггерах приведена на

Рис.

1.3

Рис.

1.3

Информация в регистр записывается при наличии логической единицы на входе “вход”. Тогда входные сигналы параллельного входа установят в соответствующее состояние тригерры Т1 – Тn. На выходе регистра информация появится при наличии логической единицы на входе “вывод”. При считывании информация, записанная в регистре, сохраняется. Перед вводом информации регистр устанавливается в нулевое состояние при подаче логической единицы на шину “сброс”.

Регистр сдвига (сдвигающий регистр)

Данный регистр предназначен для выполнения операции сдвига слова информации, то есть для перемещения всех цифр слова в направлении от старших к младшим разрядам (сдвиг вправо) или наоборот (сдвиг влево). Схема сдвигающего регистра на JK-триггерах показана на рис.2.3

Здесь информация, поступившая на вход регистра, по окончании каждого синхронизирующего импульса передается (продвигается) из предыдущего триггера в последующий. Пусть требуется записать в регистр трехразрядное двоичное число X=CBA = 101, Т.е.имеющее разряды А= 1, B= 0, C = 1.На вход подается двоичное слово последовательно разряд за разрядом(младшим разрядом-А вперед). По окончании первого синхронизирующего импульса триггер ТT1 установится в состояние 1(Q1 = 1), поскольку JK-триггер работает как синхронный двухтактный RS-триггер.Таким образом,по окончании первого синхроимпульса Q1=A=1. Затем на информационный вход регистра поступает второй разряд B= 0 слово X. При воздействии второго синхроимпульса триггер ТT2 воспримет информацию с выхода первого триггера. По окончании второго синхроимпульса Q2 =А= 1, а первый триггер воспримет входную информацию регистра и на его выходе Q1 = B = 0. Таким образом, произошел сдвиг информации из первого разряда регистра во второй; точно также по окончании третьего синхроимпульса Q3 = A = 1, Q2 = B =0, Q1 = C = 1 и все слово будет записано в регистр. Считывать информацию из регистра сдвига можно либо в последовательном коде с выхода Q3, продвигая информацию через все разряды регистра к выходу,

либо в параллельном коде одновременно с выходов трех триггеров. Если каждый триггер снабдить отдельным кодом, то данные могут вводиться параллельно через эти входы.

14. Цифровой асинхронный счетчик. Цифровым счетчиком импульсов называют устройство, реализующее счет числа входных импульсов и фиксирующее это число. Обычно счетчики строят на основе триггеров, поэтому счет импульсов ведется в двоичной системе счисления. Функциональная схема двоичного четырехразрядного счетчика приведена на рис.

Схема

состоит из четырех последовательно

соединенных Т-триггеров, выполненных

на основе универсальных JK-триггеров.

Выходы всех триггеров первоначально

можно установить в нулевое состояние

подавая на короткое время логическую

1 на общий вход сброса . Входные им пульсы

поступают на счетный вход левого

триггера. По окончании первого входного

импульса левый триггер Т0

перейдет в состояние 1. По окончании

второго входного импульса триггер Т0

перейдет в положение 0, а следующий

триггер Т1

в состояние 1 и т.д. После шестнадцатого

входного импульса все триггеры переходят

в состояние 0, и счет повторяется.

Единичные выходы триггеров отражают

число поступивших на вход счетчика

импульсов в двоичной системе счисления.

Результат двоичного счета получается

на выходах с А по D

и, поэтому число следует читать в порядке

DCBA.

Общее число возможных состояний (модулей)

М счетчика определяют числом триггеров

n:

М = 2n.

В нашем случае М = 16. Для получения

счетчика с другим коэффициентом пересчета

(модулем) применяют обратные связи. На

рис. 4.3 изображена схема десятичного

счетчика импульсов, то есть c

М = 10. Наличие двух входов сброса у схемы

позволяет организовать и получить

разные коэффициенты пересчета и, в

частности, М = 10. В нашем случае счетчик

автоматически сбрасывается в 0 , когда

на выходах не появится комбинация 1010.

Таким образом десятый импульс переводит

все триггеры в состояние 0, и счет

начинается снова. Другие комбинации

обратных связей позволяют построить

счетчик с другим модулем пересчета.

Схема

состоит из четырех последовательно

соединенных Т-триггеров, выполненных

на основе универсальных JK-триггеров.

Выходы всех триггеров первоначально

можно установить в нулевое состояние

подавая на короткое время логическую

1 на общий вход сброса . Входные им пульсы

поступают на счетный вход левого

триггера. По окончании первого входного

импульса левый триггер Т0

перейдет в состояние 1. По окончании

второго входного импульса триггер Т0

перейдет в положение 0, а следующий

триггер Т1

в состояние 1 и т.д. После шестнадцатого

входного импульса все триггеры переходят

в состояние 0, и счет повторяется.

Единичные выходы триггеров отражают

число поступивших на вход счетчика

импульсов в двоичной системе счисления.

Результат двоичного счета получается

на выходах с А по D

и, поэтому число следует читать в порядке

DCBA.

Общее число возможных состояний (модулей)

М счетчика определяют числом триггеров

n:

М = 2n.

В нашем случае М = 16. Для получения

счетчика с другим коэффициентом пересчета

(модулем) применяют обратные связи. На

рис. 4.3 изображена схема десятичного

счетчика импульсов, то есть c

М = 10. Наличие двух входов сброса у схемы

позволяет организовать и получить

разные коэффициенты пересчета и, в

частности, М = 10. В нашем случае счетчик

автоматически сбрасывается в 0 , когда

на выходах не появится комбинация 1010.

Таким образом десятый импульс переводит

все триггеры в состояние 0, и счет

начинается снова. Другие комбинации

обратных связей позволяют построить

счетчик с другим модулем пересчета.

15. Синхронный счетчик. Все счетчики рассмотренные ранее состояли из последовательно переключаемых триггеров. Такая конструкция имеет недостаток, заключающийся в наличии конечного времени переходного процесса в схеме, где триггеры не переключаются вместе. Поэтому такие счетчики называются асинхронными. В асинхронных счетчиках возможны ложные срабатывания, если сигналы с выходов счетчика используются в качестве тактовых импульсов для других схем. В синхронном четырехразрядном счетчике (рис. 5.3) за счет использования схем совпадений достигается одновременное переключение всех триггеров, Например, у первого тригерра (младший значащий разряд А) J = K = 1, так, что он изменяет свое состояние с каждым входным испульсом. У второго триггера (В) J= K = A, поэтому он переключается

только в том случае, когда А = 1. Третий триггер (С) может переключаться только тогда, когда и А и В равны 1, в то время как четвертому триггеру D для переключения необходимо равенство 1 С, В и А.

16.

Дешифратор и его применение.

Дешифратор (декодер) — комбинационное

устройство, преобразующее n-разрядный

двоичный, троичный или k-ичный код

в ![]() -ичный

одноединичный код, где

-ичный

одноединичный код, где ![]() -

основание системы счисления. Логический

сигнал появляется на том выходе,

порядковый номер которого соответствует

двоичному, троичному или k-ичному

коду.

Дешифраторы являются устройствами,

выполняющими двоичные, троичные или k-ичные логические

функции (операции).

-

основание системы счисления. Логический

сигнал появляется на том выходе,

порядковый номер которого соответствует

двоичному, троичному или k-ичному

коду.

Дешифраторы являются устройствами,

выполняющими двоичные, троичные или k-ичные логические

функции (операции).

Двоичный дешифратор работает по следующему принципу: пусть дешифратор имеет N входов, на них подано двоичное слово xN − 1xN− 2...x0, тогда на выходе будем иметь такой код, разрядности меньшей или равной 2N, что разряд, номер которого равен входному слову, принимает значение единицы, все остальные разряды равны нулю. Очевидно, что максимально возможная разрядность выходного слова равна 2N. Такой дешифратор называется полным. Если часть входных наборов не используется, то число выходов меньше 2N, и дешифратор является неполным.

Часто дешифраторы дополняются входом разрешения работы. Если на этот вход поступает единица, то дешифратор функционирует, в ином случае на выходе дешифратора вырабатывается логический ноль вне зависимости от входных сигналов.

Существуют дешифраторы с инверсными выходами, у такого дешифратора выбранный разряд показан нулём.

Функционирование дешифратора описывается системой конъюнкций:

![]()

![]()

![]()

…………………………………………………………

![]()

![]()

Обратное преобразование осуществляет шифратор.

17. Мультиплексор. Мультиплексором называют устройство, позволяющее подключаться к выходам различных устройств и передавать с них данные в нужные места. Например, если нужно сложить числа, имеющиеся на выходах двух регистров, то следует обеспечить подключение выходов этих регистров ко входам сумматора для выполнения данной операции. В другой раз на входы сумматора нужно подавать информацию со счетчиков.

Простейшим примером мультиплексора является одноканальный мультиплексор на два входа, условное изображение которого представлено на рис

![]()

Данный мультиплексор имеет один адресный вход А и два информационных входа Х1, Х2.

При А = 0 Y = Х1

При A = 1 Y = X2

Таким образом мультиплексор передает сигналы Х1 или Х2 на выход Y в зависимости от кода адреса А. Это пример двухканального мультиплексора(2 х 1).

Работу этого мультиплексора можно описать таблицей истинности(Таблица 1 )

По таблице истинности можно составить логическое выражение мультиплексора.

Y = A X1 X2 + A X1 X2 + A X1 X2 + A X1 X2 = A X1 (X2 + X2) +

+ A X2 (X1 + X1) =A X1 + A X2

По

полученному логическому выражению

можно построить схему мультиплексора

Рис

18. Полусумматор — логическая схема, имеющая два входа и два выхода (двухразрядный сумматор, бинарный сумматор). Полусумматор используется для построения двоичных сумматоров. Полусумматор позволяет вычислять сумму A+B, где A и B — это разряды двоичного числа, при этом результатом будут два бита S,C, где S — это бит суммы по модулю, аC — бит переноса. Однако, как можно заметить, для построения схемы двоичного сумматора (трёхразрядный сумматор, тринарный сумматор) необходимо иметь элемент, который суммирует три бита A, B и C, где C — бит переноса из предыдущего разряда, таким элементом является полный двоичный сумматор, который как правило состоит из двух полусумматоров и логического элемента 2ИЛИ.

Двоичный полусумматор. Представляет собой объединение двух бинарных (двухоперандных) двоичных логических функций: сумма по модулю два - s и разряд переноса при двоичном сложении - c.

19. Полный Сумматор. Сумматором называется узел цифрового вычислительного устройства, выполняющий суммирование кодов чисел. При сложении двух многоразрядных чисел независимо от системы счисления в каждом разряде производится сложение трех цифр: цифры рассматриваемого разряда первого слагаемого, цифры рассматриваемого разряда второго слагаемого и цифры переноса из соседнего с рассматриваемым младшего разряда. При сложении каждого разряда многоразрядных чисел получается значение суммы для рассматриваемого разряда и единица переноса в следующий, старший по отношению к рассматриваемому разряд, если она возникает. Из сказанного выше следует, что многоразрядный сумматор должен состоять из соединенных определенным образом одноразрядных сумматоров. Одноразрядный двоичный сумматор представляет собой логическую схему, имеющую три входа и два выхода. На входы поступают цифры рассматриваемого разряда двух слагаемых аi и bi и единица переноса из соседнего младшего разряда Рi-1, а на выходах получаются цифра суммы Si и цифра переноса в следующий разряд Рi. Логика работы одноразрядного двоичного сумматора поясняется Таблица 2

-

Ai

Bi

Pi-1

Si

Pi

0

0

0

0

0

0

1

0

1

0

1

0

0

1

0

1

1

0

0

1

0

0

1

1

0

0

1

1

0

1

1

0

1

0

1

1

1

1

1

1

Одноразрядный двоичный сумматор может быть построен на основе двух полусумматоров HA (схем сложения по модулю 2). Полусумматор реализует сложение двух двоичных цифр без учета переноса из соседнего младшего разряда. Схемы полусумматора и полного сумматора представлены на рис

Особенность данных сумматоров в том, что выходные сигналы каждой схемы определяются в любой момент комбинацией входных сигналов, поданных одновременно на ее входы. Снятие сигналов приводит к исчезновению выходных сигналов. Такие сумматоры называют комбинационными сумматорами. Результат сложения в комбинационных сумматорах обычно запоминается в отдельных триггерных регистрах.

20.Многоразрядные параллельные сумматоры. На основе одноразрядных строят многоразрядные сумматоры. Наибольшее распространение получили сумматоры параллельного действия. В параллельном сумматоре все разряды чисел обоих слагаемых одновременно подаются на входы одноразрядных сумматоров, в которых образуются разрядные суммы и переносы. В работе исследуется параллельный трехразрядный сумматор с последовательным переносом.

В данной схеме бит переноса из старшего разряда сумматора становится старшим разрядом суммы.

21-22.Принцип прогр. управл. в ЭВМ. Взаимод. устройств ЭВМ на уровне маш.команд

Структура и виды команд

Решение задач на ЭВМ реализуется программным способом, т. е.путем выполнения последовательно во времени отдельных операций над информацией, предусмотренных алгоритмом решения задачи.

Алгоритм - это точно определенная последовательность действий, которые необходимо выполнить над исходной информацией, чтобы получить решение задачи.

Алгоритм решения задачи, заданный в виде последовательности команд на языке вычислительной машины (в кодах машины), называется машинной программой.

Команда машинной программы (иначе, машинная команда) - это элементарная инструкция машине, выполняемая ею автоматически без каких-либо дополнительных указаний и пояснений. Машинная команда состоит из двух частей: операционной и адресной. Операционная часть команды - это группа разрядов в команде, предназначенная для представления кода операции машины. Адресная часть команды - это группа разрядов в команде, в которых записываются коды адреса (адресов) ячеек памяти машины, предназначенных для оперативного хранения информации, или иных объектов, задействованных при выполнении команды. Часто эти адреса называются адресами операндов, т.е. чисел, участвующих в операции.

По количеству адресов, записываемых в команде, команды делятся на безадресные, одно-, двух- и трехадресные.

Типовая структура трехадресной команды:

КОП а1 а2 а3, где КОП -код операции;

а1 и а2 - адреса ячеек (регистров), где расположены соответственно первое и второе числа, участвующие в операции;

а3 - адрес ячейки (регистра), куда следует поместить число, полученное в результате выполнения операции.

Типовая структура двухадресной команды:

КОП а1 а2

где a1 - это обычно адрес ячейки (регистра), где хранится первое из чисел, участвующих в операции, и куда после завершения операции должен быть записан результат операции;

а2 -обычно адрес ячейки (регистра), где хранится второе участвующее в операции число.

Типовая структура одноадресной команды:

КОП а1

где a1 в зависимости от модификации команды может обозначать либо адрес ячейки (регистра), где хранится одно из чисел, участвующих в операции, либо адрес ячейки (регистра ), куда следует поместить число результат операции.

Безадресная команда содержит только код операции, а информация для нее должна быть заранее помещена в определенные регистры машины (безадресные команды могут использоваться только совместно с командами другой адресности).

Пример: Поступила представленная на языке символического кодирования команда: СЛ 0103 5102

Такую команду следует расшифровать так: "сложить число, записанное в ячейке 0103 памяти, с числом, записанным в ячейке 5102, а затем результат (т.е. сумму) поместить в ячейку 0103".

Примечание. В кодах машины такая команда содержит только двоичные цифры записанных выше объектов.

Состав машинных команд

Современные ЭВМ автоматически выполняют несколько сотен различных команд. Например, стандартный набор современных ПК содержит около 240 машинных команд. Все машинные команды можно разделить на группы по видам выполняемых операций: операции пересылки информации внутри ЭВМ; арифметические операции над информацией;

логические операции над информацией; операции обращения к внешним устройствам ЭВМ; операции передачи управления;

обслуживающие и вспомогательные операции.

Пояснения требуют операции передачи управления (иначе ветвления программы), которые служат для изменения естественного порядка выполнения команд. Бывают операции безусловной передачи управления и операции условной передачи управления.

Операции безусловной передачи управления требуют выполнения после данной команды не следующей по порядку, а той, адрес которой в явном или неявном виде указан в адресной части.

Операции условной передачи управления требуют тоже передачи управления по адресу, указанному в адресной части команды, но только в том случае, если выполняется некоторое заранее оговоренное для этой команды условие. Это условие в явном или неявном виде указано в коде операции.