Lektsii_mikroprotsessory

.pdf

41

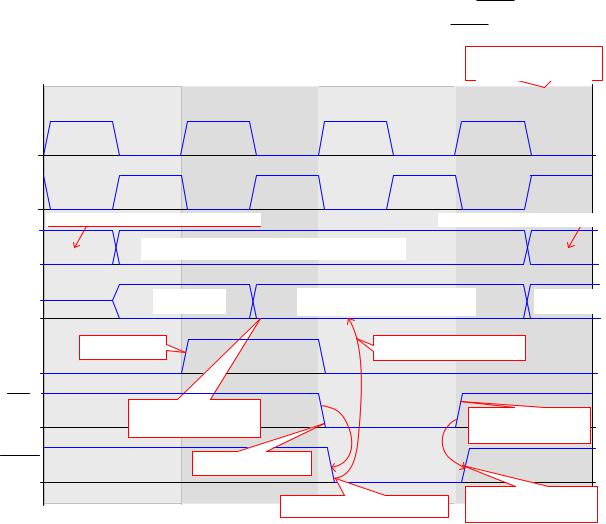

Вывод в порт интерфейса внешнего устройства

Этим машинным циклом процессор выполняет команду OUT Port – вывод байта данных из аккумулятора в регистр интерфейса (порт Port) внешнего устройства. Как представленная выше команда IN Port, данная команда по формату двухбайтная. Port в составе команды – второй еѐ байт, который является адресом регистра интерфейса.

Временные диаграммы данного машинного цикла приведены на рис. 2.17. Однобайтный адрес порта, выставляемый в первом такте на линии адреса будет дублироваться как в старшие 8 разрядов адресной шины (A8..15) так и в младшие 8 разрядов (A0..7). Поэтому логика дешифрации адреса может быть построена, на выбор разработчика, либо на старшей, либо на младшей частях адресной шины. Ввод из порта аналогичен записи в память. Отли-

чие состоит в том, что в при вводе из порта вместо сигнала MWR , системный |

||||

контроллер сформирует для стробирования ввода сигнал IOWR . |

||||

|

|

|

|

Начало следующего |

|

|

|

|

машинного цикла |

|

T1 |

T2 |

T3 |

T1 |

CLK1 |

|

|

|

|

CLK2 |

|

|

|

|

|

Адрес 2-го байта команды OUT port |

Адрес следующей команды |

||

|

|

Адрес порта, взятый из принятой команды |

|

|

D0..7 |

|

PSW = 10h |

Записываемый в порт байт |

PSW = A2h |

SYNC |

Приѐм PSW |

Интерфейс принял байт |

||

WR |

|

Процессор выставил |

|

|

|

|

|

Процессор убрал |

|

|

|

байт на шину |

|

|

|

|

|

строб записи |

|

|

|

|

|

|

IOWR |

|

Дешифрация PSW |

|

|

|

|

|

Обращение к интерфейсам |

Интерфейс отключил |

|

|

|

регистр от шины |

|

|

|

|

|

|

Рис. 2.17. Временные диаграммы машинного цикла вывод в порт.

Прерывание

Как отмечалось выше при описании логики управления прерываниями, машинный цикл прерывания – один из элементов механизма прерываний процессора (рис. 2.11). В этом машинном цикле процессор выполняет чтение

42

от инициатора прерывания одного байта команды вызова подпрограммы обслуживания прерывания.

Все рассмотренные ранее машинные циклы были причинно-обусловлены логикой программных действий процессора, последовательностью движения процессора по интерпретации команд, реализующий алгоритм программного управления.

Отличительная особенностью машинного цикла прерывания является его причинная обусловленность логикой внешних событий, воздействующих на процессор и переключающих его на программные обслуживания этих внешних событий через механизм прерываний.

Возможность перехода к выполнению машинного цикла прерывания связана с обнаружением логикой процессора факта установки триггера запроса к моменту завершения текущей команды. Этот триггер устанавливается сигналом INT при наличии установленного триггера запросов (рис. 2.11).

Временные диаграммы машинного цикла прерывания представлены на рис. 2.18. Они напоминают машинный цикл чтения памяти, рассмотренный выше.

Особенности диаграмм данного цикла состоят в следующих моментах. Показаны события завершающего такта команды, при интерпретации

которой пришѐл запрос прерывания, поскольку именно в нѐм процессор определяется с необходимостью выполнения машинного цикла прерывания.

Не актуальны в данном цикле линии адреса, поскольку механизм прерываний процессора предполагает наличие только одного инициатора прерывания. Для его выбора используется линия INTA .

Добавлены диаграммы сигналов элементов логики управления прерываниями из схемы на рис. 2.11.

Из анализа механизма прерываний процессора следуют требования к инициатору прерывания. Одно из них связано формированием сигнала запрос прерывания. Поскольку в момент прихода запроса INT процессор выполняет очередную команду, он "не замечает" запроса да завершения команды. Если запрос не удерживать достаточное время, он может быть проигнорирован, поэтому время активности сигнала INT должно быть больше самой длинной команды.

Механизм прерываний процессора создаѐт основу механизма прерываний микро-ЭВМ.

Останов

К машинному циклу останов процессор приходит в фазе выполнения команды HLT (останов). Он посвящѐн действиям приводящим процессор из состояния выполнения программы к состоянию останова, описанному выше.

|

|

|

43 |

|

|

|

T3 |

T1 |

T2 |

|

T3 |

CLK1 |

|

|

|

|

|

CLK2 |

|

|

|

|

ИП убрал |

|

|

|

|

|

|

|

|

|

|

|

байт команды |

D0..7 |

|

|

PSW = 03h |

Команда RST n |

|

|

|

Приѐм PSW |

|

ИП выставил |

|

SYNC |

|

|

байт команды |

||

|

|

|

|

||

DBIN |

|

|

Дешифрация PSW |

|

|

|

|

|

|

Процессор |

|

|

|

|

|

принял байт в |

|

INTA |

|

|

|

IR и снял DBIN |

|

|

|

|

|

|

|

|

|

|

Подключение к шине |

|

Отключение |

INTE |

Процессор сбросил |

инициатора прерывания (ИП) |

от шины ИП |

||

|

|

|

|

||

|

триггер разрешения |

|

|

|

|

INT |

|

С этого момента ИП может убрать запрос |

|

||

T_Int |

|

|

|

|

|

|

|

|

Процессор сбросил |

|

|

Завершающий такт команды, при |

триггер запроса |

|

|

||

|

|

|

|||

итерпретации которой пришѐл запрос |

|

|

|

||

Рис. 2.18. Временные диаграммы машинного цикла прерывания.

Прерывание при останове

Машинный цикл прерывание при останове отличается от машинного цикла прерывания тем, что перед началом данного машинного цикла процессор не выполняет очередную команду, а пребывает в состоянии останова при наличии установленного триггера разрешения прерываний. Поэтому после поступления запроса на вход INT, процессору нет необходимости затрачивать время на выполнение текущей команды. Процессор сразу, с началом следующего такта после прихода INT, установит триггер запроса прерывания и выполнит выход из состояния останова путѐм сброса бита подтверждения останова в слове состоянии PSW. Этот такт будет первым тактом машинного цикла прерывания и далее он будет протекает как обычный машинный цикл прерывания.

44

Библиографический список к теме 4

1.Угрюмов Е. П. Цифровая схемотехника: Учеб. пособие для вузов. – СПб.: БВХ-Петербург, 2005. – 800 с.

2.Пухальский Г. И. Проектирование микропроцессорных устройств: Учебное пособие для вузов. – Санкт-Петербург, 2001 – 544 с.

3.Управляющие и вычислительные устройства робототехнических комплексов на базе микро-ЭВМ: Учебное пособие для техн. вузов/ В. С.Медведев, Г. А. Орлов, Ю. И. Рассадкин и др.; Под ред. В. С. Медведева. –

М.: Высш. шк., 1990 – 239 с.

4.Григорьев В. Л. Программное обеспечение микропроцессорных систем. – М.: Энергоатомиздат, 1983 – 203 с.

5.Каган Б. М., Сташин В. В. Основы проектирования микропроцессорных устройств автоматики. – М.: Энергоатомиздат, 1987 – 304 с.

6.Левенталь Л., Сэйвилл У. Программирование на языке ассемблера для микропроцессоров 8080 и 8085: Пер. с англ. – М.: Радио и связь, 1987. – 448 с.

7.Балашов Е. П., Пузанков Д. В. Микропроцессоры и микропроцессорные системы. – М.: Радио и связь, 1981 – 326с.

Тема 5. Запоминающие устройства

Иерархическая структура памяти микро-ЭВМ

Память представляет собой компонент микро-ЭВМ, обеспечивающий хранение информации, а также возможности процессору еѐ обновления (запись) и чтения. Технические (аппаратные) средства, реализующие такие функции памяти называют запоминающими устройствами (ЗУ).

Главные требования к памяти большой объѐм хранимой информации;

быстрота доступа к элементам хранимой информации.

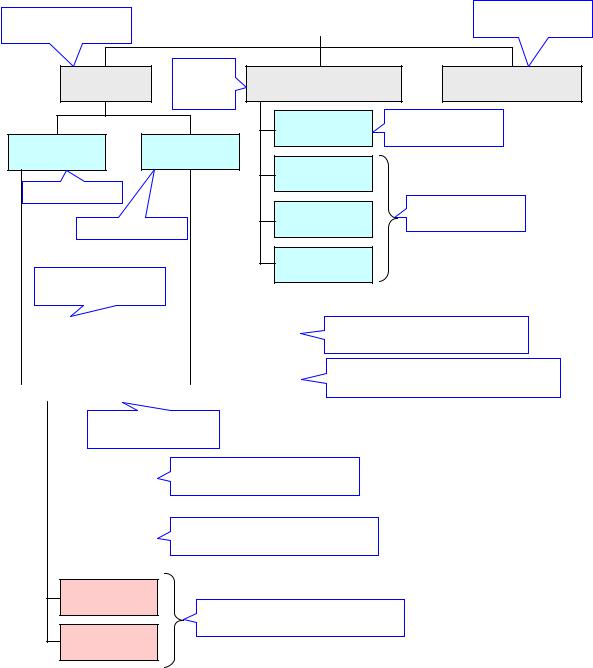

Эти требования очевидно противоречивы и приоритет одному из них отдаѐтся, в зависимости от типа хранимой информации. Поэтому запоминающие устройства системы памяти разделены и имеют многоступенчатую иерархическую структуру (рис. 3.1).

Уровни, следуют друг за другом, начиная с ближайшего к процессора. Рабочие регистры процессора – наиболее быстро доступная (сверхопе-

ративная) память за счѐт местоположения внутри процессора. Она и обновляется наиболее часто.

Кэш-память – место хранения команд и данных очередных и ближайших, с которыми процессор будет работать в последующих шагах программы. Внутренняя кэш-память рассчитана для работы на частоте процессора (наибольшей), потому она быстрее других стоящих дальше в иерархии. Внешняя кэш-память работает на частоте шины, но она строится на более быстрых (и дорогих) элементах чем основная память. Кэш-память осуществляет

45

буферное хранение ближайших в очереди к процессору команд и данных, приходящих из основной памяти.

Основная память рассчитана на максимальный объѐм места для программ и данных, которые бы мог отрабатывать высокопроизводительный микропроцессор. Этот объѐм ограничен разрядностью адресной шины. С другой стороны, сочетать требование увеличения этого объѐма и высокого быстродействия мешает фактор стоимости быстродействующих ОЗУ.

Когда пределы ѐмкости основной памяти исчерпаны, в микро-ЭВМ добавляется внешняя память. Она подключается к шине через интерфейс как внешнее устройства. Отсюда еѐ название. Непосредственный доступ процессора к внешней памяти невозможен, а происходит только через еѐ интерфейс, поэтому

o перед началом работы с информацией внешней памяти она должна быть скопирована (загружена) в ОЗУ основной памяти;

o внешняя память – самая медленная память микро-ЭВМ.

Микропроцессор

Рабочие регистры (сверхоперативная память)

Внутренняя кэш-память

Наибольшая скорость обмена, наименьший объѐм

Хранение непосредственно исполняемых фрагментов программ и данных

ОЗУ (RAM) ПЗУ (ROM)

Основная память (ячейки) |

Линии |

|

|

|

управления |

Линии

адреса

Линии

Регистры

данных

Внешняя кэш-память Интерфейс

внешней памяти

Буфер для ближайших текущих команд и данных

Внешняя

Наименьшая скорость память обмена, наибольший объѐм

Рис. 3.1. Структура памяти микро-ЭВМ.

46

Основные параметры запоминающих устройств

Основные параметрами запоминающих устройств являются: информационная ѐмкость; организация; быстродействие; производительность; энергонезависимость.

Информационная ѐмкость – максимально возможный объѐм хранимой информации. Выражается в битах или словах (обычно, словом считается байт). Бит хранится в запоминающем элементе (элементарной ячейке). Слово хранится в запоминающей ячейке или просто ячейке. Добавление к единице измерения множителя означает:

"К" (кило) умножение на 210 = 1024; "М" (мега) умножение на 220 = 1 048 575;

"Г" (гига) умножение на 230 = 1 073 741 824.

Производители микросхем обычно оценивают ѐмкость в битах, а системотехники – в байтах.

Организация запоминающих устройств – произведение числа храни-

мых слов на их разрядность. Это произведение выражает информационную ѐмкость, но одной ѐмкости может соответствовать разная организация. Сомножитель разрядности показывает возможность по доступу к элементам запоминающего устройства за одно обращение:

побитный, например 1М×1; побайтный, например 128К×8;

пословный (два байта), например 32×16.

Быстродействие запоминающих устройств показывает скорость вы-

полнения обменных операций, которую способно поддержать запоминающее устройство. Быстродействие оценивается следующими параметрами:

временем считывания – интервал между моментом появления строба чтения и установкой слова на шину данных (на выход микросхемы памяти);

временем записи – интервал от момента появления строба чтения до установления состояния ячейки, определяемого входным с шины данных словом;

длительность циклов доступа (чтения/записи) – интервал между последовательными повторными операциями доступа, учитывающий время необходимое для восстановления начального состояния запоминающего устройства после предыдущего обращения;

другие дополнительные параметры для новых устройств. Производительность (или полоса пропускания) запоминающих уст-

ройств определяется как произведение числа считанных (записанных) слов на их разрядность. Например, микросхема памяти с темпом передачи 50 МГц при разрядности 8 бит будет иметь производительность

47

50 МГц × 8 = 400 Мбит/с.

Энергонезависимость – способность сохранять данные при отключении питания. Энергонезависимость может быть:

искусственной – присущей самим запоминающим элементам; естественной – достигаемой за счѐт дополнительных источников пи-

тания, автоматически подключаемых после отключения основных источников.

Классификация запоминающих устройств микро-ЭВМ

Основным классификационным признаком запоминающих устройств микро-ЭВМ является способ доступа к данным, характеризующий логическую организацию взаимодействия процессора с памятью.

Различаются следующие варианты доступа к данным: адресный или произвольный, последовательный, ассоциативный.

Структурно классификация запоминающих устройств микро-ЭВМ представлена на рис. 3.3.

Адресный или произвольный доступ

При адресном или произвольном доступе код на адресных линиях прямо и однозначно указывает на выбираемую ячейку. Все ячейки равнодоступны. Этим способом адресуются как команды так и данные.

Адресные запоминающие устройства по физической организации делятся на

оперативные, ОЗУ (стандартное международное обозначение: RAM – Random Access Memory – память с произвольным доступом);

постоянные, ПЗУ (ROM – Read Only Memory – память только для чте-

ния).

|

|

48 |

|

|

|

|

|

|

|

|

|

Запоминающие устройства микроЭВМ |

|

Доступ по |

Произвольный доступ |

|

|||

|

|

заданному признаку |

||

по заданному адресу |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Доступ |

|

|

Адресные |

упорядо- |

Последовательные |

Ассоциативные |

|

ченный |

|

|

|

|

LIFO |

Последним пришѐл |

|

|

– первым вышел |

|

|

|

|

|

ROM |

RAM |

|

|

|

|

FIFO |

|

Постоянные ЗУ |

|

|

|

|

|

|

Первым пришѐл – |

Оперативные ЗУ |

Файловые |

первым вышел |

|

|

|

||

|

|

Циклические |

|

ПЗУ без перепрограм- |

|

|

|

мирования |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROM (Mask) |

|

|

|

|

|

SRAM |

|

|

|

|

Статические ОЗУ |

|

|||

|

|

|

|

|

|

|

(запоминающий элемент – триггер) |

|

||||||||

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Динамические ОЗУ |

|

|

|

|

PROM |

|

|

|

|

|

DRAM |

|

||||||

|

|

|

|

|

|

|

|

|

|

(запоминающий элемент – конденсатор) |

||||||

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

ПЗУ с перепрограм- |

|

|

|

|

|

|

||||||

|

|

|

|

мированием |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EPROM-OTP |

|

|

|

|

ПЗУ однократно |

|

|

|

|

|

|||

|

|

|

|

|

программируемое у заказчика |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EPROM |

|

ПЗУ многократно программируемое |

|

||||||||||

|

|

|

|

|

|

стираемое ультрафиолетом |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EEPROM

ПЗУ многократно программируемое стираемое электрически

FLASH

Рис. 3.3. Классификация запоминающих устройств микро-ЭВМ.

Постоянные запоминающие устройства могут не допускать изменения информации пользователем или позволять это делать при помощи специальных средств (программаторов). Программируются в процессе изготовления и не допускают возможности стирания первоначальной информации масочные ROM (Mask). Остальные четыре разновидности, по-разному, допускают перепрограммирование поэтому именуются PROM – Programmable ROM или в русской терминологии ППЗУ (программируемые ПЗУ).

ПЗУ многократно репрограммируемые именуется РПЗУ или EPROM – Erasable Programmable ROM. Технология репрограммирования перед новым

49

программированием EPROM предполагает стирание старой информации. В зависимости от способа стирания EPROM подразделяются на две группы:

стираемые ультрафиолетовым облучением; стираемые электрическим способом.

EPROM стираемые ультрафиолетовым облучением – называют либо просто EPROM, либо UV-EPROM (Ultra-Violet Erasable Programmable ROM).

Русское название – РПЗУ-УФ. На корпусах таких микросхем имеется специальное прозрачное окошко для облучения, поэтому корпуса относительно дороги.

Отказ от сложных и дорогих корпусов с окошком, замена их на обычные дешѐвые пластмассовые без изменения внутреннего содержимого микросхем привѐл к появлению памяти типа EPROM-OTP (One Time Programmable). Она допускает только однократное программирование. Микросхемы EPROM-OTP покупаются чистыми, затем при помощи программатора пользователь записывает нужную ему информацию. Ультрафиолетовым облучение такие микросхемы не стираются, ввиду отсутствия окошка.

Электрически стираемые EPROM называются EEPROM (Electrical Erasable Programmable ROM) или E2PROM. Русское название – РПЗУ-ЭС.

Запоминающие элементы типа FLASH стираются и программируются электрическим способом подобно микросхемам EEPROM. Но ряд структурных и технологических особенностей выделяет еѐ в отдельный вид.

Оперативные запоминающие устройства (RAM) подразделяются по физической организации на

статические SRAM (Static RAM), динамические DRAM (Dynamic RAM).

ВSRAM запоминающий элемент (элементарная ячейка) строится на основе триггера, способного сохранять своѐ состояние сколь угодно долго пока имеется питание.

ВDRAM запоминающий элемент (элементарная ячейка) строится на основе конденсатора, хранящего информацию в виде заряда. Конденсаторы с течением времени разряжаются. Поэтому для сохранения информации в таких ячейках требуется периодическая подзарядка конденсаторов. Такое восстановление информации еще называют регенерацией.

Для обеспечения регенерации требуются специальные аппаратнопрограммные средства. Вследствие необходимости регенерации уменьшается быстродействие памяти, усложняется логика управления памятью. Но преимущества DRAM – большая плотность элементов и дешевизна (почти в 5 раз) по сравнению SRAM делают DRAM наиболее широко применяемым типом памяти.

Разработаны запоминающие устройства с динамическими элементарными ячейками, но имеющие внутреннюю встроенную систему регенерации. Их внешнее поведение не отличается от SRAM. Их называют квазистатическими

RAM.

50

Последовательный доступ Последовательный доступ предназначен для работы только с данными.

Они организуются в виде очереди, построенной по определѐнным правилам. Считывание слов из очереди происходит либо в порядки их записи (первое записанное – читается первым), либо в обратном порядке (последнее записанное – читается первым). Моделью такого запоминающего устройства является цепочка, в которой данные передаются между соседними элементами.

Прямой порядок чередования имеет место в буферах FIFO (First Input – First Output), а также в файловых и циклических запоминающих устройствах.

Буферы FIFO организованы сравнительно проще. Запись поступает в конец пустого буфера и сразу становится доступной, то есть становится в конце цепочки. Например, клавиатурный буфер или буфер последовательного обмена.

Вфайловых запоминающих устройствах данные организуются в виде более сложной блочной структуры, в которой каждый блок имеет начало и конец. Приѐм данных из блока начинается только после обнаружения начала блока.

Вциклических запоминающих устройствах слова доступны одно за другим с постоянным периодом, определяемым ѐмкостью памяти. Например, видеопамять.

Обратный порядок чередования реализован в стековой памяти процес-

сора. Здесь основное правило – LIFO (Last Input – First Output) или "последний пришѐл – первый вышел".

Время доступа к конкретной единице информации хранимой в последовательном запоминающем устройстве является случайной величиной. Мак-

симум времени может потребовать просмотра всего объѐма хранимых данных. Однако наличие правил доступа позволяет сэкономить на подготовке адреса, упростить логику выбора адресата и ускорить процесс выбора.

Ассоциативный доступ

Ассоциативный доступ реализует поиск информации по какому-то заданному признаку, а не по местоположению в памяти (адресу или месту в очереди). В наиболее полной версии все хранимые в памяти слова одновременно проверяются на соответствие признаку, например, на совпадение определѐнных полей слов (тегов – от англ. tag) с признаком, задаваемым входным словом (теговым адресом). На выход выдаются слова, удовлетворяющие признаку. Порядок выдачи слов, когда тегу удовлетворяют несколько слов, а также порядок записи новых данных, может быть различными. Область применения ассоциативной памяти – кэширование данных.

Соотношение разных типов запоминающих устройств на рынке

Доля различных типов микросхем памяти в общем объѐме продаж памяти на мировом рынке по данным на 2003 год представлена в табл. 3.1 .