Lektsii_mikroprotsessory

.pdf

51

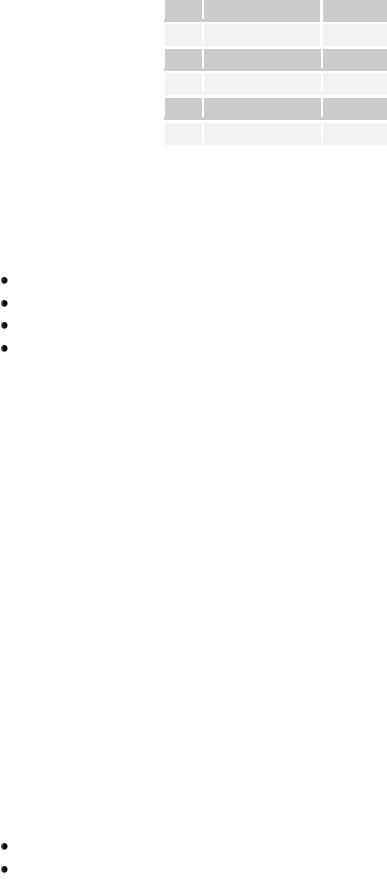

Таблица 3.1

Доли продаж различных типов микросхем памяти

№ |

Тип памяти |

% |

1 |

DRAM |

58 |

2 |

SRAM |

21 |

3 |

FLASH |

13 |

4 |

EEPROM |

5 |

5 |

остальные |

3 |

Постоянные запоминающие устройства

Режимы работы и основные параметры

В постоянных запоминающих устройствах (ПЗУ) с максимальными возможностями предусматриваются четыре режима работы:

хранение информации при отсутствии обращения; чтение хранимой информации; стирание информации;

запись информации при программировании.

Наличие последних двух режимов зависит от типа памяти (табл. 3.2).

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 3.2 |

||

|

Режимы работы для различных типов микросхем ПЗУ |

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROM |

|

|

|

PROM- |

|

|

|

|

EPROM |

|

|

|

EE- |

|

|

|

FLASH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

Режим |

|

|

|

|

|

|

OTP |

|

|

|

|

|

|

|

PROM |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

Хранение информации |

|

|

|

+ |

|

|

|

+ |

|

|

|

+ |

|

|

|

+ |

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

Чтение информации |

|

|

|

+ |

|

|

|

+ |

|

|

|

|

+ |

|

|

|

+ |

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

Стирание |

|

|

|

− |

|

|

|

− |

|

|

|

+ |

|

|

|

+ |

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

Запись (программирование) |

|

|

|

− |

|

|

|

+ |

|

|

|

+ |

|

|

|

+ |

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Хранить информацию в режиме хранения ПЗУ могут бесконечно долго пока она не будет стѐрта в режиме стирания.

Чтения хранимой информации производится достаточно быстро: от нескольких сотен до десятков наносекунд для разных типов микросхем.

Стирание и запись информации гораздо более длительны по времени. Самые быстрые в стирании микросхемы FLASH памяти требуют нескольких секунд, а микросхемы EPROM стираются ультрафиолетом за десятки минут.

Запись в одну ячейку EPROM может потребовать 50 миллисекунд. Если же всего в микросхеме 4 Кбайта ячеек, то потребуется 3,4 минуты. Поэтому такая запись называется программированием.

Основные параметры отечественных EPROM: информационная ѐмкость – до 128 Кбайт; время доступа – 350 нс.

52

Основные параметры отечественных EEPROM: информационная ѐмкость – до 8 Кбайт; время доступа – 250 нс.

Среди зарубежных микросхем EPROM и EEPROM имеются значения параметров:

информационная ѐмкость – до 512 Кбайт; время доступа – 12,5 нс.

Технологии стирания и программирования микросхем ПЗУ

Микросхемы EPROM, рассчитанные на стирание ультрафиолетовым облучением, имеют на корпусе маленькое стеклянное окошко для этой цели. Процесс стирания производится в специальных устройствах – стирателях. Возможно стирание только сразу всех ячеек микросхемы EPROM. Время стирания составляет порядка нескольких минут (или десятков минут для старых типов). Защита информации от стирания – путѐм заклейки окна. Стѐртые ячейки имеют единичные значения всех своих бит. Воздействие ультрафиолета постепенно изменяет свойства материала, поэтому число циклов перепрограммирования ограничено диапазоном от 10 до 100 у микросхем разного качества.

Программированием ПЗУ называется запись информации в ячейки ПЗУ, а устройства обеспечивающие такую запись – программаторами.

Запись может быть произведена в любую ячейку указанием еѐ адреса. Запись каждого бита сводится либо к занесению нулевого значения когда оно требуется, либо к сохранению единичного значения. Когда в ячейку записан «0» – до стирания информацию уже не изменить, а когда после стирания остаѐтся «1» – можно при записи поменять еѐ на «0». Для программирования ячеек EPROM требуется реализовать специальные циклы длительностью порядка десятков миллисекунд с подачей на определѐнный вход микросхем высокого напряжения. В зависимости от типа микросхемы EPROM оно находится в диапазоне от 12 В до 26 В.

Микросхемы EEPROM, рассчитанные на стирание электрическим способом, стираются перед программированием в программаторах. Технология стирания похожа на технологию программирования. Возможность стирание напряжением достигается некоторым усложнением запоминающих элементов, как следствие – увеличение габаритов и стоимости микросхем. Зато у EEPROM появляются преимущества:

стирание отдельных ячеек памяти, задаваемых их адресами; сокращение времени процесса перепрограммирования (стирание-

запись); увеличение числа циклов перепрограммирования до диапазона 104-106;

возможность перепрограммирования без извлечения микросхем из устройства, где они применяются.

Для микросхем FLASH допустимо стирание только сразу всех ячеек или

53

блока ячеек.

FLASH память

Первые микросхемы EEPROM имели традиционную технологию построения ячеек. Но с начала 90-х годов широкое распространение получает новая технология построения ячеек EPROM и FLASH памяти на еѐ основе. В них удалось объединить достоинства EEPROM с достоинствами EPROM. В результате получилось:

высокая плотность ячеек (ячейки на 30% меньше ячеек DRAM); возможность относительно быстрого электрического стирания сразу

многих ячеек микросхемы (1-2 с для всей микросхемы), с которой связано происхождение названия (flash – вспышка);

возможность управления стиранием и программированием ячеек микросхемы без применения дополнительных аппаратных средств из прикладной программы пользователя (цикл программирования байта – 10 мкс);

низкое энергопотребление; высокая надѐжность и количество циклов перепрограммирования прак-

тически не ограниченное.

Преимущество быстрого стирания всей микросхемы оборачивается недостатком – увеличенным временем перепрограммирования отдельных маленьких блоков памяти (чтобы их перепрограммировать надо стереть всю информацию, затем перезаписать всю с изменѐнным маленьким блоком). Для преодоления недостатка современные микросхемы FLASH памяти проектируются с блочной структурой. При этом блоки могут стираться независимо и отдельно друг от друга.

Два основных направления применения FLASH памяти:

хранение не очень часто изменяемой информации (например, обновляемые программы BIOS компьютеров) – Boot Block Flash Memory;

внешняя память взамен памяти на жѐстких дисках – Flash File Memory. Эти направления применения предъявляют различные требования к характеристикам микросхем, в частности, к их структуре. Для Boot Block Flash Memory применяются несимметричные блочные структуры, а для Flash File Memory – симметричные блочные структуры. Разница структур даѐт разные возможности по выборочному стиранию и быстрому перепрограммированию

памяти.

Обозначения микросхем ПЗУ

Среди отечественных микросхем EPROM (в маркировке имеются буквы РФ) наиболее популярна серия К573 с широким набором типономиналов, а среди микросхем EEPROM (в маркировке имеются буквы РР) имеются серии КР558, К1609, К1624, К1626.

Наиболее популярные зарубежные микросхемы EPROM обозначаются 27xx-tt или 27Cxx-tt (CMOS), где xx определяет ѐмкость в Кбитах. Обычно микросхемы имеют байтовую организацию, а tt - время доступа (50-250 нс).

54

Поэтому, например, микросхема типа 27128 представляет собой 16 Кбайтную микросхему EPROM.

Наиболее популярные зарубежные микросхемы для Boot Block Flash Memory обозначаются 28Fxx или 29Fxx.

Статические оперативные запоминающие устройства

Элементы статического ОЗУ (SRAM ) обеспечивают хранение информации в своих ячейках сколь угодно долго пока подается питание. Элементарной ячейкой такого типа оперативной памяти является обычный триггер.

Основная область применения относительно дорогостоящих микросхем SRAM – память с требующая наибольшего быстродействия:

кэш-память компьютеров;

буферы FIFO и LIFO;

внешняя память микроконтроллеров, применяемых в системах встроенного управления.

Режимы работы и основные параметры

Статические ОЗУ предусматривает три режима работы: чтение хранимой информации; запись новой информации;

хранение информации при отсутствии обращения.

Пребывая в режиме хранения, микросхема SRAM может сохранять информацию всѐ время пока на неѐ подаѐтся питание.

Режимы чтения и записи по времени не отличаются, поэтому говорят в времени доступа и оно составляет от сотен до десятков наносекунд. Оно близко времени чтения ПЗУ.

Структура статических ОЗУ чаще всего типа 2DM (в том числе в составе блочных запоминающих устройств). Часть их, при небольшой информационной ѐмкости, строится по структуре 2D, имеются и микросхемы со структурой 2D.

В типичной номенклатуре зарубежных статических ОЗУ имеются микросхемы с параметрами:

информационная ѐмкость – от 8 Кбайт до 1 Мбайт; время доступа – 10-20 нс.

Среди отечественных микросхем наиболее развиты серии К537 и К132, но в настоящее время по своим характеристикам они существенно уступают зарубежным.

Запоминающий элемент статического ОЗУ

Схема запоминающего элемента (ЗЭ) микросхемы статического ОЗУ представлена на рис. 3.11. Она построена на основе четырѐх полевых транзисторов.

|

|

55 |

|

|

|

Состояния транзистора |

Сигналы и их состветствие: |

||||

взависимости от сигнала |

|||||

Логические |

1 |

0 |

|||

на затворе: "1" – открыт; |

|||||

Физические |

Vcc В |

0 В |

|||

"0" – закрыт |

|||||

|

|

|

|||

|

|

|

|

Vcc |

|

|

|

|

R1 |

R2 |

|

|

|

T1 |

|

|

|

|

|

|

|

T3 |

|

Линия выбора |

|

|

|

A |

|

элемента |

|

|

|

||

S1 |

|

|

|

||

|

|

|

|

||

|

|

T2 |

B |

|

|

|

|

|

|

||

Общая линия |

|

|

|

|

|

данных |

|

|

|

T4 |

|

|

|

|

|

||

|

ЗЭ1 |

|

|

|

|

|

S2 |

|

|

|

|

|

ЗЭ2 |

|

|

|

|

|

Sn |

|

|

|

|

|

ЗЭn |

|

|

|

|

Рис. 3.11. Запоминающие элементы SRAM. |

|||||

Транзисторы T3, T4 соединены так, что когда один из них включен, тогда другой обязательно выключен (реализован триггер). Хранимая в ЗЭ информация определяется уровнем сигнала в точке A, а в точке B всегда инверсный сигнал. Выбор ЗЭ1 из множества запоминающих элементов памяти обеспечивает при обращениях процессора входной сигнал S1. Выбранному запоминающему элементу будет отдана на время обращения общая линия данных. На неѐ ключи T1, T2 по сигналу S1 скоммутируют точку хранения информации запоминающего элемента. Двунаправленная линия данных обеспечивает два направления для потока информации: ввод – установку триггера ЗУ при записи информации, и вывод – чтение процессором текущего состояния триггера ЗУ.

В случае записи бит информационных данных процессор устанавливает на общей линии данных. По сигналу S1 этот бит пропускается в ЗЭ и устанавливает триггер: если бит равен "0", то в точке А будет "0"; если бит – "1", то и

56

в точке А установится "1". После снятия сигнала S1 и отключения ЗЭ от линии данных состояние триггера сохранится. Записанный бит будет хранится до новой записи или до снятия питания Vcc.

При чтении ЗЭ линия данных становится выходной, а процессор подготовлен к приѐму. По сигналу S1 ключи T1, T2 коммутируют информационный бит данных на общую линию данных. Информационный бит данных принимается процессором.

Микросхема статического ОЗУ

Рассмотрим далее структуру типичной микросхемы статического ОЗУ емкостью 64 Кбит с организацией 8 К × 8 бит (рис. 3.12). Структура относится к типу 3D. В ней 8 линий данных. Запоминающие элементы образуют 8 матриц M1..M8, состоящих из 256 строк и 32 столбцов. Считывание и запись данных выполняются побайтно, то есть одновременно из восьми ЗЭ, расположенных в одной строке и одном столбце, но разных матриц. Номер строки кодируется восемью старшими разрядами адреса A5..A12, в то время как младшие пять разрядов адреса A0..A4 кодируют столбец.

При чтении информации из памяти процессор сформирует:

адрес читаемой ячейки на линиях A0..A12, чтобы выбрать строку и столбец одновременно в восьми матрицах;

сигнал CS = "0" (выбор кристалла);.

сигнал WR / RD = "1" (строб чтения/записи).

Эта комбинация управляющих сигналов откроет вентиль чтения GR и закроет вентиль записи GW буфера данных. Содержимое восьми ЗЭ из каждой матрицы скоммутируется на линии DI0..DI7 чтобы процессор его принял в свой регистр.

При записи информации в память процессор установит:

адрес записываемой ячейки на линиях A0..A12, чтобы выбрать строку и столбец одновременно в восьми матрицах;

сигнал CS = "0";.

данные для записи на линиях DI0..DI7;

сигнал WR / RD = "0".

Эта комбинация управляющих сигналов откроет вентиль записи GW и закроет вентиль чтения GR буфера данных.В результате в восемь ЗЭ разных матриц, указанных выбранными строкой и столбцом запишется установленная процессором на линиях A0..A12 двоичная информация.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

57 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

Адрес слова |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

A0..A12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

Адрес строки |

|

|

|

|

|

|

|

|

|

|

|

|

|

Адрес столбца |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

A5..A12 |

|

|

|

|

|

A0..A4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

Дешифратор столбца |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

(s=8) |

|

|

|

|

|

(r=5) |

|

|

|

2 |

5 |

= 32 выхода |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

Дешифратор строки |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

28 = 256 выходов |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DCc |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

SL1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SC1 |

SC2 |

|

|

|

|

|

|

|

|

|

SC32 |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

SL2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SC2 |

|

|

|

|

|

|

|

|

|

SC2 |

|

|

|

|

|

|

SC2 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SC |

1 |

SC32 |

|

|

|

|

|

SC1 |

SC32 |

|

|

|

|

SC1 |

SC32 |

|||||||||||||||||

|

|

|

|

|

DCL |

|

|

|

|

SL1 |

|

|

|

|

|

|

SL1 |

|

|

|

|

|

|

|

|

SL1 |

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SL2 |

M8 |

SL2 |

M7 |

SL2 |

M1 |

SL256 |

256×32 |

SL256 |

256×32 |

SL256 |

256×32 |

|

|

|

|||

CS |

D7 |

|

D6 |

|

D0 |

SL256 |

|

|

|||

|

|

|

|

|

Выбор

микросхемы

WR / RD

&

& |

Cтроб чтения/записи

Буфер данных

(8)

GR

GW

(8) |

Слово данных

DIO0..DIO7

Рис. 3.12. Структура микросхемы SRAM.

Модуль статического ОЗУ

На основе представленных выше микросхем можно организовать модуль статического ОЗУ объемом до 64 Кбайт. Вариант с максимальным объѐмом представлен на рис. 3.13. У микросхем объединяют поразрядно линии адреса A0..A12, линии данных D0..D7, а также все одноимѐнные управляющие сигналы.

58

Для выбора микросхемы к ячейке которой выполняется обращение применѐн дешифратор выбираемой микросхемы. На его 3-разрядный вход скоммутированы три старших разряда адресной шины A13..A15. Их комбина-

цией в моменты обращения процессора, сопровождаемые стробами MRD или

MWR , производится активизация одного из выходов дешифратора, подклю-

чѐнного к входу CS соответствующей микросхемы DD1..DD7.

Если необходимо организовать модуль для шины микро-ЭВМ разрядность которой превышает разрядность шины данных микросхемы памяти,

схема модуля строится с параллельным выбором нескольких микросхем.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Шина адреса |

|

|

|

|

|

Адрес ячейки |

|

(13) |

|

|

|

A0 |

RAM |

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIO0 |

(8) |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

A0..A12 |

|

|

|

... |

|

|

|

||||||||||||||

|

|

A0..A15 |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

... |

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A12 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIO7 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A13..A15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Адрес |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WE / RD |

|

|

|

|

|||||

|

|

|

|

|

|

микросхемы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD2 |

|

(3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RAM |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A0 |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIO0 |

(8) |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

... |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

DC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

... |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS _ M0 |

|

|

|

|

A12 |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

A0 |

0 |

|

|

|

|

|

|

DIO7 |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

... |

|

|

|

|

|

CS _ M1 |

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

A2 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

CS |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

... |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

MRD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WE / RD |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

& |

|

CS _ M7 |

MWR |

E |

7 |

|

|

Шина данных |

|

|

|

|

|

DD7 |

||

|

|

|

|

|

|

|

|

|

|

RAM |

|||||

Дешифратор |

|

A0 |

|||||

выбираемой |

|

|

|

DIO0 (8) |

|||

микросхемы |

|

|

|

... |

|||

|

|

|

|||||

|

|

|

... |

|

|

||

|

A12 |

|

|

||||

|

|

|

|

DIO7 |

|||

|

|

|

|

|

|||

CS

CS

WE / RD

WE / RD

D0..D7

Рис. 3.13. Схема 64-Кбайтного модуля SRAM.

Динамические оперативные запоминающие устройства

В динамических запоминающих устройствах DRAM данные хранятся в виде зарядов конденсаторов, на которых построены запоминающие элементы. Такой элемент значительно проще триггерного, применяемого в SRAM и содержащего 4 или 6 транзисторов. Это позволяет разместить в кристалле

59

DRAM много больше запоминающих элементов (примерно в 4-5 раз) и обеспечить максимальную информационную ѐмкость. В то же время, следствие необходимости регенерации усложняется управление памятью и уменьшается еѐ быстродействие. Последнее также есть следствие задержек на заряд конденсатора при записи в него информации.

Область применения динамических запоминающих устройств – основная память обычных компьютеров, где требуется наибольший объѐм, не обязательно самое высокое быстродействие и желательна экономичность в затратах.

Режимы работы и основные параметры

Динамические ОЗУ предусматривает четыре режима работы: чтение хранимой информации; запись новой информации;

хранение информации при отсутствии обращения; регенерации хранимой информации.

Основные параметры отечественных DRAM: информационная ѐмкость – до 128 Кбайт; время доступа – 150 нс.

Основные параметры зарубежных DRAM: информационная ѐмкость – до 256 Мбайт; время доступа – 7-15 нс.

Особенности структуры и логики управления DRAM

Запоминающие элементы динамического ОЗУ (рис. 3.17) построены на основе конденсаторов C и транзисторных ключей T. Запоминающие элементы сгруппированы в матрицу, находясь на пересечении строк и столбцов. Общим для всех элементов столбца является усилитель-регенератор УР.

Хранение "1" или "0" определяется наличием или отсутствием заряда конденсатора C. Когда выбрана строка, ключи всех конденсаторов строки коммутируют их со своими регенераторами. При этом регенератор воспринимает уровень напряжения конденсатора и формирует из него соответствующий логический сигнал ("0" или "1"). Затем регенератор выполняет восстановление информации:

если на конденсаторе была "1", то регенератор обеспечивает подзаряд конденсатора;

если на конденсаторе был обнаружен "0", то регенератор разряжает конденсатор.

Таким образом в данном варианте структуры при выборе строки выполняется регенерация всех ячеек выбранной строки.

Выполнять регенерацию ячеек динамической оперативной памяти требуется периодически, независимо от частоты обращения к ним. Для этого в микро-ЭВМ с динамическим ОЗУ предусматриваются специальные циклы регенерации. Они выполняются на фоне всех остальных действий микро-ЭВМ

60

периодически через интервалы в диапазоне от 1 до 15 мс, в зависимости от типа микросхемы. За время регенерации производится однократное сканирование строк динамического ОЗУ. Время регенерации зависит от двух факторов:

количества строк в матрице микросхемы NL; длительности цикла чтения tCY.

Например, типичная микросхема имеет следующие параметры: информационная ѐмкость – 1 Мбит; организация – 1 М × 1 бит;

длительность цикла чтения – tCY = 100 нс; период регенерации – 5 мс;

матрица квадратная 210× 210, NL = 1024. Тогда время требуемое для регенерации

rgn NL tCY |

1024 100 10 6 мс 0,1024 мс |

Значит для данной микросхемы из каждого дискретного интервала 5 мс его часть длительностью 0,1024 мс (2,048 %) должна будет тратится только на регенерацию.