- •В соответствии с этим все регистры микропроцессора можно разделить на

- •If (Interrupt Flag) - маски и приоритеты прерываний, а также условия реакции на прерывания;

- •Idt (Interrupt Descriptor Table) - таблица дескрипторов прерываний;

- •5. Режимы работы универсальных микропроцессоров

- •6. Режимы работы 32-разрядных процессоров фирмы Intel 32-разрядные микропроцессоры фирмы Intel имеют три основных режима функционирования (рис. 63):

- •Тема 4. Адресация данных в универсальных микропроцессорах

- •1. Способы адресации операндов

- •Базовая индексная адресация со смещением и масштабированием.

- •Тема 5. Средства управления памятью в универсальных микропроцессорах

If (Interrupt Flag) - маски и приоритеты прерываний, а также условия реакции на прерывания;

TF (Trace Flag) - флажок пошаговой трассировки, маска специального прерывания.

Регистр PSW включает также различные модификаторы команд, изменяющие реакцию МП на отдельные команды (например, флажок направления

DF).

Для обеспечения особых условий выполнения программ в PSW вводят специальный флажок, определяющий эти условия. Так, например, флажок H/U (Halt/User) служит для разрешения особых условий выполнения программ и реализации директив пультового терминала, а флажок U/S (User/System) используется для перевода микропроцессора из специального системного режима, в котором выполняются программы ОС, в пользовательский.

Упаковка всех флажков в одно слово (и соответственно хранение в одном регистре) дает возможность организовать их быструю запись в память с последующим восстановлением. В некоторых микропроцессорах поле кода условия, а также ряд других флажков (например, флажки, управляющие работой МП, и модификаторы команд) выделяются в отдельный регистр признаков (флагов) F.

В сложных микропроцессорах состав специальных регистров более широкий. В этих микропроцессорах имеются специальные регистры, используемые преимущественно ОС, - системные регистры. К системным регистрам относятся:

• управляющие регистры (разрешают защищенный режим, страничную организацию памяти, управляют работой с сопроцессором, задают

информацию для управления памятью, например, адреса системных таблиц, и т.п.);

отладочные регистры;

тестовые регистры.

Регистры данных. Наиболее типичным представителем регистров данных является аккумулятор A (Accumulator), который используется для временного хранения операндов и промежуточных результатов. С аккумулятором связано большинство команд арифметической и логической обработки. Ссылка на него, как правило, производится неявно с помощью кода операции. В состав микропроцессора может входить один или несколько аккумуляторов.

Влияние аккумулятора на организацию микропроцессора настолько велико, что процессоры с аккумулятором выделены в отдельный класс.

Другим примером регистров данных являются рабочие регистры. В отличие от аккумулятора они адресуются явно и могут рассматриваться как сверхскоростное регистровое ОЗУ данных. Рабочие регистры могут совмещать свою функцию хранения данных с функцией их адресации. В этом случае они приобретают функции регистров общего назначения (РОН).

Как аккумуляторы, так и РОН могут при необходимости объединяться в регистровые пары.

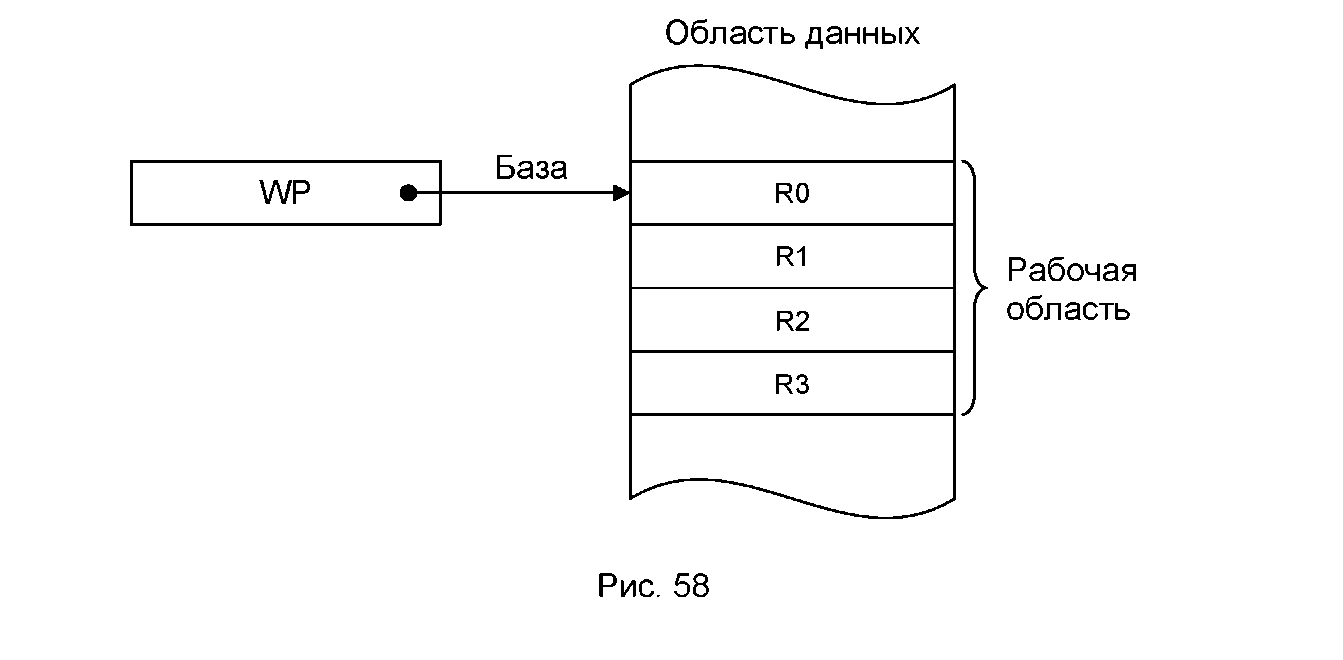

Микропроцессор может содержать несколько (например, два или четыре) наборов рабочих регистров. При этом один из них используется для системных целей или обработки прерываний, в все остальные - для прикладных программ пользователя. В каждый момент времени доступен только один набор рабочих регистров, выбираемый специальным регистром - указателем рабочего набора WP (Work Pointer). Переключение доступного рабочего набора связано с перезагрузкой малоразрядного указателя WP.

Расширение разрядности указателя WP до полного размера адресного регистра и отображение набора рабочих регистров на основную память данных с базой в WP приводит к типовой архитектуре с рабочими областями (рис. 58). Однако при этом теряется быстрый доступ к данным, хранящимся в рабочих регистрах. Решение этой проблемы связано с реализацией части основной памяти данных на одном кристалле с микропроцессором и размещением рабочей области в этой внутренней части ОЗУ.

Передача функции аккумулятора вершине стека TOS приводит к стековым архитектурам. Стековая организация дает возможность строить безадресные системы, в которых команды имеют наименьшую длину. Безадресные команды стековой архитектуры оперируют операндами, находящимися на вершине стека и непосредственно под ней. При выполнении операций операнды извлекаются из стека, а результат передается на вершину TOS. Стековая архитектура обладает высокой вычислительной эффективностью. Однако в классической форме она практического распространения не нашла. Это объясняется тем, что стек обычно размещается в основной памяти, доступ к которой требует отдельного цикла обращения к системной магистрали. Для уменьшения времени доступа к стеку он должен быть физически приближен к АЛУ за счет реализации на одном кристалле с процессором внутренней памяти данных и размещения в ней стека.

Более эффективным решением является введение в состав микропроцессора специального стека, который размещается в его регистровой области и используется исключительно для промежуточного хранения данных. Такой стек обладает быстрым доступом и называется вычислительным. Глубина вычислительного стека невелика - обычно она составляет 3-8 машинных слова. Прямой доступ к содержимому указателя вершины вычислительного стека, как правило, отсутствует. Манипуляция содержимым указателя выполняется только через запись/чтение данных из стека.

4. Регистры 32-разрядных процессоров фирмы Intel

Регистры 32-разрядных МП фирмы Intel подразделяются на следующие группы:

1. Основные функциональные регистры:

регистры общего назначения EAX, EDX, ECX, EBX, EBP, ESI, EDI, ESP;

указатель команд EIP;

регистр флагов EFLAGS;

сегментные регистры CS, SS, DS, ES, FS, GS.

Регистры блока обработки чисел с плавающей точкой (регистры FPU):

регистры данных R7-R0 (ST7-ST0);

регистр тегов TW;

регистр состояния FPSR;

регистр управления FPCR;

регистры-указатели команды и операнда FIP, FDP.

Регистры блока обработки пакетов чисел с плавающей точкой (регистры

SSE):

регистры пакетов данных XMM7-XMM0;

регистр управления-состояния MXCSR.

Системные регистры:

системные адресные регистры GDTR, LDTR, IDTR, TR;

управляющие регистры CR4-CR0;

регистры отладки DR7-DR0;

регистры тестирования TR7-TR3.

Служебные или модельно-специфические регистры.

Регистры трех первых групп используются при выполнении прикладных программ, регистры четвертой группы - при выполнении системных программ и отладке, регистры пятой группы - при тестировании микропроцессора и контроле эффективности выполнения программ. Системные и служебные регистры доступны только программам с высшим уровнем привилегий 0.

Основные функциональные регистры. Эти регистры относятся к видимой для прикладных программ части архитектуры процессоров и представляют собой расширение набора регистров 16-разрядных процессоров 8086/8088 и 80286.

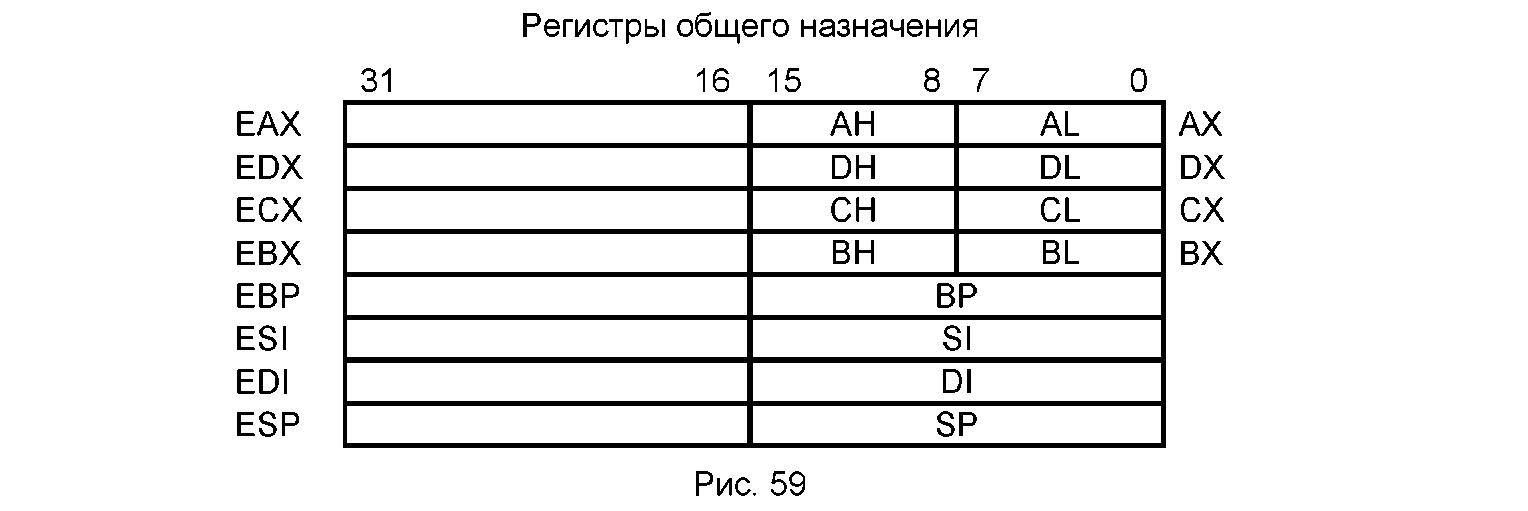

Восемь 32-разрядных регистров общего назначения (рис. 59) EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP предназначены для хранения данных и адресов. Младшие 16 разрядов этих регистров доступны под именами AX, BX, CX, DX, SI, DI, BP, SP, т. е. в 32-разрядных процессорах регистры базовой архитектуры расширены до 32 бит и к прежнему обозначению их имен добавилась приставка Е (Extended -расширенный). При операциях с байтами можно отдельно обращаться к младшему (разряды 7-0) или старшему (разряды 15-8) байту регистров AX, BX, CX, DX: младшие байты имеют имена AL, BL, CL, DL, старшие - AH, BH, CH, DH.

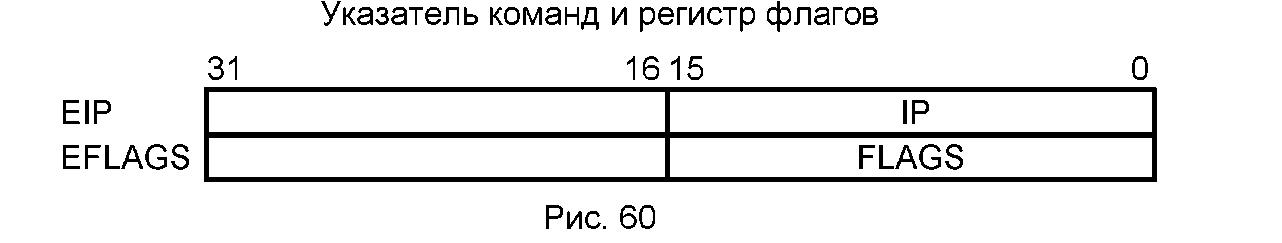

Указатель команд (рис. 60) EIP представляет собой 32-разрядный регистр, содержимое которого используется в качестве смещения при определении адреса следующей выполняемой команды. Смещение задается относительно базового адреса сегмента команд, задаваемого регистром CS. Младшие 16 бит EIP (биты 150) содержат 16-разрядный указатель команд с именем IP, который используется при 16-разрядной адресации. Содержимое EIP (IP) изменяется при выполнении команд передачи управления и прерываний.

Регистр флагов EFLAGS (рис. 60) содержит ряд битов, которые имеют различное назначение: признаки состояния CF, PF, AF, ZF, SF, OF указывают определенные характеристики результата, полученного при выполнении команды; управляющий признак DF определяет порядок адресации операндов при выполнении последовательности строковых команд; системные признаки TF, IF, IOPL, NT, RF, VM, AC, VIF, VIP, ID задают режим процессора при обслуживании исключений и прерываний, организации ввода-вывода данных и реализации ряда других процедур. Младшие шестнадцать бит регистра EFLAGS (биты 15-0) представляют 16-разрядный регистр флагов FLAGS, который используется при выполнении программ, написанных для микропроцессоров 8086, 80286. Рассмотрим назначение некоторых основных дополнительных разрядов регистра EFLAGS.

IOPL - уровень привилегий ввода/вывода. Задает максимальную величину уровня привилегий текущей программы, при котором разрешается выполнение команд ввода/вывода.

VM - признак режима виртуального 8086. Установка значения VM=1 вызывает переключение процессора в V86, при котором эмулируются возможности микропроцессора 8086.

AC - признак контроля выравнивания. Установка значения AC=1 вводит контроль выравнивания операндов при обращении к памяти. В этом случае при обращении к операнду, который не выровнен по соответствующей границе (2, 4, 8 байт), реализуется исключение типа #AC (ошибка выравнивания).

ID - признак допустимости идентификации. Возможность программного изменения значения ID указывает, что для данного процессора обеспечивается выполнение команды идентификации CPUID.

С егментные

регистры (рис.

61) CS,

SS,

DS,

ES,

FS,

GS

содержат 16-разрядные значения указателей

(в реальном режиме) или селекторов

сегментов (в защищенном режиме),

определяющих адресуемый сегмент памяти.

В реальном режиме содержимое этих

регистров непосредственно задает

значение базового адреса соответствующего

сегмента. В защищенном режиме содержимое

этих регистров задает выбор дескриптора,

который содержит базовый адрес, размер

и атрибуты сегмента. Соответствующий

дескриптор выбирается из таблицы,

хранящейся в основной памяти, и размещается

в программно-недоступном (теневом)

регистре дескриптора сегмента. С каждым

из шести сегментных регистров связаны

программно-недоступные скрытые регистры

дескрипторов (их еще называют Segment

Descriptor

Cache

- кэш сегментных регистров), автоматически

загружаемые при загрузке соответствующих

сегментных регистров. В защищенном

режиме в регистры дескрипторов из

таблицы дескрипторов загружается

32-битный базовый адрес, 32-битный лимит

(размер сегмента) и атрибуты сегментов.

По содержимому этих скрытых регистров

при каждом обращении к памяти выполняется

вычисление линейного адреса и проверка

защиты, причем именно эти регистры

задают свойства сегментов как в

защищенном, так и в реальном режимах.

егментные

регистры (рис.

61) CS,

SS,

DS,

ES,

FS,

GS

содержат 16-разрядные значения указателей

(в реальном режиме) или селекторов

сегментов (в защищенном режиме),

определяющих адресуемый сегмент памяти.

В реальном режиме содержимое этих

регистров непосредственно задает

значение базового адреса соответствующего

сегмента. В защищенном режиме содержимое

этих регистров задает выбор дескриптора,

который содержит базовый адрес, размер

и атрибуты сегмента. Соответствующий

дескриптор выбирается из таблицы,

хранящейся в основной памяти, и размещается

в программно-недоступном (теневом)

регистре дескриптора сегмента. С каждым

из шести сегментных регистров связаны

программно-недоступные скрытые регистры

дескрипторов (их еще называют Segment

Descriptor

Cache

- кэш сегментных регистров), автоматически

загружаемые при загрузке соответствующих

сегментных регистров. В защищенном

режиме в регистры дескрипторов из

таблицы дескрипторов загружается

32-битный базовый адрес, 32-битный лимит

(размер сегмента) и атрибуты сегментов.

По содержимому этих скрытых регистров

при каждом обращении к памяти выполняется

вычисление линейного адреса и проверка

защиты, причем именно эти регистры

задают свойства сегментов как в

защищенном, так и в реальном режимах.

Селектор в регистре CS обеспечивает обращение к сегменту команд, селектор в SS - к сегменту стека, селекторы в DS, ES,FS,GS — к сегментам данных.

Системные регистры. Кроме регистров общего назначения, предназначенных для использования прикладными программами, процессоры имеют ряд регистров системного назначения. Этих регистров в процессорах 8086 не было, а в процессоре 80286 присутствовала лишь часть из них и не в полном объеме. Эти регистры доступны только в защищенном режиме для программ,

имеющих максимальный уровень привилегий 0. Для доступа к системным регистрам используются специальные команды пересылки данных.

Управляющие регистры (Control Registers) CR0, CR2, CR3, CR4 хранят признаки состояния процессора, общие для всех задач. Регистр CR1 в существующих 32-разрядных процессорах не используется (зарезервирован для последующих моделей).

Регистр CR0 обеспечивает общее управление режимами работы процессора. Рассмотрим назначение некоторых основных разрядов регистра CR0.

РЕ (Protection Enable) - разрешение защиты. Установка значения разряда РЕ=1 переводит процессор в защищенный режим. Разряд РЕ совместно с битом PG определяет режим работы процессора (табл. 2).

PG (Paging Enable) - включение механизма страничной адресации памяти. При установке значения PG=1 обеспечивает страничную адресацию памяти в защищенном режиме.

Таблица 2 |

||

PG |

PE |

Режим процессора |

0 |

0 |

Реальный режим |

0 |

1 |

Защищенный режим без использования страничной адресации |

1 |

0 |

Запрещенная комбинация (вызывает исключение типа #GP -нарушение защиты) |

1 |

1 |

Защищенный режим с использованием страничной адресации |

ЕМ (Processor Extension Emulated) - эмуляция FPU. Установка значения ЕМ=0 указывает на присутствие в системе блока FPU. Установка значения ЕМ=1 вызывает при выборке команды FPU исключение типа #NM (отсутствие FPU), обеспечивающее обращение к подпрограмме, эмулирующей работу FPU.

AM (Alignment Mask) - разрешение контроля выравнивания. Контроль выравнивания выполняется только на уровне привилегий 3 при АМ=1 и установленном разряде АС=1 в регистре EFLAGS.

Регистр CR0 для совместимости с защищенным режимом микропроцессора 80286 является расширением 16-разрядного регистра MSW (Machine State Word -слово состояния машины) этого процессора, в котором были определены лишь биты РЕ, МР , ЕМ и TS. Команды загрузки и сохранения LMSW, SMSW для совместимости с микропроцессором 80286 работают только с этими четырьмя разрядами регистра CR0. Для загрузки или сохранения всего содержимого регистра CR0, используются MOV CR0, r/m или MOV r/m, CR0, выполняемые программами, имеющими максимальный уровень привилегии 0.

Регистр CR2 (Page Fault Linear Address) содержит 32-разрядный линейный базовый адрес страницы, при обращении к которой зафиксирована ошибка при страничной адресации.

Регистр CR3 (Page Directory Base Register) содержит 20 старших разрядов физического базового адреса таблицы каталога страниц, а также разряды, управляющие загрузкой страниц в кэш-память данных.

Регистр CR4 содержит разряды разрешения архитектурных расширений функциональных возможностей, реализуемых в процессорах Pentium и выше. Рассмотрим назначение некоторых основных разрядов регистра CR4.

DE (Debugging Extensions) - расширение возможностей отладки (разрешение точек останова на инструкциях обращения к заданным портам ввода/вывода).

PSE (Page Size Extension) - расширение размера страницы (4 Кбайт и 4 Мбайт).

РАЕ (Physical Address Extension) - расширение физического адреса (страницы 4 Кбайт и 2 Мбайт, 36-разрядная адресация).

OSXMMEXCPT - флаг поддержки операционной системой исключений от блока ХММ (SIMD-инструкций с плавающей точкой - расширение набора команд SSE и SSE2 процессоров P6 и Pentium 4).

Системные адресные регистры (рис. 62) служат для обращения к таблицам и системным сегментам, с помощью которых осуществляется адресация памяти в защищенном режиме:

• GDT (Global Descriptor Table) - глобальная дескрипторная таблица (таблица дескрипторов);