Сумматор

Комбинационные сумматоры

Особенностью комбинационных сумматоров является то что они выполнены на логических схемах, не обладают свойствами накапливания суммы, все комбинационные сумматоры последовательного действия и позволяют складывать числа без учета переноса.

M S |

S

P |

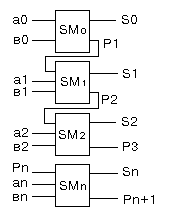

Сумматор может быть построен как комбинационная схема -

последовательный сумматор и как

последовательностная схема -

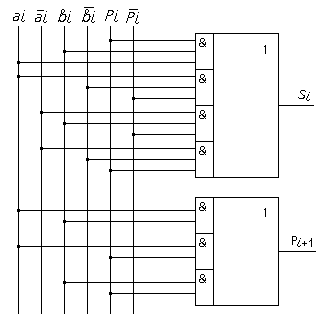

накапливающий сумматор. Сумматор осуществляет cуммирование цифр разрядов слагаемых и цифр переноса по правилам сложения по модулю 2. Работа сумматора строго регламентирована в соответствии с таблицей:

-

ai

bi

Pi

Si

Pi+1

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

6. Последовательный сумматор

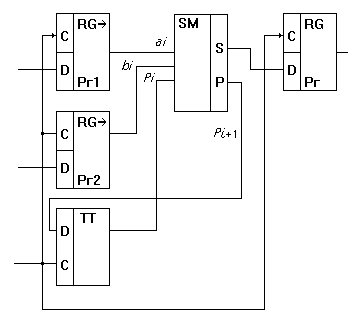

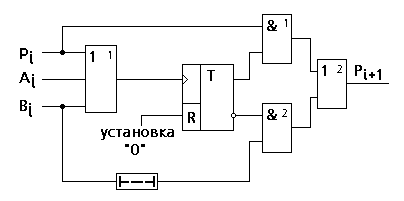

Накапливающий сумматор

Накапливающий сумматор является автоматом с памятью, т.е. слагаемые могут приходить поочередно в произвольные моменты времени и запоминаться в линиях задержки или в триггерах. Накапливающий. сумматор применяется в асинхронных устройствах, в которых слагаемые не привязаны к тактам тактового генератора.

одновременно bi опрокидывает триггер в "0". На инверсном выходе триггера устанавливается "1", следовательно на вторую схему "И" подаются две единицы, следовательно на выходе второй схемы "ИЛИ" формируется цифра переноса в старший разряд, равная "1". Если Pi=0, то цифра суммы, которая снимается с прямого выхода триггера, равна "0". Если Pi=1, то сумма Si=1.

-

ai

bi

Pi

Si

Pi+1

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1