- •Базовая организация персонального компьютера Содержание

- •1. Многоуровневая организация и эволюция эвм

- •Уровни архитектуры эвм

- •2. Архитектурные принципы Фон-Неймана

- •Выполнение команд по программе, хранимой в эвм

- •3. Процессор. Основные компоненты и их назначение

- •4. Оперативная память (общая характеристика)

- •6. Типовая структура машинной команды

2. Архитектурные принципы Фон-Неймана

В каждой области науки и техники существуют

некоторые фундаментальные

идеи или принципы.

В компьютерной науке роль таких

фундаментальных идей сыграли принципы,

сформулированные независимо друг от

друга - американским математиком и

физиком Джоном

фон Нейманом

(1903-1957) и советским ученым Сергеем

Лебедевым

(1902-1974).

каждой области науки и техники существуют

некоторые фундаментальные

идеи или принципы.

В компьютерной науке роль таких

фундаментальных идей сыграли принципы,

сформулированные независимо друг от

друга - американским математиком и

физиком Джоном

фон Нейманом

(1903-1957) и советским ученым Сергеем

Лебедевым

(1902-1974).

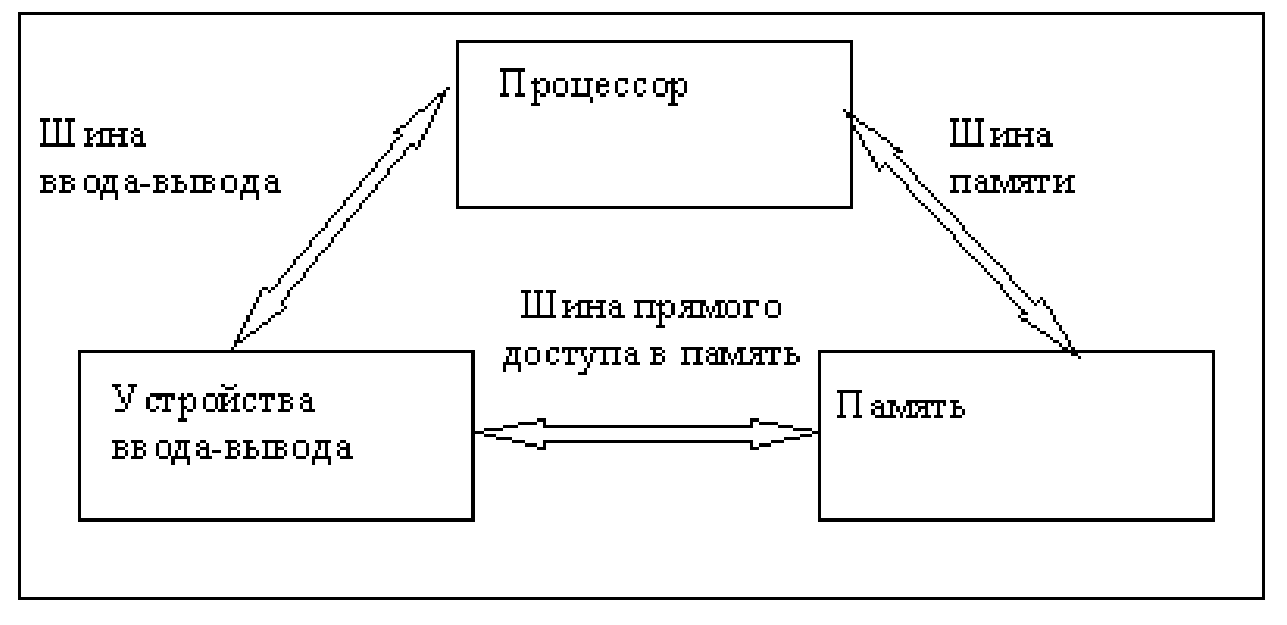

Сущность "Неймановских принципов" в следующем (Рис. 4):

Рис. 4 Структурная схема типовой ЭВМ

Компьютер включает связанные между собой Процессор (арифметичес-кое устройство и устройство управ-ления), Память и Устройства ввода-вывода.Компьютеры на электронных элементах должны работать не в десятичной, а в двоичной системе счисления.

Программа, так же как и числа, с которыми оперирует компьютер, записываются в двоичном коде, то есть по форме представления команды и числа однотипны.

Программа должна размещаться в одном из блоков компьютера - в запоминающем устройстве (ЗУ), которое имеет произвольный доступ.

Трудности физической реализации ЗУ большого быстродействия, энергонезависимого и большой емкости требуют иерархической организации. Программа выполняется из основной памяти, а сохраняется в энергонеза-висимой вторичной памяти (в файл).

Файл - идентификационная совокупность экземпляров описанного в программе типа данных, находящихся вне программы во внешней памяти и доступных программе посредством специальных операций.

Арифметико-логическое устройство (АЛУ) компьютера конструируется на основе схем, выполняющих операцию сложения, сдвига, логическую операцию. Помимо результата операции, АЛУ формирует ряд признаков результата (флагов), которые могут анализироваться при выполнении команд условной передачи управления.

7. В компьютере используется параллельный принцип организации вычислительного процесса (операции над двоичными кодами осуществляются одновременно над всеми разрядами).

Централизованное последовательное управление при выполнении команд. Т.о. нет конвейера, параллельности, внеочередного выполнения и прочего, что свойственно современным процессорам.

Линейная структура адресации памяти.

10.Низкий уровень машинного языка. Нет микропрограммируемости.

Выполнение команд по программе, хранимой в эвм

Программа - последовательность команд, хранимых в памяти компьютера.

● Команды в ЭВМ (в машине фон Неймана) располагаются в ячейках программной памяти подряд, одна за другой.

● Процессор по порядку считывает команды из памяти и выполняет их.

Этот процесс сводится к последовательному выполнению этапов:

считывание команды из ОП - Read,

дешифрация команды- Decoding,

обращение к памяти за операндом- Memory Access,

выборка операнда- Operand Fetch,

исполнение операции- Execution,

запись результата в память - Record.

● Операнд/результат могут быть взяты/записаны в устройства ввода-вывода.

●Следующая команда выполняется после завершения предыдущей команды. Ее адрес содержится в особом регистре процессора, называемом указателем (или счетчиком) команд. После считывания очередной команды процессор автоматически увеличивает содержимое счетчика команд, так, что он указывает на очередную команду.

► Известны альтернативные пути построения компьютера:

Потоковая машина - действиями управляют сами данные.

Нейронные сети и др.

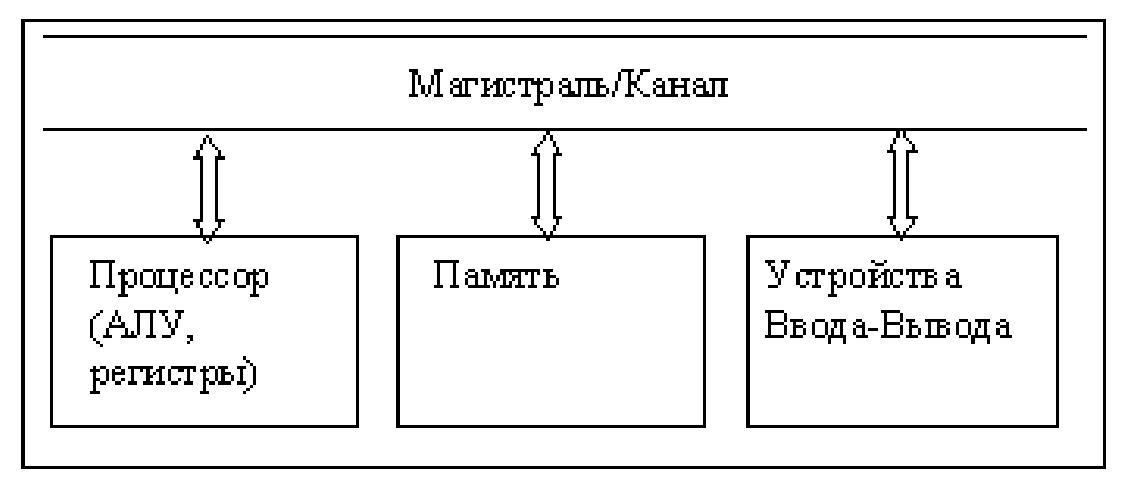

Рис

5 Структурная

схема ЭВМ с общей шиной

агистральная

вычислительная структура

агистральная

вычислительная структура

Принципы фон Неймана применимы к магистральной (шинной) архитектуре (Рис. 5). В этом случае ЭВМ включает четвертый элемент - магистраль, которая связывает отдельные элементы и влияет на выполнение команд.

Магистраль/канал - унифицированная подсистема связи структурных частей ЭВМ. Унификация в том, что все устройства подключаются к магистрали одинаково (набор сигналов, алгоритм обмена). Унификация позволяет легко заменять, добавлять или удалять отдельные части, входящие в состав ЭВМ, без нарушения ее работоспособности. Основные конструктивные компоненты магистрали - линии связи (провода), которые можно подразделить на три группы (шины) - адреса, данных и управления.

Линии связи - провод, по которому передается логический сигнал.

Шина - группа линий однотипных сигналов.

▪ Шина адреса предназначена для передачи из процессора в память параллельным кодом двоичного слова, представляющего собой начальный адрес участка памяти, к которому требуется обращение.

Количество линий (ширина шины адреса) определяет размер физического адресного пространства, т.е. максимальное количество различных адресов в ОЗУ. Адрес по шине передается от процессора в память или во внешнее устройство. В процессор адрес передается только в мультипроцессорных системах, для поддержания правильной работы кэшей.

▪ Шина данных предназначена для передачи команд и данных между процессором, памятью и периферийными устройствами. Передача слов осуществляется также параллельным кодом, а "ширина" шины данных в реальных системах может составлять от 1 до 4 и более байтов. Шина данных является двунаправленной и имеет наибольшую пропускную способность.

В некоторых ЭВМ шина адреса и шина данных объединены в одну мультиплексируемую шину адреса/данных.

Такая шина функционирует в режиме разделения времени:

цикл шины разбит на временной интервал передачи адреса и на интервал передачи данных.

Мультиплексирование позволяет сократить общее число линий, но требует усложнения логики связи с шиной. Кроме того, оно может привести к потере производительности.

▪ Шина управления предназначена для передачи управляющих сигналов из процессора в прочие устройства, подключенные к магистрали.

Любое устройство, подключенное к магистрали, должно быть способно:

1) распознать "свой адрес", формируемый процессором на адресной шине;

2) распознать по сигналам на шине управления действие, которого ждет от устройства процессор;

3) выполнить это действие: передать в процессор либо принять из него через шину данных двоичное слово.

Последовательность этих трех шагов составляет "цикл магистрали" ("канальный цикл"). Циклы могут следовать непрерывно, либо с интервалами. Они происходят под управлением процессора или внешних устройств, и обеспечивают обмен информацией между частями ЭВМ.

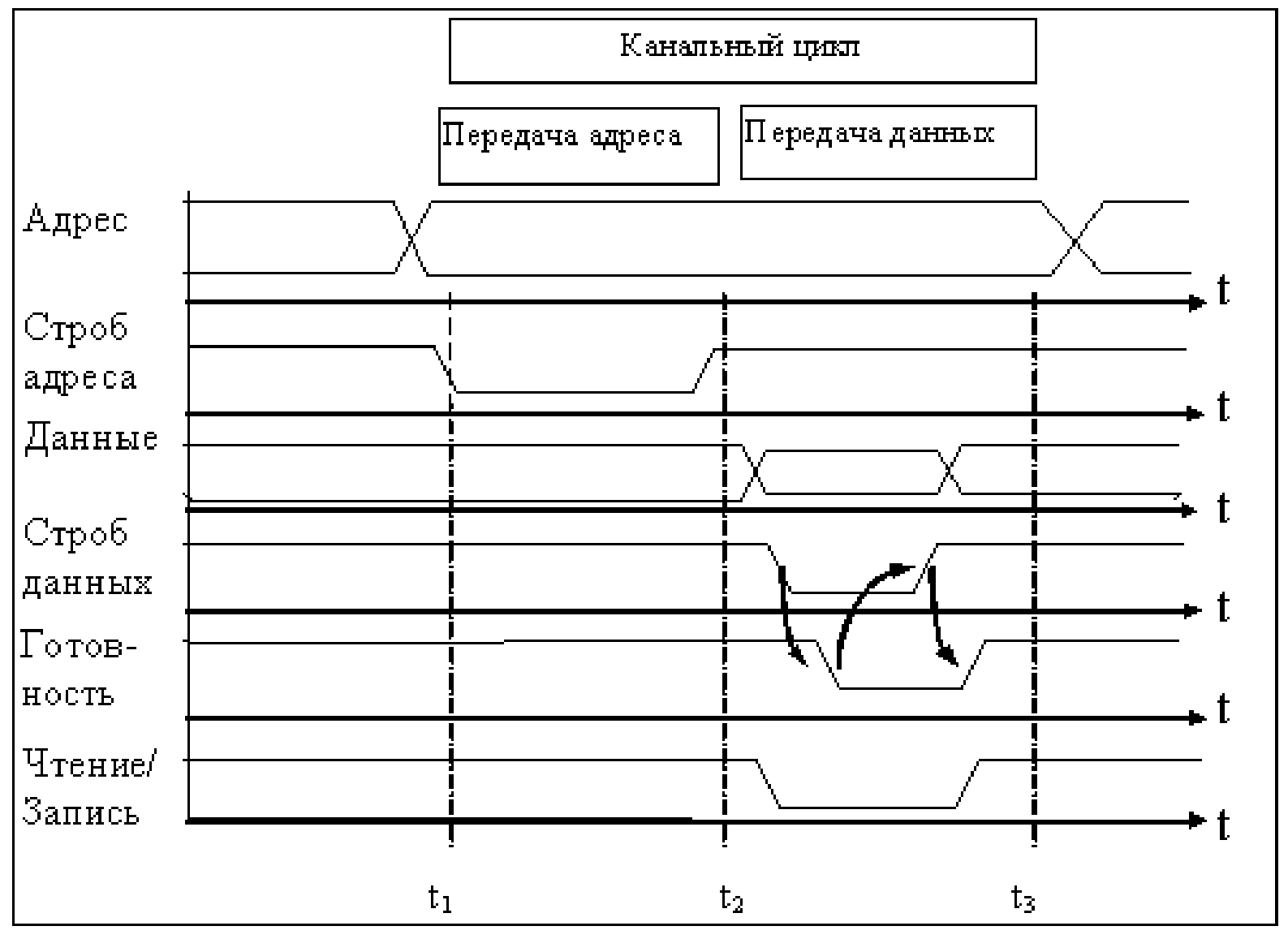

К

К анальный

цикл обмена данными

Временная

диаграмма канального цикла обмена

данными - на Рис

6.

В ней можно выделить два

этапа:

анальный

цикл обмена данными

Временная

диаграмма канального цикла обмена

данными - на Рис

6.

В ней можно выделить два

этапа:

(1)

передачи/ декодирования адреса - фазу

адреса

(задается положением во времени строба

адреса) и

(1)

передачи/ декодирования адреса - фазу

адреса

(задается положением во времени строба

адреса) и

Рис.6.

Типовая

временная диаграмма канального цикла

для раздельных шин адреса и данных

В приведенном примере:

1) шины адреса и данных - раздельные,

2) адрес передается синхронно,

Синхронный канал - время канального цикла постоянно, адрес/данные записываются синхронно со стробом. Обычно переключение сигналов шины происходит по импульсам тактовой частоты.

3) передача данных производится асинхронно - длительность этапа передачи данных определяется задержкой снятия сигнала Готовности.

А синхронный канал - время канального цикла зависит от приемного устройства, которое после записи данных вырабатывает сигнал Готовности.

Арбитраж шин. При любой передаче по шине всегда имеется инициатор передачи (ведущее устройство) и приемник данных (ведомое устройство). Ведущее устройство захватывает шину и начинает формировать временную диаграмму ее работы.

Если несколько устройств претендуют на права ведущего, то должен быть механизм выбора одного из них (арбитраж шин). Арбитраж построен на основе нескольких положений:

Каждому из претендентов на шину присваивается определенный уровень приоритета, который может оставаться неизменным (статический приоритет) или изменяться по какому-то алгоритму (динамический приоритет). Шина отдается устройству с наивысшим приоритетом.

Может использоваться централизованная схема арбитража или децентрализованная. Центральный арбитр, находящийся, например, в контроллере шины, принимает запросы параллельно или последовательно от устройств и решает задачу предоставления шины. В децентрализованной схеме каждый ведущий может иметь контроллер шины и самостоятельно принимать решение о ее захвате.

• Ограничение времени управления шиной. Вне зависимости от модели арбитража должно быть предусмотрено ограничение времени управления шиной. Например, алгоритм фиксированного кванта времени, который отводится каждому ведущему для захвата шины.