- •Предисловие

- •Глава 1

- •1.1. Средства микропроцессорной вычислительной техники

- •1.2. Основные характеристики, место и классификация микроЭвм

- •1.3. Индустрия микропроцессорных средств вт

- •Глава 2 элементная база микроэвм. Микропроцессоры

- •2.1. Микропроцессорные бис

- •2.2. Микропроцессор 8086

- •2.3. Развитие семейства мп 8086

- •Глава 3 элементная база микроэвм. Микропроцессорные семейства бис

- •3.1. Сопроцессоры

- •3.2 Интегральные микросхемы памяти

- •3.3. Интерфейсные схемы, контроллеры

- •3.4. Схемы обрамления

- •Глава 4 магистрально-модульная организация микроэвм

- •4.1. Интерфейсы и магистрали микроЭвм

- •4.2. Магистрали типа Multibus

- •4.3. Интерфейсы периферийного оборудования

- •4.4. Конструктивные особенности микроЭвм

- •Глава 5 аппаратура микроэвм

- •5.1. Периферия микроЭвм

- •5.2. Аппаратура персональных микроЭвм

- •5.3. Модульные системы и одноплатные микроЭвм

- •Глава 6

- •6.1. Операционные системы

- •6.2. Средства автоматизации программирования

- •6.3. Пакеты прикладных программ

- •1. Монография я учебные издания

- •2. Периодические издания

- •3. Фирменные издания

- •Глава 1. Введение в микропроцессорную технику .............................. 5

- •Глава 2. Элементная база микроЭвм. Микропроцессоры ...................... 18

- •Глава 3. Элементная база микроЭвм. Микропроцессорные семейства бис ............................................................................................................................ 81

- •Глава 4. Магистрально-модульная организация микроЭвм ……………108

- •Глава 5. Аппаратура микроЭвм ............. ……………………………….148

- •Глава 6. Программное обеспечение микроЭвм ........................................187

3.2 Интегральные микросхемы памяти

Характеристики и широкие возможности современных микроЭВМ во многом определяются достижениями микроэлектроники в создании больших интегральных микросхем запоминающих устройств (БИС ЗУ). Микросхемы памяти ориентированы на построение внутренних запоминающих устройств, которые должны обеспечить долговременное хранение информации и оперативное (соизмеримое по времени с циклом работы процессора) ее изменение и/или считывание. Классификация БИС ЗУ приведена на рис. 3.4. Возможности микросхем памяти определяются тремя группами характеристик: функциональными, схемотехническими и эксплуатационными. К первой группе относятся:

функциональное назначение — основное назначение микросхемы, например, для построения постоянных ЗУ, сверхоперативных ЗУ, оперативных ЗУ, видеопамяти для графических дисплеев;

информационная емкость (capacity) — максимальное количество хранимой в БИС информации (измеряется в битах, Кбит или Мбит);

организация БИС — разрядность информационного кода, который можно одновременно записать или считать из микросхемы. Например, БИС ЗУ емкостью 64 Кбит может иметь организацию 16К4 (4-разрядное слово) или 8К8 (8-разрядное слово);

время обращения (access time) — характеризует временные затраты на выполнение операций чтения/записи с БИС;

энергопотребление — электрическая мощность (или ток), которую БИС потребляет от источников питания. Обычно указывается энергопотребление в активном режиме (БИС выбрана и операции чтения/записи выполняются) и в режиме хранения (БИС не выбрана, чтение и запись невозможны).

Перечень схемотехнических и эксплуатационных характеристик интегральных схем памяти практически совпадает с соответствующими характеристиками микропроцессоров (параграф 2.1). Все БИС ЗУ, используемые в микропроцессорных вычислителях, строятся на базе nМОП или КМОП технологий (или их усовершенствованных модификаций) с обязательной совместимостью входных и выходных сигналов с ТТЛ уровнями.

Рассмотрим следующие запоминающие устройства.

Постоянные запоминающие устройства. Постоянные запоминающие устройства (ПЗУ, read only memory, ROM) предназначены для воспроизведения неизменяемой информации, заносимой в схему специальным образом. В ПЗУ, как правило, записываются системные программы широкого назначения, таблицы, которые необходимо постоянно хранить в памяти микроЭВМ. Важно, что при отключении электропитания информация в БИС ПЗУ сохраняется и становится доступной сразу после его включения. ПЗУ подразделяются на:

программируемые изготовителем (истинные) ПЗУ. Запись информации в такие элементы выполняется изготовителем схемы по заказу и спецификациям пользователя;

однократно программируемые ПЗУ (ППЗУ, programmable ROM — PROM). С помощью специального устройства (программатора) пользователь имеет возможность самостоятельно записать в БИС информацию. Изменить занесенные в ППЗУ коды невозможно;

перепрограммируемые (стираемые, репрограммируемые) ПЗУ (СППЗУ, РПЗУ, reprogrammable, erasable PROM — EPROM). Допускают стирание записанной информации и повторное ее занесение с помощью программаторов, стирание можно осуществить электрически (ЭСППЗУ, electrically erasable — EEPROM) или с помощью ультрафиолетовых лучей (УФ СППЗУ, ultraviolet erasable — UVEPROM).

Основные функциональные характеристики современных БИС ПЗУ приведены в табл. 3.2 (по материалам [2.8]). Следует отметить, что разработчики и производители микропроцессорных вычислительных систем в последние годы склоняются к предпочтительному использованию СППЗУ. Это вызвано невозможностью гарантировать стопроцентную безошибочную работу программного обеспечения, и, следовательно, к возможности выбросить массу заказных БИС ПЗУ или записанных БИС ППЗУ.

Рассмотрим 1 Мбит СППЗУ с электрическим стиранием и программированием типа Аm27С1024 фирмы Advanced Micro Devices [2.8]. Память организована в 64 К шестнадцатиразрядных слов, что полностью соответствует двум сегментам МП 8086. Микросхема выполнена по КМОП технологии на кристалле площадью 52 мм2 и размещается в пластмассовом корпусе типа DIP с 40 выводами. Упрощенная структура БИС показана на рис. 3.5. Основой ПЗУ является 16-разрядная матрица запоминающих элементов (каждый площадью 20,25 мкм2), состоящая из 128 столбцов и 512 строк. Полный 16-разрядный адрес A15 — А0 разделен на два поля: адрес столбца А6 —A0 и адрес строки A15—А7. С помощью дешифраторов строк и столбцов код, поступающий по адресным входам, определяет одно слово из 64 К возможных. Информационный код из ПЗУ выдается по двунаправленным линиям данных D15 —D0 с тремя состояниями.

Низкий активный уровень сигнала на входе выборки кристалла CS (chip select) включает буфер ввода-вывода данных и переводит схему в активное состояние. В этом режиме с задержкой 170 нc после установления адреса на входах А15—А0 на выходах D15—D0 формируется код, записанный в выбранную ячейку памяти. Для выполнения операции чтения не требуется никакой синхронизации. В активном режиме при работе с частотой 5 МГц БИС потребляет ток 50 мА и рассеивает мощность 50 мВт. В пассивном (невыбранном) режиме рассеиваемая мощность падает в 50 раз (ток питания 1 мА).

В режим программирования БИС переводится высоким уровнем сигнала на входе PR и подачей специального питающего напряжения величиной 10,5 В. В этом режиме линии данных настраиваются на прием записываемого кода. Длительность программирующего импульса на входе PR составляет 0,5 мс, что позволяет заполнить весь кристалл за 50 с. В СППЗУ легко размещается полный текст достаточно мощной операционной системы (ОС) со всеми программами поддержки. Включение такой ОС на кристалле в состав микроЭВМ резко снижает требования к емкости внешних запоминающих устройств и повышает производительность системы в целом.

Оперативные запоминающие устройства. Большие интегральные схемы для построения ОЗУ получили название схем запоминающих устройств с произвольной выборкой (ЗУПВ, random access memory — RAM). Они обеспечивают режимы записи, хранения и считывания информации. В работе полупроводниковых ЗУПВ есть две существенные особенности. При чтении информации она остается в БИС неизменной, т. е. допускается многократное считывание кода без его восстановления. Однако, если отключить электропитание, хранимые данные безвозвратно разрушаются. При подаче питания на ЗУПВ в его ячейках появляются случайные коды, не несущие никакой информации. Можно указать два основных вида БИС ЗУПВ:

статические ЗУПВ (static RAM), способные сохранять записанную информацию пока микросхема подключена к источнику питания;

динамические ЗУПВ (dynamic RAM — DRAM), время хранения информации в которых ограничено единицами миллисекунд, вследствие чего ее требуется периодически восстанавливать — регенерировать (refresh process). Это делается специальными встроенными или внешними схемами таким образом, чтобы процесс регенерации был, по возможности, «незаметен» для микропроцессора.

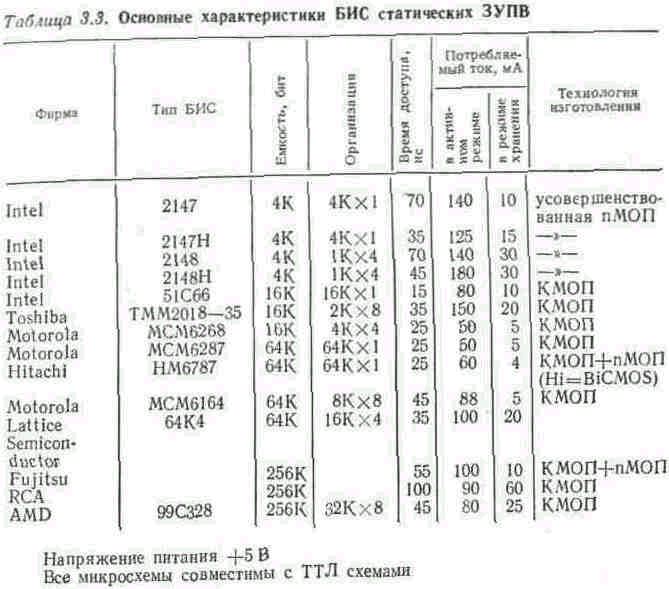

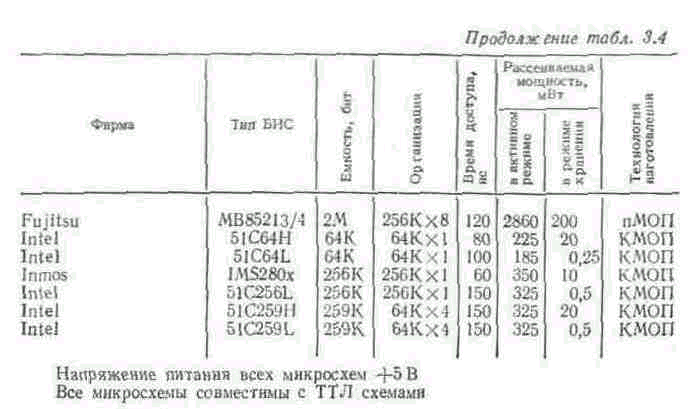

Типичные характеристики статических и динамических ЗУПВ приведены в табл. 3.3, 3.4, соответственно (по материалам [2.7, 2.8]). Сравнительный анализ таблиц показывает, что емкость динамических схем в среднем в четыре раза выше, чем статических. Однако они не выдерживают сопоставления по быстродействию (в 2—3 раза ниже) и по рассеиваемой мощности. Последнее особенно заметно для динамических ЗУПВ, выполненных по nМОП технологии. Резкое снижение цен на динамические БИС, вызванное конкурентной борьбой, прогресс в создании высококачественных статических элементов заставили ряд ведущих фирм (Intel, Mostek) отказаться от дальнейшей разработки динамических ЗУПВ. Другие производители (особенно японские) продолжают исследования в этой области. Так, компания Texas Instruments объявила о выпуске КМОП динамических ЗУПВ емкостью 4 Мбит со временем доступа 150 не (а в режиме статической дешифрации столбцов 30 нc) и площадью кристалла 8,9 мм2.

Несмотря

на указанные недостатки динамические

ЗУПВ остаются в настоящее время основной

элементной базой для построения ОЗУ в

микроЭВМ. В качестве примера рассмотрим

схему ДЗУПВ фирмы IBM,

ориентированную на микропроцессорные

применения. БИС емкостью 256 Кбит

с аппаратно настраиваемой организацией

(256К1,

128К2,

64К4)

выполнена по усовершенствованной

nМОП

технологии на кристалле площадью 50 мм2.

Микросхема питается напряжением 5 В,

в активном режиме рассеивает мощность

300 мВт, а в режиме хранения — 25 мВт,

полностью совместима по входу-выходу

с ТТЛ схемами. Структура прибора приведена

па рис. 3.6. Информация хранится в 16

запоминающих матрицах емкостью по

16 Кбит,

состоящих из 128 строк и 128 столбцов. В

микросхеме имеется четыре буфера

ввода-вывода, к которым подключено по

4 матрицы запоминающих элементов.

Информация поступает в схему или выдается

из нее по двунаправленным с тремя

состояниями линиям D3—D0.

Управляющие сигналы

![]() позволяют подключить буфер, и,

следовательно, 64 Кбит

памяти к соответствующей линии

данных. Тем самым можно устанавливать

разрядность слова памяти. Если

микросхема используется как память

256 К1,

то все линии данных объединяются, а

входы

,

используются для задания двух младших

разрядов адреса. Если необходима

организация 64 К4,

то входы

просто

заземляются.

позволяют подключить буфер, и,

следовательно, 64 Кбит

памяти к соответствующей линии

данных. Тем самым можно устанавливать

разрядность слова памяти. Если

микросхема используется как память

256 К1,

то все линии данных объединяются, а

входы

,

используются для задания двух младших

разрядов адреса. Если необходима

организация 64 К4,

то входы

просто

заземляются.

Шестнадцатиразрядный

адрес разбит на два поля. Восемь старших

разрядов задают адрес строки, а восемь

младших — столбца. При обращении к БИС

адрес строки и адрес столбца

мультиплексируются на линиях адреса

А7—А0,

а их прием стробируется сигналами

![]() (row

address

strobe)

и

(row

address

strobe)

и

![]() (column

address

strobe).

Выполнение операций записи и чтения

иллюстрируется рис. 3.7 (входы G3—G0

заземлены). Сначала на шину адреса

подается адрес строки, который принимается

в буфер БИС по спадающему фронту сигнала

RAS. Принятый адрес дешифрируется и

определяется одна из 128 строк во всех

верхних или нижних матрицах (на рис. 3.6

— верхние). Затем подается адрес столбца,

который фиксируется по спадающему

фронту

.

Дешифраторы столбцов выбирают один

из 128 столбцов в левых или правых матрицах

во всех четырех группах (на рисунке —

левых). Таким образом, в каждой группе

определяется уникальный бит, лежащий

на пересечении

выбранной

строки и столбца. Тип операции (чтение

или запись) задается сигналом

(column

address

strobe).

Выполнение операций записи и чтения

иллюстрируется рис. 3.7 (входы G3—G0

заземлены). Сначала на шину адреса

подается адрес строки, который принимается

в буфер БИС по спадающему фронту сигнала

RAS. Принятый адрес дешифрируется и

определяется одна из 128 строк во всех

верхних или нижних матрицах (на рис. 3.6

— верхние). Затем подается адрес столбца,

который фиксируется по спадающему

фронту

.

Дешифраторы столбцов выбирают один

из 128 столбцов в левых или правых матрицах

во всех четырех группах (на рисунке —

левых). Таким образом, в каждой группе

определяется уникальный бит, лежащий

на пересечении

выбранной

строки и столбца. Тип операции (чтение

или запись) задается сигналом

![]() .

.

При записи (см. рис. 3.7,а) низкий уровень сигнала W/R должен сопровождать появление на линиях данных кода для записи практически одновременно с адресом столбца. При чтении (см. рис. 3.7, б) сигнал должен быть высоким, по сигналу линии данных переходят из третьего состояния в активное, а затем на них формируется считанный из памяти код. Полный цикл чтения или записи требует не менее 150 нс. Возможен страничный режим, когда при фиксированном сигналом адресе строки последовательно или произвольно изменяется адрес столбца. Для чтения или записи в этом режиме доступно 2564 бит, причем время обращения снижается до 100 нс. Управляя сигналами , можно дополнительно расширить размер страницы до 1024 бит, снизив одновременно время обращения до 25 не.

Динамические элементы памяти в запоминающих матрицах гарантированно хранят информацию не более 4 мс. По истечении этого интервала необходимо перезаписать состояние всех 256 К элементов, для чего БИС переводится в режим регенерации по сигналу RF. Регенерация выполняется внешними схемами последовательным перебором всех 256 адресов строк. По спадающему фронту сигнала происходит чтение всей текущей строки во внутренние усилители, а затем автоматическая запись в те же элементы. Таким образом, за один цикл длительностью 100 нс регенерируется 1024 элемента памяти. Полная регенерация БИС занимает немногим более 25 мкс, что составляет 0,64 % рабочего интервала.

По оценке специалистов в ближайшие годы ожидается широкое внедрение в микропроцессорной аппаратуре динамических ЗУПВ, емкостью 1—4 Мбита и статических ЗУПВ, емкостью 256 — 512 Кбит.