- •Раздел 3 основы микропроцессорной техники

- •3.1 Структуры вычислительных систем

- •3.2 Принципы организации однокристальных микропроцессоров и микропроцессорных систем

- •3.3 Программирование микропроцессоров

- •При использовании прямой адресации

- •При использовании косвенной адресации

- •На языке Ассемблер

- •Ассемблер, содержащая подпрограмму

- •3.4 Принципы организации однокристальных микроконтроллеров

- •3.5 Программирование микроконтроллеров

- •3.6 Организация памяти микропроцессорных систем

- •3.7 Интерфейсные бис/ сбис

- •Информации

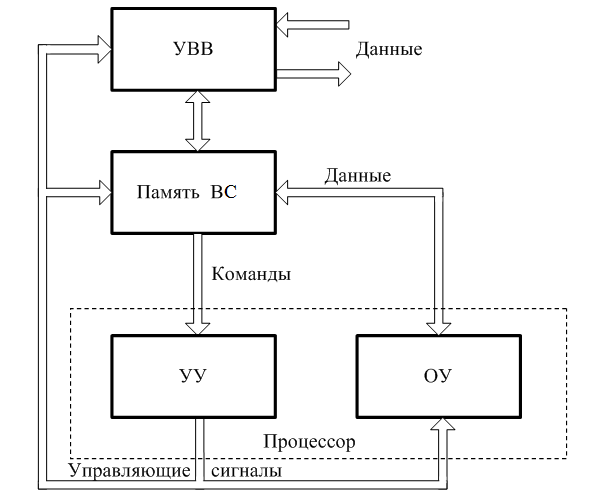

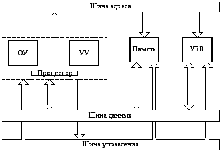

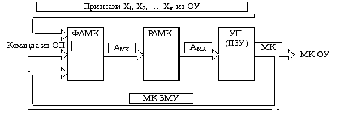

3.1 Структуры вычислительных систем

Рисунок 3.1 – Классическая структура вычислительной системы

Рисунок 3.2 – Магистральная структура вычислительной системы

Рисунок 3.3 – Упрощенная структура блока микропрограммного управления

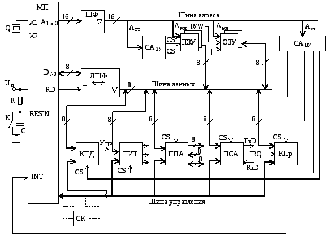

3.2 Принципы организации однокристальных микропроцессоров и микропроцессорных систем

Рисунок 3.4 – Типовая структурная схема МПС

Рисунок 3.5 – Мультиплексирование шины адреса/данных

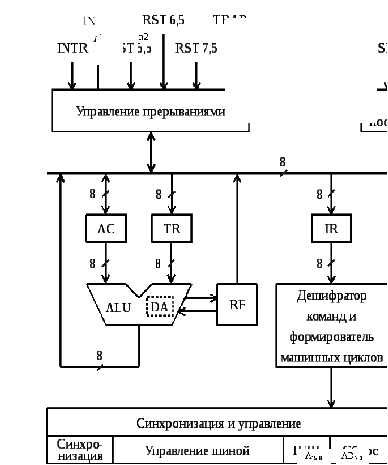

Рисунок 3.6 – Структура простого микропроцессора

Рисунок 3.7 – Структурная схема блока дешифрации команд и формирования машинных циклов

|

КЦ |

|

b1 |

N – 2 | |||||||||||||||||

|

М1 |

М2 |

М3 |

|

b2 |

N – 1 | |||||||||||||||

|

Т1 |

Т2 |

Т3 |

Т4 |

Т1 |

Т2 |

Т3 |

Т1 |

Т2 |

Т3 |

|

b3 |

N | ||||||||

|

а) |

|

б) |

| |||||||||||||||||

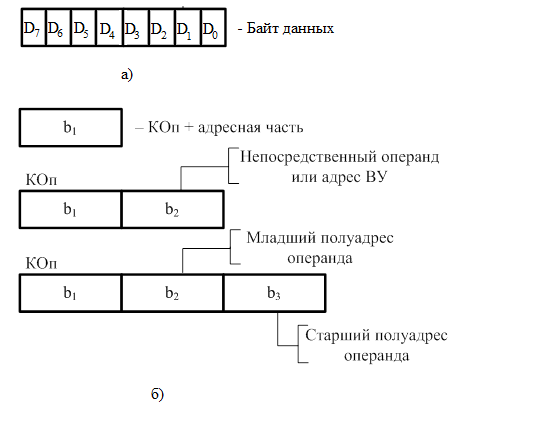

Рисунок 3.8 – Циклы и такты МП (а) и пример размещения команды в памяти МПС(б)

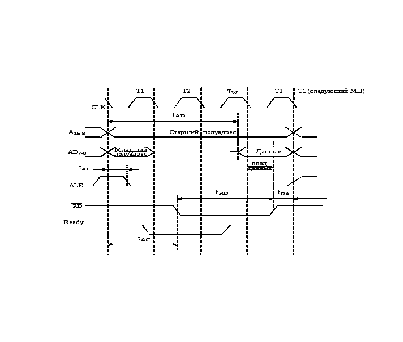

Рисунок 3.9 – Временные диаграммы цикла чтения МП

Рисунок 3.10 – Аппаратная реализация пересылки байта вектора прерывания при выполнении операции рестраRST

|

N-1 0 |

0000 h |

|

RG 0 | |

|

RG 1 |

0001 h |

|

RG 2 |

0002 h |

|

. . . |

. . . |

|

RG M-2 |

FFFE h |

|

RG M-1 |

FFFF h |

Рисунок 3.11 – Условное представление линейной организации памяти для 16-разрядной шины адреса

б)

Рисунок 3.12 – Форматы команд простого микропроцессора

Таблица 3.1 – Система команд простого микропроцессора

|

Мнемокод |

Код |

Флажки |

Число |

Содержание | |||

|

байтов |

тактов |

циклов | |||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 | |

|

Команды пересылки | |||||||

|

MOV r1, r2 |

01ПППИИИ |

– |

1 |

4 |

1 |

Пересылка из регистра r2 в регистр r1 | |

|

MOV M, r |

01110ИИИ |

– |

1 |

7 |

2 |

Пересылка из регистра в память | |

|

MOV r, M |

01ППП110 |

– |

1 |

7 |

2 |

Пересылка из памяти в регистр | |

|

MVI r, b2 |

00ППП110 |

– |

2 |

7 |

2 |

Пересылка непосредственных данных в регистр | |

|

Продолжение таблицы 3.1

| |||||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 | |

|

Команды пересылки | |||||||

|

MVI M, b2 |

36 |

– |

2 |

10 |

3 |

Пересылка непосредственных данных в память | |

|

LXI rp,b3b2 |

00ПР0001 |

– |

3 |

10 |

3 |

Загрузка непосредственных данных в пару регистров | |

|

LDA b3b2 |

3A |

– |

3 |

13 |

4 |

Прямая загрузка аккумулятора | |

|

STA b3b2 |

32 |

– |

3 |

13 |

4 |

Прямая запись аккумулятора в память | |

|

LHLD b3b2 |

2A |

– |

3 |

16 |

5 |

Прямая загрузка пары регистров H | |

|

SHLD b3b2 |

22 |

– |

3 |

16 |

5 |

Прямая загрузка пары регистров H в память | |

|

LDAX rp |

00ПР1010 |

– |

1 |

7 |

2 |

Косвенная загрузка аккумулятора посредством пары регистров B или D | |

|

STAX rp |

00ПР0010 |

– |

1 |

7 |

2 |

Косвенная запись аккумулятора в память посредством пары регистров B или D | |

|

XCHG |

EB |

– |

1 |

4 |

1 |

Обмен между парами регистров H и D | |

|

Команды арифметических и логических операций | |||||||

|

ADD r |

10000ИИИ |

+ |

1 |

4 |

1 |

Сложение регистра и аккумулятора | |

|

ADD M |

86 |

+ |

1 |

7 |

2 |

Сложение памяти и аккумулятора | |

|

ADI b2 |

C6 |

+ |

2 |

7 |

2 |

Сложение непосредственных данных и аккумулятора | |

|

ADC r |

10001ИИИ |

+ |

1 |

4 |

1 |

Сложение регистра и аккумулятора с переносом | |

|

Продолжение таблицы 3.1

| |||||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 | |

|

Команды арифметических и логических операций | |||||||

|

ADC M |

8E |

+ |

1 |

7 |

2 |

Сложение памяти и аккумулятора с переносом | |

|

ACI b2 |

CE |

+ |

2 |

7 |

2 |

Сложение непосредственных данных и аккумулятора с переносом | |

|

SUB r |

10010ИИИ |

+ |

1 |

4 |

1 |

Вычитание регистра из аккумулятора | |

|

SUB M |

96 |

+ |

1 |

7 |

2 |

Вычитание памяти из аккумулятора | |

|

SUI b2 |

D6 |

+ |

2 |

7 |

2 |

Вычитание непосредственных данных из аккумулятора | |

|

SBB r |

10011ИИИ |

+ |

1 |

4 |

1 |

Вычитание регистра из аккумулятора с заемом | |

|

SBB M |

9E |

+ |

1 |

7 |

2 |

Вычитание памяти из аккумулятора с заемом | |

|

SBI b2 |

DE |

+ |

2 |

7 |

2 |

Вычитание непосредственных данных из аккумулятора с заемом | |

|

INR r |

00ППП100 |

(+) |

1 |

4 |

1 |

Инкремент регистра | |

|

INR M |

34 |

(+) |

1 |

10 |

3 |

Инкремент памяти | |

|

DCR r |

00ППП101 |

(+) |

1 |

4 |

1 |

Декремент регистра | |

|

DCR M |

35 |

(+) |

1 |

10 |

3 |

Декремент памяти | |

|

INX rp |

00ПР0011 |

– |

1 |

6 |

1 |

Инкремент пары регистров | |

|

DCX rp |

00ПР1011 |

– |

1 |

6 |

1 |

Декремент пары регистров | |

|

DAD rp |

00ПР1001 |

C |

1 |

10 |

3 |

Сложение регистровой пары H с регистровой парой | |

|

Продолжение таблицы 3.1

| |||||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 | |

|

Команды арифметических и логических операций | |||||||

|

DAA |

27 |

+ |

1 |

4 |

1 |

Преобразование аккумулятора в двоично-десятичный код | |

|

ANA r |

10100ИИИ |

+ |

1 |

4 |

1 |

Логическое И регистра и аккумулятора | |

|

ANA M |

A6 |

+ |

1 |

7 |

2 |

Логическое И памяти и аккумулятора | |

|

ANI b2 |

E6 |

+ |

2 |

7 |

2 |

Логическое И непосредственных данных и аккумулятора | |

|

XRA r |

10101ИИИ |

+ |

1 |

4 |

1 |

Исключающее ИЛИ регистра и аккумулятора | |

|

XRA M |

AE |

+ |

1 |

7 |

2 |

Исключающее ИЛИ памяти и аккумулятора | |

|

XRI b2 |

EE |

+ |

2 |

7 |

2 |

Исключающее ИЛИ непосредственных данных и аккумулятора | |

|

ORA r |

10110ИИИ |

+ |

1 |

4 |

1 |

Логическое ИЛИ регистра и аккумулятора | |

|

ORA M |

B6 |

+ |

1 |

7 |

2 |

Логическое ИЛИ памяти и аккумулятора | |

|

ORI b2 |

F6 |

+ |

2 |

7 |

2 |

Логическое ИЛИ непосредственных данных и аккумулятора | |

|

CMP r |

10111ИИИ |

+ |

1 |

4 |

1 |

Сравнение регистра и аккумулятора | |

|

CMP M |

BE |

+ |

1 |

7 |

2 |

Сравнение памяти и аккумулятора | |

|

Продолжение таблицы 3.1 | |||||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 | |

|

Команды арифметических и логических операций | |||||||

|

CPI b2 |

FE |

+ |

2 |

7 |

2 |

Сравнение непосредственных данных и аккумулятора | |

|

CMA |

2F |

– |

1 |

4 |

1 |

Инвертирование аккумулятора | |

|

STC |

37 |

C |

1 |

4 |

1 |

Установка флажка переноса | |

|

CMC |

3F |

C |

1 |

4 |

1 |

Инвертирование флажка переноса | |

|

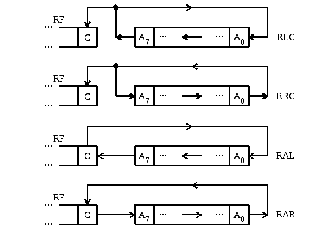

RLC |

07 |

C |

1 |

4 |

1 |

Циклический сдвиг аккумулятора влево | |

|

RRC |

0F |

C |

1 |

4 |

1 |

Циклический сдвиг аккумулятора вправо | |

|

RAL |

17 |

C |

1 |

4 |

1 |

Циклический сдвиг аккумулятора влево через разряд переноса | |

|

RAR |

1F |

C |

1 |

4 |

1 |

Циклический сдвиг аккумулятора вправо через разряд переноса | |

|

Команды управления | |||||||

|

JMP b3b2 |

C3 |

– |

3 |

10 |

3 |

Безусловный переход | |

|

Jусл b3b2 |

11УУУ010 |

– |

3 |

10 |

3 |

Условный переход | |

|

CALL b3b2 |

CD |

– |

3 |

18 |

5 |

Безусловный вызов подпрограммы | |

|

Cусл b3b2 |

11УУУ100 |

– |

3 |

11/18 |

3/5 |

Условный вызов подпрограммы | |

|

RET |

C9 |

– |

1 |

10 |

3 |

Возврат | |

|

Rусл |

11УУУ000 |

– |

1 |

5/11 |

1/3 |

Возврат при условии | |

|

RST n |

11nnn111 |

– |

1 |

11 |

3 |

Повторный запуск | |

|

SPHL |

F9 |

– |

1 |

6 |

1 |

Пересылка пары регистров H в SP | |

|

Окончание таблицы 3.1

| |||||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 | |

|

Специальные команды | |||||||

|

PUSH rp |

11РП0101 |

– |

1 |

11 |

3 |

Пересылка пары регистров в стек | |

|

PUSH PSW |

F5 |

– |

1 |

11 |

3 |

Пересылка аккумулятора и регистра флажков в стек | |

|

POP rp |

11РП0001 |

– |

1 |

10 |

3 |

Загрузка регистровой пары из стека | |

|

POP PSW |

F1 |

+ |

1 |

10 |

3 |

Загрузка аккумулятора и регистра флажков из стека | |

|

XTHL |

E3 |

– |

1 |

18 |

5 |

Обмен между регистровой парой H и стеком | |

|

PCHL |

E9 |

– |

1 |

5 |

1 |

Пересылка регистровой пары H в PC | |

|

IN port |

DB |

– |

2 |

10 |

3 |

Ввод | |

|

OUT port |

D3 |

– |

2 |

10 |

3 |

Вывод | |

|

EI |

FB |

– |

1 |

4 |

1 |

Разрешение прерывания | |

|

DI |

F3 |

– |

1 |

4 |

1 |

Запрещение прерывания | |

|

HLT |

76 |

– |

1 |

7 |

2 |

Останов | |

|

NOP |

00 |

– |

1 |

4 |

1 |

Нет операции | |

|

RIM |

20 |

– |

1 |

4 |

1 |

Чтение маски прерывания | |

|

SIM |

30 |

– |

1 |

4 |

1 |

Запись маски прерывания | |

Таблица 3.2 – Адреса регистров и регистровых пар микропроцессора

|

Регистры |

Пары регистров | ||||||||||

|

B |

C |

D |

E |

H |

L |

A |

B |

D |

H |

SP | |

|

000 |

001 |

010 |

011 |

100 |

101 |

111 |

00 |

01 |

10 |

11 | |

Таблица 3.3 – Коды условий для команд управления

|

УУУ |

Мнемокод |

Условия |

|

000 |

NZ |

Неравенство нулю |

|

001 |

Z |

Равенство нулю |

|

010 |

NC |

Отсутствие переноса |

|

011 |

C |

Наличие переноса |

|

100 |

PO |

Нечетность |

|

101 |

PE |

Четность |

|

110 |

P |

Плюс |

|

111 |

M |

Минус |

|

S |

Z |

0 |

AC |

0 |

P |

1 |

C |

|

бит 7 |

|

|

|

|

|

|

бит 0 |

Рисунок 3.13 – Формат регистра флажков

Рисунок 3.14 – Схемы, поясняющие выполнение сдвигов микропроцессором