- •Раздел 3 основы микропроцессорной техники

- •3.1 Структуры вычислительных систем

- •3.2 Принципы организации однокристальных микропроцессоров и микропроцессорных систем

- •3.3 Программирование микропроцессоров

- •При использовании прямой адресации

- •При использовании косвенной адресации

- •На языке Ассемблер

- •Ассемблер, содержащая подпрограмму

- •3.4 Принципы организации однокристальных микроконтроллеров

- •3.5 Программирование микроконтроллеров

- •3.6 Организация памяти микропроцессорных систем

- •3.7 Интерфейсные бис/ сбис

- •Информации

3.5 Программирование микроконтроллеров

Пример исходного файла на языке Ассемблер:

.LIST P=P33FJ32MC204

.INCLUDE "P33FJ32MC204.inc"

.GLOBAL __reset ;Метка начала кода

__reset:

main:

NOP

GOTO MAIN

service:

NOP

NOP

RETFIE

.END ;Конец кода

Таблица 3.10 – Синтаксис числовых значений

|

Тип |

Синтаксис |

Пример |

|

Шестнадцатеричный |

0x< числовое значение > |

#0x9F |

|

Десятичный |

<числовое значение> |

#123 |

|

Двоичный |

0b<числовое значение> |

#0b11 |

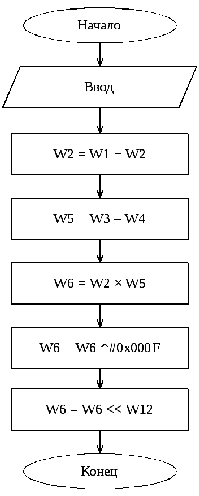

Рисунок 3.28 – Схема алгоритма к примеру 3.24

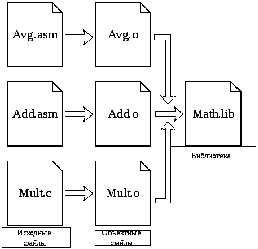

Рисунок 3.25 – Обобщенная схема процесса конструирования программы

Рисунок 3.26 – Создание файла библиотеки

3.6 Организация памяти микропроцессорных систем

Рисунок 3.31 – Типичные сигналы ЗУ

Рисунок

3.32 – Классификация полупроводниковых

ЗУ

Рисунок

3.32 – Классификация полупроводниковых

ЗУ

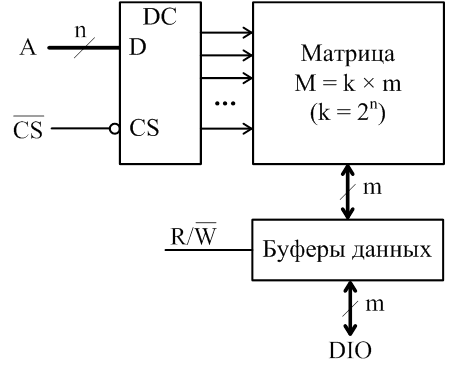

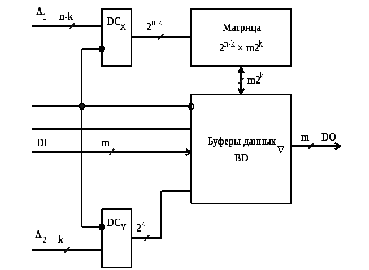

Рисунок 3.33 – Структура ОЗУ типа 2D

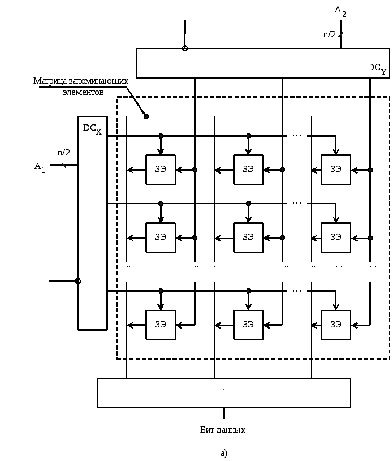

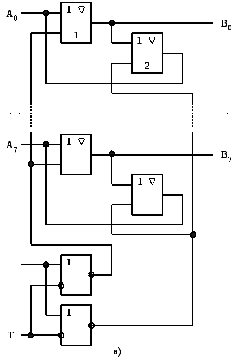

Рисунок 3.34 – Структура постоянного ЗУ типа 3Dс одноразрядной (а) и многоразрядной организациями (б)

Окончание рисунка 3.34

Рисунок 3.35 – Структура ЗУ типа 2DMдляROM

Рисунок 3.36 – Структура ЗУ типа 2DMдляRAM

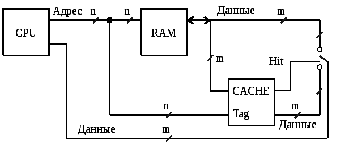

Рисунок 3.37 – Структура Кэш-памяти

Рисунок 3.38 – Структура полностью ассоциативной Кэш-памяти

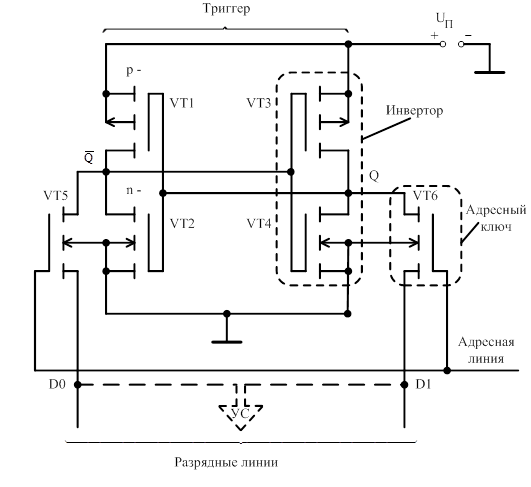

Рисунок 3.39 – Принципиальная электрическая схема ЗЭ на КМОП-транзисторах

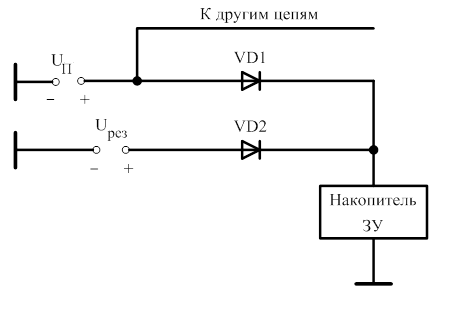

Рисунок 3.40 – Схема подключения резервного источника питания к накопителю ЗУ

Рисунок 3.41 – Принципиальная схема ЗЭ динамического ОЗУ

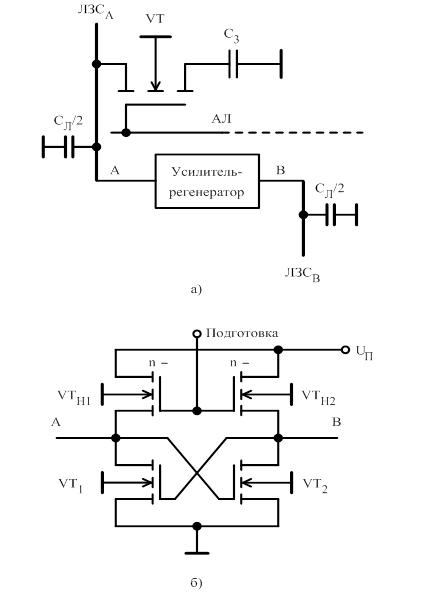

Рисунок 3.42 – Схема включения усилителя-регенератора в разрыв линии записи-считывания динамического ЗУ (а) и вариант схемной реализации усилителя-регенератора (б)

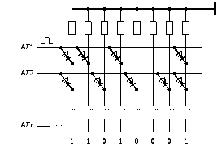

Рисунок 3.43 – Матрица диодных запоминающих элементов масочного ПЗУ

Рисунок 3.44 – Запоминающие элементы с плавкими перемычками (а) и диодными парами (б)

Рисунок 3.45 – Структуры транзисторов типов МНОП (а) и ЛИЗМОП с двойным затвором (б)

Рисунок 3.46 – Схема подключения ЛИЗМОП-транзисторов с двойным затвором к линиям выборки и считывания в РПЗУ

Рисунок 3.47 – Структура матрицы накопителя Флэш-памяти на основе ячеек ИЛИ-НЕ

3.7 Интерфейсные бис/ сбис

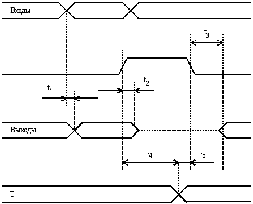

Рисунок 3.48 – Шинный формирователь КР580ВА86. Схема логическая (а) и временные диаграммы работы (б)

t1 – задержка распространения сигналов от входов к выходам;

t2 – задержка перехода выходов в Z-состояние;

t3 – задержка перехода выходов в активное состояние;

t4

и t5

– время выдержки и предустановки сигнала

T

относительно сигнала

.

.

б)

Окончание рисунка 3.48

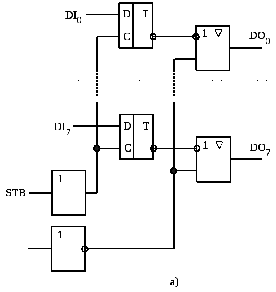

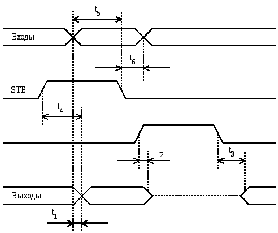

Рисунок 3.49 – Буферный регистр КР580ИР82. Схема логическая (а) и временные диаграммы работы (б)

t1 – задержка распространения сигналов от входов к выходам;

t2 – задержка перехода выходов в Z-состояние;

t3 – задержка перехода в активное состояние;

t4 – интервал от изменения строба до изменения выхода схемы;

t5

и t6

– времена предустановки и выдержки

входного сигнала относительно

спада строба ( ).

).

б)

Окончание рисунка 3.49

Таблица 3.11 – Адресация внутренних регистров ППА и направление передач

Информации

|

A1 |

A0 |

|

|

|

Операция |

|

0 |

0 |

0 |

1 |

0 |

Порт A → Системная ШД |

|

0 |

1 |

0 |

1 |

0 |

Порт B → Системная ШД |

|

1 |

0 |

0 |

1 |

0 |

Порт C → Системная ШД |

|

1 |

1 |

0 |

1 |

0 |

Запрещенная комбинация |

|

0 |

0 |

1 |

0 |

0 |

Системная ШД → Порт A |

|

0 |

1 |

1 |

0 |

0 |

Системная ШД → Порт B |

|

1 |

0 |

1 |

0 |

0 |

Системная ШД → Порт C |

|

1 |

1 |

1 |

0 |

0 |

Системная ШД → РУС при D7 = 1 |

|

|

|

|

|

|

Системная ШД → BSR при D7 = 0 |

|

X |

X |

1 |

1 |

0 |

Шины отключены (Z-состояние) |

|

X |

X |

X |

X |

1 |

Шины отключены (Z-состояние) |

|

Примечание – Знак «X» означает произвольный уровень сигнала (0 или 1) | |||||

Рисунок 3.50 – Параллельный периферийный адаптер. Схема электрическая структурная

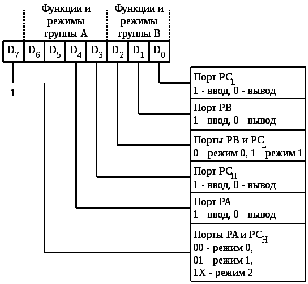

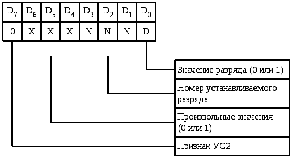

Рисунок 3.51 – Формат управляющего слова УС1 ППА

Рисунок 3.52 – Формат управляющего слова УС2 ППА