- •Структура и функционирование процессоров PowerPC

- •Рис. 1. Структура процессоров семейства PowerPC

- •Рис. 2. Регистровая модель пользователя процессоров PowerPC

- •Рис. 3. Форматы содержимого регистров CR, XER, FPSCR

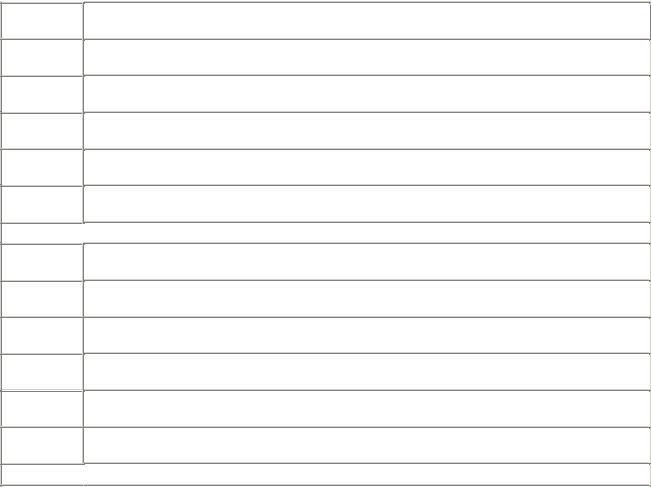

- •Таблица 1. Виды и относительные адреса векторов исключений

- •Способы адресации и система команд

- •Номенклатура и применение процессоров PowerPC

Таблица 1. Виды и относительные адреса векторов исключений

Адрес вектора Av

00100h

00200h

00300h

00400h

00500h

00600h

00700h

00900h

00C00h

00D00h

00F00h

01300h

0140h

Вид исключения

"Системный сброс" - установка в начальное состояние при поступлении внешних сигналов сброса SRESET#=0 или HRESET#=0

"Контроль процессора" - поступление сигналов ошибки пересылки TEA#=0 или контроля

процессора MCP#=0 (реализуется, если в MSR бит МЕ=1)

"Ошибка выбора данных" - ошибка при трансляции выбора данных; нарушение защиты при выборе данных; выборка операнда, адрес которого содержится в регистре DABR

"Ошибка выбора команды" - ошибка при трансляции адреса команды; нарушение защиты при выборе команды

"Внешнее прерывание" - поступление внешнего сигнала INT#=0 (разрешено, если в MSR бит ЕЕ=1)

"Нарушение выравнивания" - обращение к памяти по адресу, не кратному четырем

"Нарушение выравнивания" - обращение к памяти по адресу, не кратному четырем

"Программное исключение" - неправильный код команды; нарушение защиты; программное прерывание; прерывания при обработке чисел с плавающей точкой

"Периодическое прерывание" - изменение содержимого регистра декремента DEC с 00...0 не 11...1 (разрешено, если если в MSR бит ЕЕ=1)

"Системный вызов" - вызов подпрограммы обслуживания при поступлении команды системного вызова SC

"Исключение трассировки" - пошаговый режим с остановкой после каждой команды (если в MSR бит SE=1) или после команд ветвлений (если в MSR бит ВЕ=1)

"Исключение контроля эффективности" - переполнение регистров контроля эффективности PMC1 или PMC2

"Прерывание в контрольной точке" - выборка команды, адрес которой совпадает с содержимым регистра IABR

"Сиситемное прерывание" - поступление сигнала SMI#=0 (если в MSR бит ЕЕ=1)

"Сиситемное прерывание" - поступление сигнала SMI#=0 (если в MSR бит ЕЕ=1)

При исключениях типа “системный сброс”, “контроль процессора” в регистре SRR0 сохраняется ранее записанное содержимое. Поэтому после их обслуживания можно обеспечить переход к заданной команде, адрес которой предварительно заносится в SRR0. В регистре SRR1 при исключении “контроль процессора” отдельные биты указывают на поступление сигналов TEA#=0, MCP#=0, нарушение чётности при выборке команд или данных. Анализ содержимого SRR1 позволяет определить причину исключения. Если исключение “контроль процессора” замаскировано (в регистре MSR бит ME=0), то процессор останавливает свою работу, выдавая внешний сигнал контрольной остановки. При исключениях типа “ошибка выбора данных”, “нарушение выравнивания” в регистр DAR заносится код выполнявшейся команды, а в регистр DSISR — адрес операнда, выборка которого вызвала исключение.

Процессор имеет отдельные устройства управления памятью IMMU, DMMU и внутренние кэши для команд IC и данных DC (рис. 1). Емкость каждого кэша составляет 32 Кбайт. Устройства управления IMMU, DMMU обеспечивают блочную, сегментную и страничную организацию памяти.

Оба кэша организованы в виде группы из 256 наборов, каждый из которых содержит четыре 32-байт строки. В качестве тега используются 19 старших разрядов адреса. Cледующие 8 разрядов адреса определяют номер набора строк, в котором должны размещаться выбираемые данные или команда. Младшие 5 разрядов адресуют расположенные в строке байт, полуслово или слово. При кэш-промахе в выбранном наборе производится замещение пустой (недостоверной) строки или строки, к которой дольше всего не производилось обращение (метод замещения LRU — least-recently used). Каждая строка в кэше содержит 19-разрядный тег, восемь 32-разрядных слов (данные или команды) и биты, идентифицирующие текущее состояние строки.

Для строк кэша команд IC возможны два состояния: V (valid) — достоверное или I (invalid) — недостоверное содержимое строки. Недостоверное (незаполненное) состояние строк этого кэша устанавливается при сбросе процессора в начальное состояние (reset) путём загрузки

соответствующего содержимого в регистр конфигурации HID0 или c помощью команды аннулирования содержимого строки. При заполнении строки устанавливается достоверное состояние её содержимого.

Для кэша данных DC введено четыре возможных состояния строки, идентификация которых обеспечивает возможность совместного использования нескольких кэшей в мультипроцессорной системе:

M (modified) — содержимое строки модифицировано путём записи по соответствующему адресу, и новое содержимое не переписано в ОЗУ;

E (exclusive) — содержимое строки хранится только в этом кэше и ОЗУ;

S (shared) — содержимое строки хранится в данном кэше, ОЗУ и каком-либо другом устройстве (кэше);

I (invalid) — недостоверное (аннулированное) содержимое строки.

Для идентификации состояния строки служат соответствующие биты состояния. Для каждого состояния установлен определённый протокол обращения к содержимому строки. При этом реализуется снупинг — возможность обращения к содержимому кэша данных со стороны другого устройства (процессора в мультипроцессорной системе). Установленный протокол обращения (MESIпротокол) с применением снупинга обеспечивает соответствие данных, хранящихся в различных кэшах мультипроцессорной системы, что позволяет избежать ошибок из-за использования каким-либо из процессоров старых данных, которые были модифицированы другим процессором.

Обращение к кэшу команд IC производится устройством управления процессора (рис. 1), которое одновременно выбирает из строки четыре команды (16 байт). Обращение к кэшу данных выполняется блоком LSU, который одновременно выбирает два слова (8 байт). Оба кэша подключены к общей шине через блок интерфейса BIU, который обеспечивает пересылку двух слов (8 байт) в одном цикле. Пересылка содержимого кэшей в ОЗУ или в обратном направлении выполняется с помощью пакетного обмена, при котором реализуется четыре последовательных цикла для передачи содержимого строки

(32 байт).

Отдельные биты содержимого регистра конфигурации HID0 определяют режим использования кэшей. Установкой значения этих битов можно обеспечить включение или отключение каждого кэша, его блокировку, при которой кэш не используется, но его содержимое сохраняется, освобождение кэша путём аннулирования содержимого его строк (перевод в недостоверное состояние).

Обычно кэши работают в режиме обратной записи, который снижает нагрузку на общую шину, обеспечивая повышение производительности системы. Однако при обращении к отдельным блокам или страницам памяти возможна реализация сквозной записи.

Изменение содержимого отдельных строк кэша IC или DC осуществляется с помощью специальных команд, которые выбирают строку кэша, в которой размещаются команды или данные с заданным адресом. При выполнении операций со строками кэша данных учитывается их состояние — M, E, S или

I.

Например, одна из этих команд аннулирует содержимое выбранной строки кэша данных, устанавливая для неё состояние I. Если перед этим строка имела состояние M, то предварительно её содержимое переписывается в ОЗУ. Другая команда выполняет запись в память содержимого выбранной строки кэша данных, если она имеет состояние M.

Полная очистка (аннулирование содержимого всех строк) кэшей команд или данных реализуется путём записи соответствующего содержимого в регистр HID0, которая производится с помощью команды, выполняемой в режиме супервизора.

Устройства управления памятью IMMU, DMMU осуществляют трансляцию адреса при выборке команд и данных, обеспечивая возможность блочной, сегментной и страничной организации памяти. Работа IMMU, DMMU обеспечивается с помощью 8 пар регистров IBAT, DBAT, 16-сегментных регистров SR15-0 и регистра SDR1, обращение к которым выполняется только в режиме супервизора. Если в регистре управления MSR (рис. 5) биты IT, DT имеют значение “0”, то трансляция адреса не выполняется (IMMU, DMMU отключены), и сформированный процессором эффективный адрес поступает на выводы A0-31 в качестве физического адреса ячейки памяти или внешнего устройства.