- •Структура и функционирование процессоров PowerPC

- •Рис. 1. Структура процессоров семейства PowerPC

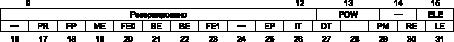

- •Рис. 2. Регистровая модель пользователя процессоров PowerPC

- •Рис. 3. Форматы содержимого регистров CR, XER, FPSCR

- •Таблица 1. Виды и относительные адреса векторов исключений

- •Способы адресации и система команд

- •Номенклатура и применение процессоров PowerPC

Включение IMMU, DMMU производится путём записи в регистр MSR содержимого, в котором соответствующий бит IT, DT имеет значение “1”. В этом случае сформированный адрес команды или данных воспринимается как логический адрес, который с помощью IMMU или DMMU транслируется в физический адрес, поступающий на внешние адресные выводы. При этом IMMU, DMMU реализуют следующие варианты адресной трансляции.

Блочная трансляция обеспечивает обращение к блокам внешней памяти заданного объёма — от 128 Кбайт до 256 Мбайт. Возможна организация четырёх блоков для хранения команд и четырёх — для хранения данных. Параметры каждого блока задаются дескриптором, который содержится в паре регистров IBATiU-IBATiL для команд, DBATiU-DBATiL для данных, где i = 0...3 — номер блока.

Сегментная и страничная трансляция обеспечивают обращение к сегментам памяти ёмкостью 256 Мбайт, которые разбиваются на страницы объёмом по 4 Кбайт, размещаемые в ОЗУ. Для обращения к сегментам используются 16 сегментных регистров SR15-0, которые содержат дескрипторы сегментов. Размещение в памяти отдельных страниц и их параметров определяются специальной таблицей дескрипторов, хранящейся в ОЗУ. При трансляции IMMU или DMMU производят обращение к таблице дескрипторов страниц для формирования необходимого физического адреса. Чтобы сократить потери времени, связанные с выполнением обращения к этой таблице, в составе IMMU и DMMU имеется специальная буферная память TLB, в которой хранятся дескрипторы 128 страниц, к которым производилось обращение в процессе выполнения предыдущих команд. Если при очередном обращении к памяти адресуется ранее использованная страница, то её параметры выбираются из TLB. Таким образом, значительно сокращаются потери времени, связанные со страничной трансляцией адреса, так как обращение к таблице дескрипторов производится только при выборке страницы, параметры которой отсутствуют в TLB.

Дескрипторы блоков, сегментов и страниц содержат биты, определяющие правила доступа к ним: разрешение обращения в режиме пользователя или супервизора, разрешение или запрещение записи или считывания их содержимого.

При нарушении этих правил реализуется исключение “ошибка выбора данных” (Av=00300h) или “ошибка выбора команды” (Av=00400h). Кроме битов доступа дескрипторы содержат ряд других параметров, например, биты, характеризующие “историю” страницы — выполнялось ли ранее обращение к данной странице, производилось ли изменение её содержимого (запись). Эти биты используются операционной системой для эффективной реализации виртуальной памяти, обеспечивающей оперативный обмен содержимым страниц между ОЗУ и внешней памятью большого объёма.

Способы адресации и система команд

Процессоры PowerPC используют следующие способы адресации:

регистровая; косвенно-регистровая со смещением;

косвенно-регистровая с индексированием; относительная; абсолютная; непосредственная.

Все команды арифметических и логических операций, сравнения и сдвигов выполняются только с регистровой и непосредственной адресацией. Благодаря этому обеспечивается высокая производительность, так как при обработке данных не требуется выполнять циклов обращения к шине для выбора операндов. Регистровая адресация позволяет использовать трёхадресный формат команд, при котором команда содержит номера трёх регистров (GPR или FPR): rA, rB, в которых хранятся операнды, и rD, в котором размещается полученный результат. Трёхадресные команды обеспечивают повышение производительности благодаря исключению лишних пересылок данных между регистрами. Один из операндов может непосредственно задаваться 32-разрядным словом, следующим за кодом команды.

Команды загрузки и сохранения содержимого регистров GPR или FPR используют при обращении к памяти косвенно-регистровую адресацию со смещением или индексированием. Эффективный адрес

операнда EA определяется выражениями:

EA = (rA ! 0) + d32 при адресации со смещением;

EA = (rA ! 0) + (rB) при адресации с индексированием,

где rA, rB — номера регистров общего назначения GPR31-1, d32 — 32-разрядное смещение. Регистр GPR0 не используется при этих способах адресации: если в качестве номера rA указан “0”, то формируется адрес EA=d32 при адресации со смещением, EA=(rB) — при адресации с индексированием. Так реализуется прямая (абсолютная) адресация с обращением по заданному в команде адресу d32 и косвенно-регистровая адресация по адресу, заданному содержимым регистра rB.

Команды ветвления используют прямую или относительную адресацию. Адресом перехода служит указанный в команде адрес t-adr или сумма (PC + t-adr).

Все команды процессора имеют 32-разрядный формат кода операции. При использовании непосредственной адресации после кода команды следует 32-разрядный операнд. В командах, использующих косвенно-регистровую адресацию со смещением, после кода операции следует 32разрядное смещение, а в командах ветвления — 32-разрядный адрес t-adr. Таким образом, все команды содержат 4 или 8 байт. Команды обработки целочисленных данных. Команды данной группы реализуют арифметические и логические операции, сравнение и сдвиг, используя целочисленные операнды, хранящиеся в регистрах GPR0-31 или содержащихся непосредственно в команде. Результат размещается в одном из регистров GPR.

Команды арифметических операций выполняют сложение, вычитание, умножение и деление операндов. Эти команды имеют ряд модификаций, отличающихся формированием признаков по результатам операций. Ряд модификаций обеспечивает установку соответствующих значений битов SO, EQ, GT, LT в поле CR0 регистра CR (рис. 3а). Имеются модификации команд, по результатам выполнения которых устанавливаются биты OV, SO в регистре XER (рис. 3б), при этом бит SO дублируется в поле CR0 регистра CR. Ряд команд сложения и вычитания вызывает установку признака переноса CA в регистре XER в соответствии с результатом операции. Команды умножения и деления могут оперировать с операндами без знака или со знаком. К этой же группе относятся команды, которые изменяют знак операнда или выполняют преобразование 8- и 16-разрядных операндов в 32разрядные слова путём расширения знаком.

Команды сравнения осуществляют вычитание двух операндов, которые могут быть числами со знаком или без знака. По результатам вычитания осуществляется установка признаков в поле CRi регистра CR, номер которого i = 7...2 задаётся в команде.

Команды логических операций производятся над 32-разрядными операндами без знака. Процессор реализует восемь логических операций: И, ИЛИ, Исключающее ИЛИ, НЕ-И, НЕ-ИЛИ, Запрет, Импликация, Эквивалентность, — над операндами, хранящимися в регистрах GPR. Если один из операндов задан непосредственно в команде, то возможно выполнение операций И, ИЛИ, Исключающее ИЛИ. Одна из команд этой группы позволяет определить номер первого значащего разряда в операнде.

Команды сдвигов реализуют многоразрядные логические, арифметические и циклические сдвиги содержимого одного из регистров GPR с размещением результата в другом регистре. Число разрядов сдвига определяется содержимым указанного регистра или задаётся непосредственно в команде.

Команды логических операций и сдвигов имеют модификации, которые вызывают установку признаков в поле CR0 регистра CR в соответствии с результатом операции.

Команды обработки чисел с плавающей точкой. Операции над числами с плавающей точкой выполняются с использованием 64-разрядных регистров FPR31-0 и регистра управления и состояния FPSCR, входящих в регистровую модель пользователя (рис. 2). Обрабатываемые числа представляются в формате одинарной (ОТ, 32 разряда) или двойной (ДТ, 64 разряда) точности в соответствии со стандартом IEEE 754. Данные форматы обеспечивают также представление бесконечности и Не-чисел (NAN).

Команды арифметических операций сложения, вычитания, умножения, деления, вычисления квадратного корня, обратной величины и обратной величины от квадратного корня выполняются с операндами, располагаемыми в регистрах FPR, номера которых задаются в команде. Блок FPU реализует также комбинированные операции умножение-сложение, умножение-вычитание и аналогичные операции с изменением знака результата. Эти операции производятся над вещественными числами в формате ОТ или ДТ, кроме операций вычисления обратных величин, которые выполняются только с числами двойной точности.

При операциях сравнения производится сравнение содержимого указанных в команде регистров FPR и установка соответствующих признаков в заданном поле CRi регистра условий CR (рис. 3а).

Команды преобразования форматов преобразуют число ДТ, хранящееся в одном из регистров FPR, в число ОТ или целое 32-разрядное число со знаком, загружаемое в другой регистр FPR. В случае необходимости при этом выполняется округление в соответствии со значением поля RN в регистре

FPSCR.

Команды пересылки производят передачу содержимого из одного регистра FPR в другой. При этом возможно изменение знака операнда, установка отрицательного знака, пересылка абсолютного значения.

Специальные команды служат для пересылки и изменения содержимого регистра FPSCR. Эти команды выполняют пересылку содержимого FPSCR в заданный регистр FPR, пересылку 4-бит поля, номер которого указывается в команде, из регистра FPSCR в поле CRi регистра условий CR, загрузку 4-бит непосредственного операнда в заданное поле регистра FPSCR, запись в FPSCR старшего 32разрядного слова из регистра FPR, логически умноженного на заданную в команде 32-бит маску, установку в “0” или “1” заданных битов в регистре FPSCR.

Большинство рассмотренных команд может изменять содержимое поля CR1 в регистре условий CR, перенося в него значения признаков FX, FEX, VX, OX, устанавливаемых в регистре FPSCR.

Команды загрузки и сохранения содержимого регистров GPR, FPR. Команды этой группы производят за-грузку в заданный регистр GPR байта, слова или полуслова (16-разрядное слово) из памяти, либо записывают в память байт, слово или полуслово из регистра. Для обращения к памяти используется косвенно-регистровая адресация со смещением или индексированием. При загрузке в регистр байта или полуслова старшие разряды регистра GPR заполняются “0” (расширение нулями) или значением старшего (знакового) бита загружаемого слова (расширение знаком). Ряд команд этой группы осуществляют перестановку байтов при загрузке в регистр полуслова или слова, либо при их записи из регистра в память.

Команды групповой пересылки производят загрузку или запись в память содержимого группы регистров, начиная с заданного в команде номера и до последнего регистра с номером GPR31. Загружаемые или записываемые данные располагаются в ячейках памяти, начиная с заданного командой адреса EA.

Команды пересылки строк символов осуществляют загрузку в регистры или запись в память n символов (байтов), число которых задается данным в команде операндом или содержимым 8 старших битов (поле SS, рис. 3б) в регистре XER. Начальный адрес пересылаемых байтов EA определяется выбранным способом адресации.

Команды загрузки и сохранения чисел с плавающей точкой производят загрузку из памяти в заданный регистр FPR вещественного числа в формате ОТ или ДТ, либо записывают в память число в формате ОТ или ДТ из регистра FPR.

Команды загрузки-сохранения имеют модификации, которые после выполнения пересылки загружают в адресный регистр rA эффективный адрес EA, использованный в данной команде. Эти модификации позволяют, например, реализовать постинкрементную адресацию байтов, полуслов или слов, если задать в соответствующих командах значения смещения d32 = 1, 2 или 4.

Команды управления программой осуществляют безусловные и условные ветвления, реализуют программные прерывания и возврат из прерывания. При ветвлениях адрес команды перехода

определяется с помощью прямой или относительной адресации. Заданное в команде число t-adr служит при этом абсолютным адресом или смещением, определяющим адрес перехода.

Команды условных ветвлений используют в качестве условия совпадение содержимого указанного в команде поля CRi в регистре условий CR с четырьмя младшими битами заданного в команде операнда BO. При совпадении заданного значения BO и содержимого поля CRi производится переход к команде, адрес которой определяется с помощью абсолютной или относительной адресации. При несовпадении выполняется следующая команда программы. Команды bcl, bcla, сохраняющие в регистре LR адрес следующей команды, служат для реализации условных вызовов подпрограммы.

Команды ветвления имеют модификации, при выполнении которых текущее содержимое программного счётчика PC заносится в регистр связи LR, обеспечивая возможность возвращения к следующей команде программы. Таким образом, эти команды могут служить для вызова подпрограмм. Команды условного возврата из подпрограммы загружают в программный счётчик PC содержимое регистра связи LR, если заданное в команде значение операнда BO совпадает с содержимым указанного поля CRi.

При условных ветвлениях программист может указать на повышенную вероятность ветвления, задав значение “1” для пятого бита операнда BO. В этом случае блок обработки ветвления BPU обеспечит выборку в конвейер следующих команд в соответствии с данным предсказанием. Такой способ предсказания ветвлений называется статическим. При нулевом значении пятого бита в операнде BO блок BPU осуществляет динамическое предсказание ветвлений с помощью кэша адресов BTAC и таблицы истории ветвлений BHT (см. предыдущий раздел).

Команды программных прерываний производят условное обращение к подпрограмме обслуживания, вектор которой Ve размещён по адресу Av=$00700 (табл. 1). Текущее содержимое PC и MSR сохраняется в регистрах SRR0, SRR1. Условием обращения является совпадение признаков, устанавливаемых в поле CR0 при сравнении содержимого указанных в команде регистров или регистра с непосредственным операндом, с битами заданного в команде 4-разрядного операнда TO. Прерывание реализуется, если хотя бы один из установленных в “1” признаков в CR0 совпадает с соответствующим битом TO.

Специальная команда осуществляет вызов системного прерывания с подпрограммой обслуживания, вектор которой Ve размещён по адресу Av=$00C00 (табл. 1). Команда возврата из прерывания восстанавливает содержимое программного счётчика PC и регистра управления MSR из регистров SRR0, SRR1, обеспечивая возвращение к выполнению прерванной программы. При выполнении команд условных переходов используется содержимое различных полей регистра условий CR.

Специальные команды реализуют различные операции с содержимым этого регистра. Эти команды производят загрузку в CR содержимого регистра GPR, которое логически умножается на заданную в команде 32-бит маску, пересылку содержимого CR в заданный регистр GPR, копирование четырёх младших битов из регистра исключений XER (признаки SO, OV, CA, рис. 3а) в поле CRi регистра CR, перенос содержимого поля CRi в поле CRj регистра CR. Ряд команд выполняет логи-ческие операции И, ИЛИ, Исключающее ИЛИ, НЕ-И, НЕ-ИЛИ, Эквивалентность, Запрет, Импликация над отдельными битами содержимого регистра CR.

Служебные команды. В группу служебных команд входят команды пересылки содержимого регистров XER, LR, CTR и служебных регистров, входящих в регистровую модель супервизора (рис. 5). Большинство этих команд выполняется процессором только в режиме супервизора.

Рис. 5. Формат содержимого регистра управления процессора MSR

К этой группе относятся также команды, обеспечивающие изменение содержимого отдельных строк кэш-памяти, синхронизацию выполнения программ несколькими совместно работающими процессорами, обращение процессора к выделенным ресурсам системы (специализированным