Лекции / Схемотехника ЭВМ. Лекция 12. Мультиплексоры

.pdf

Глава 4. Мультиплексоры

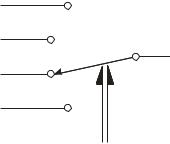

D0

D1

y

D2 |

|

D3 |

φ |

|

Рис.4.1. Электромеханическая модель од-

нобитного |

мультиплексора |

MS 4→1: |

D0...D3 - входные однобитовые |

данные; |

|

φ - угол поворота как адрес входного направления, данные с которого должны быть переданы на выход y

Однобитовым мультиплексором называется цифровой комбинационный узел, осуществляющий адресную передачу данных из одного из многих входов в один выход. Простейшим примером такого мультиплексора является поворотный переключатель, например на четыре входных направления (рис.4.1). Для передачи n-разрядного слова необходимо использовать n однобитовых мультиплексоров (n поворотных переключателей на общей механической оси).

4.1.Уравнения и структуры

Вцифровых устройствах мультиплексор реализуется как логический узел, в котором адрес задается двоичным кодом. При N входных направлениях требуется k адресных переменных, где k - ближайшее

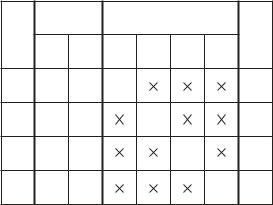

большее целое от log2N. Рассмотрим логическую структуру мультиплексора, аналогичного приведённому на рис.4.1. На основании определения составим таблицу истинности, описывающую его работу

(табл.4.1).

Очевидно, что в данном случае разрядность адреса входного на-

правления k = 2. Обозначим адресные переменные как a1 и a0. Примем, что индекс у входного направления совпадает с номером набора адресных переменных. Крестиком в таблице обозначены безразличные значения данных на входных направлениях. Итак, адрес с набором 0 пере-

дает на выход входные данные D0, а что подаётся на входы D1, D2 и D3 при этом адресе не имеет ни какого значения; адрес с набором 1 передает на выход входные данные D1 и т.д.

Из табл.4.1 получается следующее выражение для выхода y мультиплексора MS 4→1:

y =a1a0D0 +a1a0D1 +a1a0D2 +a1a0D3 . |

(4.1) |

Таблица 4.1

Таблица истинности однобитного мультиплексора MS 4→1

Номер |

Код адреса |

|

Входные данные |

|

y |

||

|

|

|

|

||||

набора |

a1 |

a0 |

D0 |

D1 |

D2 |

D3 |

|

|

|

||||||

0 |

0 |

0 |

D0 |

|

|

|

D0 |

1 |

0 |

1 |

|

D1 |

|

|

D1 |

2 |

1 |

0 |

|

|

D2 |

|

D2 |

3 |

1 |

1 |

|

|

|

D3 |

D3 |

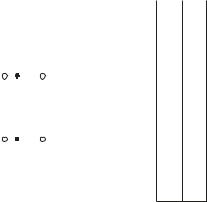

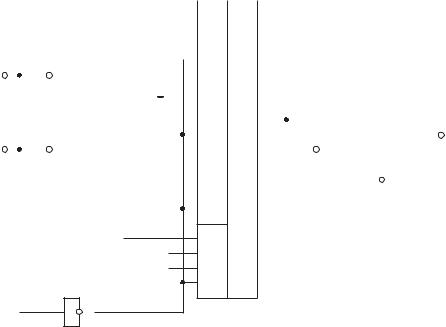

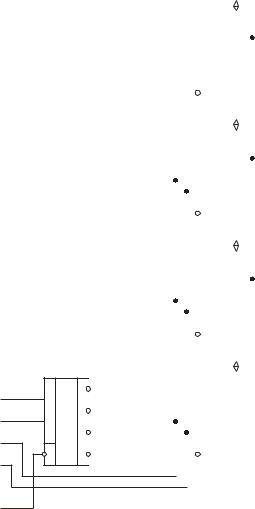

B справедливости этого выражения можно убедиться, подставляя в него различные наборы адресных переменных. Из уравнения (4.1) следует, что для реализации мультиплексора MS 4→1 необходимо использовать четыре трёхвходовых элемента И и один четырёхвходовый элемент ИЛИ. Следует обратить внимание, что адресные переменные образуют все конституенты единицы, поэтому из соображений обеспечения единичной нагрузки по входам a1 и a0 в схему дополнительно вводятся четыре буферных инвертора. Окончательная схема MS 4→1 приведена на рис.4.2,а, а его функциональное обозначение на рис.4.2,б.

Рассмотрим первый вариант построения мультиплексора с большим числом информационных входов на базе полученной структуры. Пусть требуется реализовать MS 16→1. Запишем уравнение для этого мультиплексора в виде матрицы из четырёх строк и четырёх столбцов (разрядность адреса k для MS 16→1 равна четырем):

y = a3a2a1a0 D0 +a3a2a1a0 D1 +a3a2a1a0 D2 +a3a2a1a0 D3 +

+a3a2a1a0D4 +a3a2a1a0D5 +a3a2a1a0D6 +a3a2a1a0D7 + |

(4.2) |

+a3a2a1a0 D8 + a3a2a1a0 D9 +a3a2a1a0 D10 +a3a2a1a0 D11 +

+a3a2a1a0 D12 + a3a2a1a0 D13 + a3a2a1a0 D14 + a3a2a1a0 D15 .

|

|

|

|

|

|

|

|

|

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

1 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a1 |

D1 |

|

|

|

|

|

|

|

D0 |

MS |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

a1 |

|

|

|

|

|

a1 |

|

|

|

& |

|

|

|

|

|

D1 |

|

|

|

||||

|

1 |

|

|

1 |

|

|

|

1 |

|

|

|

|

|

|

|

D2 |

|

|

|

||||

|

|

|

|

|

a |

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

D2 |

a0 |

|

|

|

|

y |

|

|

D3 |

|

y |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

a |

0 |

|

|

|

& |

|

|

|

|

|

a1 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

a0 |

|

|

|

|

|

a0 |

|

|

a1 |

|

|

|

|

|

|

|

a0 |

|

|

|

|||

|

1 |

|

|

1 |

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

D3 |

|

|

|

|

|

|

|

б |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

а

Рис.4.2. Однобитный мультиплексор MS 4→1: а - структура; б - функциональное обозначение

Отметим, что в выражении (4.2) имеют единое представление в каждой строке две старшие адресные переменные, а в каждом столбце - две младшие. Вынесем за скобки в каждой строке две старшие адресные переменные, тогда получим

y = a3a2 (a1a0D0 +a1a0D1 +a1a0D2 +a1a0D3) + |

|

+a3a2 (a1a0D4 +a1a0D5 +a1a0D6 +a1a0D7 ) + |

(4.3) |

+a3a2 (a1a0D8 +a1a0D9 +a1a0D10 +a1a0D11) +

+a3a2 (a1a0D12 +a1a0D13 +a1a0D14 +a1a0D15 ) .

B выражении (4.3) в скобках записаны уравнения четырёх MS 4→1 с общим адресом, представленным двумя младшими адресными переменными. Обозначим выходы этих мультиплексоров соответственно D0/, D1/, D2/, D3/, тогда уравнение (4.3) можно записать как

y = a3a2D0/ +a3a2D1/ +a3a2D2/ +a3a2D3/ ,

т.е. опять получили уравнение MS 4→1, следовательно, всего потребуется пять MS 4→1 .

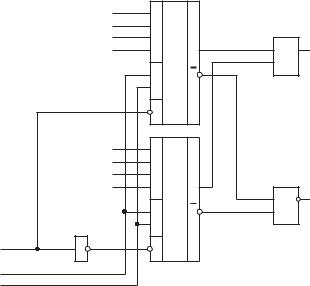

Окончательная схема MS 16→1, построенная на пяти MS 4→1, приведена на рис.4.3. Полученную схему называют мультиплексным

деревом, или многоярусным мультиплексором. Ясно, что эту структу-

ру можно реализовать для любого числа входов, однако она имеет очевидный недостаток - существенное возрастание задержек распространения сигналов в последовательно включенных ярусах мультиплексоров.

Рассмотрим второй вариант увеличения числа информационных входов мультиплексора. Пусть требуется реализовать MS 8→1. Запишем его уравнения в виде двух строк (здесь разрядность адреса равна трём):

y = a2a1aD0 +a2a1a0D1 +a2a1a0D2 +a2a1a0D3 +

+a2a1a0D4 +a2a1a0D5 +a2a1a0D6 +a2a1a0D7 . |

(4.4) |

В выражении (4.4) в первой строке адресная переменная а2 встречается только с инверсией, а во второй - без инверсии. Вынося за скобки

переменную a2 в первой строке и а2 во второй, получаем

y = a2 (a1a0D +a1a0D1 +a1a0D2 +a1a0D3 ) + |

|

+a2 (a1a0D4 +a1a0D5 +a1a0D6 +a1a0D7 ) . |

(4.5) |

В выражении (4.5) в скобках записаны уравнения двух мультиплексоров MS 4→1 с общим адресом, представленным двумя младшими

переменными. Будем рассматривать a2 в первой строке и а2 во второй

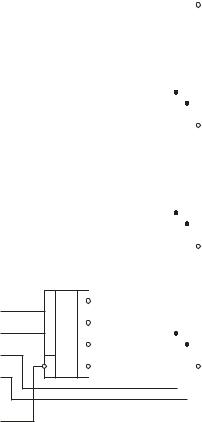

как стробирующие входы для этих мультиплексоров. Тогда уравнение стробируемого MS 4→1 с активным нулём на стробирующем входе v (valve - клапан, вентиль) будет иметь вид

y =v(a1a0D0 +a1a0D1 +a1a0D2 +a1a0D3 ) .

Структура такого мультиплексора приведена на рис.4.4,а, а его функциональное обозначение - на рис.4.4,б. На рисунке приведена реализация мультиплексора и с прямым и с инверсным выходами, что позволит показать различные варианты построения MS 4→1. Если адресную переменную а2 подать непосредственно на вход v первого стробируемого мультиплексора MS 4→1, то реализуется первая часть выражения (4.5), а если её подать через внешний дополнительный инвертор на вход второго стробируемого мультиплексора MS 4→1, то реализуется вторая часть выражения (4.5).

Представим уравнение (4.5) в виде

y = y/ + y// = y/ y// .

D0 D1

D2 D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

a3 a2

a1 a0

|

|

|

D0 |

MS |

|

|

|

|

|

||

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

y |

|

|

|

|

||

|

|

|

D3 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

MS |

|

|

|

|

|

||

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

y |

|

|

|

|

||

|

|

|

D3 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

MS |

|

|

|

|

|

||

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

y |

|

|

|

|

||

|

|

|

D3 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

MS |

|

|

|

|

|

||

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

y |

|

|

|

|

||

|

|

|

D3 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0

D1

D2

D3

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

MS |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

y |

|

y |

|

|

|

|

|

|

|||

|

|

|

|

D3 |

|

|

||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.4.3. Мультиплексор MS 16→1 на основе пяти мультиплексоров

MS 4→1 (мультиплексное дерево)

|

|

|

|

|

|

|

|

|

|

D0 |

|

& 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

a1 |

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

D0 |

MS |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

1 |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

D1 |

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D3 |

|

|

||||

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

y |

|

|

||||||||||||

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y |

|

|

|

a0 |

1 |

|

|

1 |

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

y |

a0 |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

D2 |

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

a |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

D3 &

a1 a0

V 1

а

Рис.4.4. Стробируемый мультиплексор MS 4→1: а - структура; б - функциональное обозначение

Видно, что для окончательной реализации MS 8→1на стробируемых MS 4→1 потребуется: два MS 4→1, инвертор и либо двухвходовый элемент ИЛИ, если у мультиплексоров MS 4→1 реализован прямой выход, либо двухвходовый элемент И-НЕ, если у мультиплексоров MS 4→1 реализован инверсный выход. Обобщённая схема реализации приведена на рис.4.5.

Такой вариант наращивания обеспечивает меньшие задержки распространения сигналов по сравнению с мультиплексным деревом. На рис.4.6 представлена схема MS 16→1, построенная на четырёх стробируемых MS 4→1 и одном стробируемом дешифраторе «1 из 4-х», где вход v дешифратора выполняет функции стробирующего входа всего MS 16→1. Ясно, что и эту структуру можно реализовать для любого числа входов.

|

D0 |

D0 |

MS |

|

|

|

D1 |

D1 |

|

|

|

|

D2 |

D2 |

y |

1 |

y |

|

D3 |

D3 |

|||

|

|

a1 |

y |

|

|

|

|

a0 |

|

|

|

|

|

V |

|

|

|

|

D4 |

D0 |

MS |

|

|

|

D5 |

D1 |

|

|

|

|

D6 |

D2 |

y |

|

|

|

D7 |

D3 |

& |

y |

|

|

|

a1 |

y |

||

|

|

|

|

||

|

|

a0 |

|

|

|

a2 |

1 |

V |

|

|

|

a1 |

|

|

|

|

|

a0 |

|

|

|

|

|

Рис.4.5. Мультиплексор MS 8→1 на основе двух стробируемых муль-

типлексоров MS 4→1

a3

a2

a1

a0

DC y0

2 y1

1 y2

V y3

|

|

|

D0 |

|

|

|

D0 |

MS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

D1 |

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

D2 |

|

|

|

D2 |

|

y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

D3 |

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D4 |

|

|

|

D0 |

MS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

D5 |

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

D6 |

|

|

|

D2 |

|

y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

D7 |

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

1 |

|

y |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D8 |

|

|

|

D0 |

MS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

D9 |

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

D10 |

|

|

|

D2 |

|

y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

D11 |

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D12 |

|

|

|

D0 |

MS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

D13 |

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

D14 |

|

|

|

D2 |

|

y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

D15 |

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V

Рис.4.6. Мультиплексор MS 16→1 на основе четырёх стробируемых муль-

типлексоров MS 4→1 и дешифратор «1 из 4-х»

Третий вариант увеличения числа информационных входов реализуется наиболее просто при использовании мультиплексоров, выходная цепь которых реализована с тремя состояниями выхода (см. модель такого выхода в главе 1). В этом случае выходы всех мультиплексоров просто соединяются в одну цепь, причём в каждый момент времени активным будет являться выход только одного выбранного мультиплексора, т.е. того, на входе v которого действует активный сигнал. На рис.4.7 показана схема MS 16→1, построенная на четырёх MS 4→1 с тремя состояниями выхода, активное значение у стробирующего входа которых равно 0, и одном стробируемом дешифраторе «1 из 4-х», причём вход v дешифратора выполняет функции стробирующего входа всего

MS 16→1.

Если мультиплексор кроме однобитовых данных может осуществлять передачу на свой выход констант и логических функций от вход-

ных данных, то он называется функциональным мультиплексором [8].

Примером может служить интегральная схема К561ЛС2 (CD4019A), структура которой приведена на рис.4.8.

Если обеспечить а1 = a0 , то данная схема будет выполнять функ-

ции счётверенного мультиплексора MS 2→1. Однако если рассматривать а1а0 как двухразрядный адрес, то для i-го выхода можно записать следующее выражение:

yi = a1a0 0 +a1a0 D1i +a1a0 D2i +a1a0 (D1i + D2i ),

что в ряде применений обеспечивает большие возможности в различных схемотехнических решениях.

a3

a2

a1

a0

DC y0

2 y1

1 y2

V y3

|

|

|

D0 |

|

|

|

D0 |

MS |

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

D1 |

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

D2 |

|

|

|

D2 |

|

y |

|

y |

|

|

|

|

|

|

||||||||

|

|

|

D3 |

|

|

|

D3 |

|

|

|

||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D4 |

|

|

|

D0 |

MS |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

D5 |

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

D6 |

|

|

|

D2 |

|

y |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

D7 |

|

|

|

D3 |

|

|

|

||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D8 |

|

|

|

D0 |

MS |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

D9 |

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

D10 |

|

|

|

D2 |

|

|

y |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

D11 |

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

D12 |

|

|

|

D0 |

MS |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

D13 |

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

D14 |

|

|

|

D2 |

|

|

y |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

D15 |

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V

Рис.4.7. Мультиплексор MS 16→1 на основе четырёх стробируемых муль-

типлексоров MS 16→1 с тремя состояниями выхода и дешифратора «1 из 4-х»